官网

https://developer.arm.com/architectures/system-architectures/amba/specifications

AMBA总线是ARM研发的(Advanced Microcontroller Bus Architecture)提供的一种特殊的机制,可以将RISC处理器集成在其他IP芯核和外设中,它是有效连接IP核的“数字胶”,并且是ARM复用策略的重要组件。

AMBA总线协议

关于AMBA总线协议AHB、APB、AXI对比分析

查看《AXI协议详解-AMBA总线协议AHB、APB、AXI对比分析》

https://github.com/adki/AMBA_AXI_AHB_APB (AMBA AXI/AHB/APB讲座资料)

alexforencich项目

这个项目真的不想过多介绍了,在《优秀的 Verilog/FPGA开源项目介绍(一)-PCIe通信》和《优秀的 Verilog/FPGA开源项目介绍(四)- Ethernet》中,这个项目都是主力担当。

https://github.com/alexforencich/verilog-axis

介绍

AXI Stream 总线组件的集合。大多数组件的宽度都是可以修改的。

项目包括使用cocotbext-axi 的完整 cocotb 测试平台。

模块介绍

arbiter 模块

通用参数化仲裁器。支持优先级和循环仲裁。支持阻塞直到请求释放或确认。

axis_adapter 模块

该axis_adapter模块桥接不同宽度的 AXI 流总线。该模块是可参数化的,但有一定的限制。首先,总线字宽必须相同(例如,一个 8 位通道和八个 8 位通道,但不是一个 16 位通道和一个 32 位通道)。其次,总线宽度必须是整数倍(例如2字和6字,而不是4字和6字)。必要时,将在更宽的总线侧插入等待状态。

axis_arb_mux 模块

具有可参数化数据宽度和端口数的帧感知 AXI 流仲裁多路复用器。支持优先级和循环仲裁。

axis_async_fifo 模块

可配置的基于字或基于帧的异步 FIFO,具有可参数化的数据宽度、深度、类型和坏帧检测。

axis_async_fifo_adapter 模块

可配置的基于字或基于帧的异步 FIFO,具有可参数化的数据宽度、深度、类型和坏帧检测。支持不同的输入和输出数据宽度,适当地插入一个axis_adapter实例。

axis_broadcast 模块

AXI 流广播器。

...

...

常见信号

tdata : Data (width generally DATA_WIDTH)

tkeep : Data word valid (width generally KEEP_WIDTH)

tvalid : Data valid

tready : Sink ready

tlast : End-of-frame

tid : Identifier tag (width generally ID_WIDTH)

tdest : Destination tag (width generally DEST_WIDTH)

tuser : User sideband signals (width generally USER_WIDTH)常用参数

DATA_WIDTH : width of tdata signal

KEEP_ENABLE : enable tkeep signal (default DATA_WIDTH>8)

KEEP_WIDTH : width of tkeep signal (default DATA_WIDTH/8)

LAST_ENABLE : enable tlast signal

ID_ENABLE : enable tid signal

ID_WIDTH : width of tid signal

DEST_ENABLE : enable tdest signal

DEST_WIDTH : width of tdest signal

USER_ENABLE : enable tuser signal

USER_WIDTH : width of tuser signal

USER_BAD_FRAME_VALUE : value of tuser indicating bad frame

USER_BAD_FRAME_MASK : bitmask for tuser bad frame indication源文件

arbiter.v : General-purpose parametrizable arbiter

axis_adapter.v : Parametrizable bus width adapter

axis_arb_mux.v : Parametrizable arbitrated multiplexer

axis_async_fifo.v : Parametrizable asynchronous FIFO

axis_async_fifo_adapter.v : FIFO/width adapter wrapper

axis_broadcast.v : AXI stream broadcaster

axis_cobs_decode.v : COBS decoder

axis_cobs_encode.v : COBS encoder

axis_crosspoint.v : Parametrizable crosspoint switch

axis_demux.v : Parametrizable demultiplexer

axis_fifo.v : Parametrizable synchronous FIFO

axis_fifo_adapter.v : FIFO/width adapter wrapper

axis_frame_join.v : Parametrizable frame joiner

axis_frame_length_adjust.v : Frame length adjuster

axis_frame_length_adjust_fifo.v : Frame length adjuster with FIFO

axis_ll_bridge.v : AXI stream to LocalLink bridge

axis_mux.v : Multiplexer generator

axis_pipeline_fifo.v : AXI stream register pipeline with FIFO

axis_pipeline_register.v : AXI stream register pipeline

axis_ram_switch.v : AXI stream RAM switch

axis_rate_limit.v : Fractional rate limiter

axis_register.v : AXI Stream register

axis_srl_fifo.v : SRL-based FIFO

axis_srl_register.v : SRL-based register

axis_switch.v : Parametrizable AXI stream switch

axis_stat_counter.v : Statistics counter

axis_tap.v : AXI stream tap

ll_axis_bridge.v : LocalLink to AXI stream bridge

priority_encoder.v : Parametrizable priority encoderAXI 流接口示例

两个字节传输,每个字节后有暂停

__ __ __ __ __ __ __ __ __

clk __/ \__/ \__/ \__/ \__/ \__/ \__/ \__/ \__/ \__

_____ _________________

tdata XXXXXXXXX_D0__X_D1______________XXXXXXXXXXXXXXXXXXXXXXXX

_____ _________________

tkeep XXXXXXXXX_K0__X_K1______________XXXXXXXXXXXXXXXXXXXXXXXX

_______________________

tvalid ________/ \_______________________

______________ _____ ___________

tready \___________/ \___________/

_________________

tlast ______________/ \_______________________

tuser ________________________________________________________两个背靠背数据包,没有暂停

__ __ __ __ __ __ __ __ __

clk __/ \__/ \__/ \__/ \__/ \__/ \__/ \__/ \__/ \__

_____ _____ _____ _____ _____ _____

tdata XXXXXXXXX_A0__X_A1__X_A2__X_B0__X_B1__X_B2__XXXXXXXXXXXX

_____ _____ _____ _____ _____ _____

tkeep XXXXXXXXX_K0__X_K1__X_K2__X_K0__X_K1__X_K2__XXXXXXXXXXXX

___________________________________

tvalid ________/ \___________

________________________________________________________

tready

_____ _____

tlast ____________________/ \___________/ \___________

tuser ________________________________________________________坏帧

__ __ __ __ __ __

clk __/ \__/ \__/ \__/ \__/ \__/ \__

_____ _____ _____

tdata XXXXXXXXX_A0__X_A1__X_A2__XXXXXXXXXXXX

_____ _____ _____

tkeep XXXXXXXXX_K0__X_K1__X_K2__XXXXXXXXXXXX

_________________

tvalid ________/ \___________

______________________________________

tready

_____

tlast ____________________/ \___________

_____

tuser ____________________/ \___________

pulp-platform中axi

https://github.com/pulp-platform/axi

介绍

这个是PULP中使用的axi总线,该项目已经流片经过验证。

PULP(并行超低功耗)是一个开源多核计算平台,是苏黎世联邦理工学院与博洛尼亚大学之间持续合作的项目。

PULP 架构针对需要灵活处理由多个传感器生成的数据流的物联网终端节点应用,例如加速度计、低分辨率摄像头、麦克风阵列、生命体征监视器。

PULP架构是RISC-V架构,核心是RISCY。RISCY是具有 4 个流水线阶段的有序单问题内核,其 IPC 接近 1,完全支持基本整数指令集 (RV32I)、压缩指令 (RV32C) 和乘法指令集扩展 (RV32M)。

整个项目非常适合RISC-v学习,同时开源的AXI总线也同样值得学习、参考。

整个项目文档非常完善,有兴趣的可以自行学习。

OpenCores上的AXI

OpenCores上的AXI主要是外围接口,下面简单介绍一下,相关的项目文档非常详解,有兴趣可以自行查看。

FTDI FT60x USB3.0 to AXI bus master

https://opencores.org/projects/ft60x_axi

https://github.com/ultraembedded/core_ft60x_axi

https://github.com/ultraembedded/core_ft60x_axi

https://github.com/alexforencich/verilog-ft245

项目框图

__ __ __ __ __ __ __ __ __

clk __/ \__/ \__/ \__/ \__/ \__/ \__/ \__/ \__/ \__

_____ _________________

tdata XXXXXXXXX_D0__X_D1______________XXXXXXXXXXXXXXXXXXXXXXXX

_______________________

tvalid ________/ \_______________________

______________ _____ ___________

tready \___________/ \___________/

WishboneAXI

https://opencores.org/projects/wishboneaxi

https://opencores.org/projects/ahb2wishbone

https://opencores.org/projects/ahb_m_wishbone_s

模式:

AXI4Lite -> Wishbone Classic

AXI4Lite -> Wishbone Pipelined

Wishbone Pipelined -> AXI4Lite

Wishbone Classic -> AXI4LiteAHB DMA 32 / 64 位

https://opencores.org/projects/dma_ahb

https://opencores.org/projects/dma_axi

https://opencores.org/projects/axi_dma

单通道 32 或 64 位 AHB 主 DMA 内核。支持同时读写、命令列表、外设控制、超时和字节交换。

AHB系统生成器

https://opencores.org/projects/ahb_system_generator

目的是提供一种简单的方法来配置、创建和模拟“完整的”AHB 系统。

要运行 AHB 系统生成器,您必须安装 PERL 和一个名为 Tk 的 GUI PERL 模块

AXI4 Transactor and Bus Functional Model

https://opencores.org/projects/axi4_tlm_bfm

该项目以 VHDL 实现 AXI4 事务级模型 (TLM) 和总线功能模型 (BFM)。

Generic AHB matrix

https://opencores.org/projects/robust_ahb_matrix

https://opencores.org/projects/robust_axi_fabric

通用 AHB 矩阵。它是一个具有循环仲裁的多主、多从非阻塞 AHB 矩阵。

Generic AXI to AHB bridge

https://opencores.org/projects/robust_axi2ahb

https://opencores.org/projects/robust_axi2apb

通用 AXI 到 AHB 桥接器。根据输入参数构建:AXI 命令深度、数据位等。支持非法 AHB 突发错误和 AHB 从机错误。

AXI2NandFlash

https://github.com/cjhonlyone/NandFlashController

AXI 接口 Nand Flash 控制器(同步模式)

gen_amba

https://github.com/adki/gen_amba

https://github.com/adki/gen_amba_2021

'gen_amba' 是一个生成 AMBA 总线 Verilog-HDL 的程序,包括 AMBA AXI、AMBA AHB 和 AMBA APB。

- gen_amba_axi : 用于多主机和多从机的 AMBA AXI 总线生成器

- gen_amba_ahb : 用于多主机和多从机的 AMBA AHB 总线生成器

- gen_amba_apb:用于 AMBA AXI 或 AHB 的 AMBA APB 总线桥生成器

AXI4_Interconnect

https://github.com/Verdvana/AXI4_Interconnect

https://github.com/seonskim/verilog_axi-interconnect

AXI4总线连接器,将最多4个AXI4总线主设备连接到最多8个AXI4总线从设备。

USB -> AXI Debug Bridge

https://github.com/ultraembedded/core_usb_bridge

该组件是一个 USB(CDC-ACM / USB 串行)到 AXI4-Lite 总线主桥。

core_sdram_axi4

https://github.com/ultraembedded/core_sdram_axi4

该 IP 内核是一个小型、简单的 SDRAM 控制器,用于将 32 位 AXI-4 总线连接到 16 位 SDRAM 芯片。AXI4-Slave 支持 FIXED、INCR 和 WRAP 突发。支持 16 位 SDRAM 部件。

FreeCores相关项目

https://github.com/freecores/axi_master

AXI DMA驱动

https://github.com/fpgadeveloper/fpga-drive-aximm-pcie

https://github.com/jacobfeder/axisfifo

https://github.com/bperez77/xilinx_axidma

ethernet-fmc-axi-eth

https://github.com/fpgadeveloper/ethernet-fmc-axi-eth

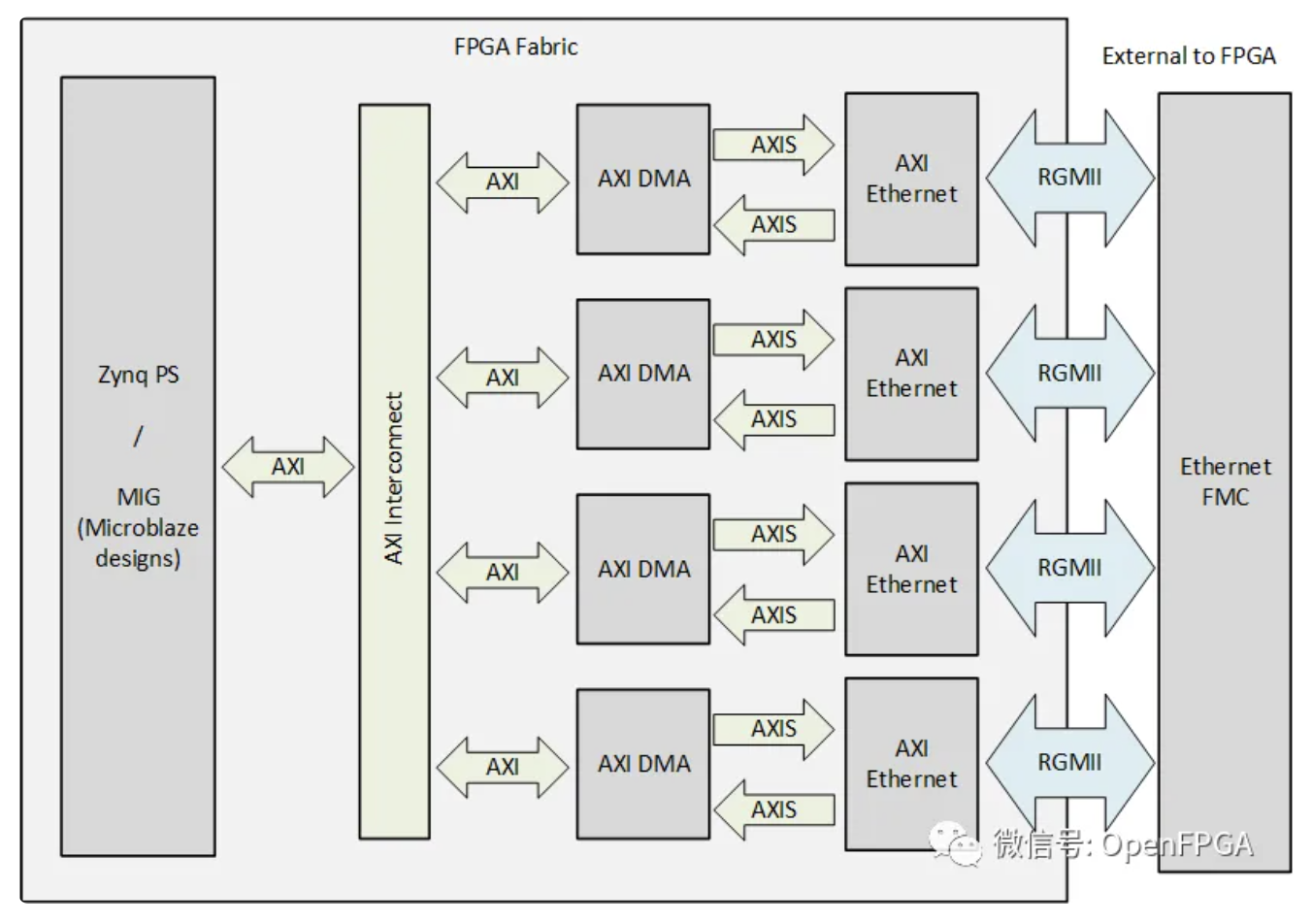

项目框图

该设计包含 4 个配置有 DMA 的 AXI 以太网模块。

总结

今天介绍了几个AXI总线的项目,在FPGA应用上,相关厂商都是有相应的IP,使用起来难度不是很大,但是在其应用不具备广泛性,一些特殊应用还是需要自己“撸”代码。这几个项目,前几个还是特别推荐的(个别项目是经过制作验证过的),后面的项目偏应用型,看自己需求选择。

最后,还是感谢各个大佬开源的项目,让我们受益匪浅。后面有什么感兴趣方面的项目,大家可以在后台留言或者加微信留言,今天就到这,我是爆肝的碎碎思,期待下期文章与你相见。

原文:OpenFPGA

作者:碎碎思

相关文章推荐

更多FPGA干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。