在新坑。。新系列文章: Verilog TestBench 中,作者将写一系列简单得发指的 Verilog 代码与 Demo,在这个过程中致力于发现了解 Verilog 的可综合代码综合特性,EDA 工具工作细节等 FPGA 知识。

第一期中,我们将借助 ISE 14.7 工具一起来探寻综合工具 XST 如何将一些 Verilog 代码转换为对应的数字电路。

常说,我们 Veriloger 们和他们不一样,我们写的不是代码,是电路!

但当然,我们敲出来的还是真真实实的代码(描述语言),那么是谁在背后将这些代码转换成电路?

是综合工具们。说综合工具们,是因为综合工具真的非常多,但我们在开发 FPGA 过程中目前接触比较多的还是厂商们的综合工具,比如 Xilinx 的 ISE 的 XST。

故事的俗套开头

人们总用一个俗套的例子开始这类故事,作者也不例外:让我们从一个(或多个)逻辑门开始吧!

assign d = a | ( b & ~c);

这句语句会产生怎样的综合结果?

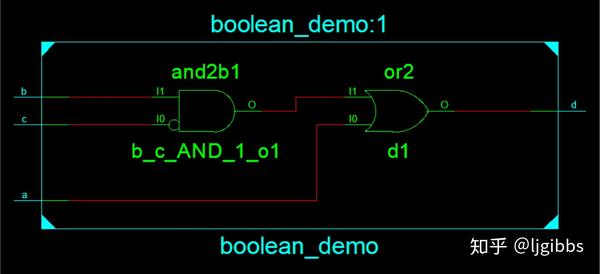

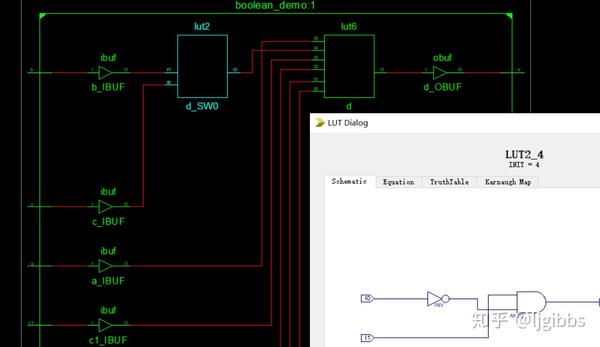

在我的笔记本用了长达 20 秒时间之后,我们得到了这样的 RTL 图:

综合产生了一个与门和一个或门,实际上还有一个非门,这和表达式相吻合。我们括号中的与非逻辑在数字电路中,高优先级体现在逻辑门的位置与连接中。

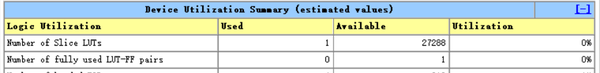

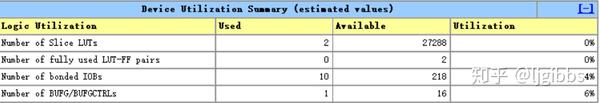

资源报告显示我们只使用了一项资源,那就是一个 LUT,查找表,是 FPGA 的一项最基本的资源,后续的文章将用尽可能简单的文字描述 LUT 的实现。

但其实我们不需要查看综合资源报告也可以知道,我们只使用了一个 LUT。因为我使用的器件是 Spantan-6,配备的是 6 输入 LUT,逻辑目前只有 3 个输入,自然只会使用到一个 LUT。

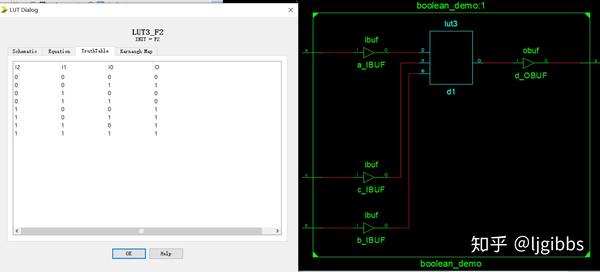

我们也可以通过 ISE 综合选项中的 View Technology Schematic 查看具体到 LUT 的综合情况(比较好奇为什么叫 Technology?)。上一项 View RTL Schematic 则只能看到逻辑门,选择器,比较器模块级别的综合结果。

通过 View Technology Schematic 我们可以看到 LUT,输入输出缓冲等,双击 LUT 还可以查看查找表的内容以及卡诺图等。

左侧为双击 LUT 后打开的窗体

如果把输入变量增加到 7 个,就可以综合出两个 LUT。

assign d = a | ( b & ~c) & c1 & c2 & c3 & c4;

右侧的窗口表示:第一个 LUT 实现了一个与非门,这应该和我们的逻辑表达式中,与非逻辑因为括号的原因,运算优先级最高有关。

随手翻阅一下综合报告,我们的设计实在太简单了,XST 甚至没找出一个 Warning.(~\_~)

同步起来

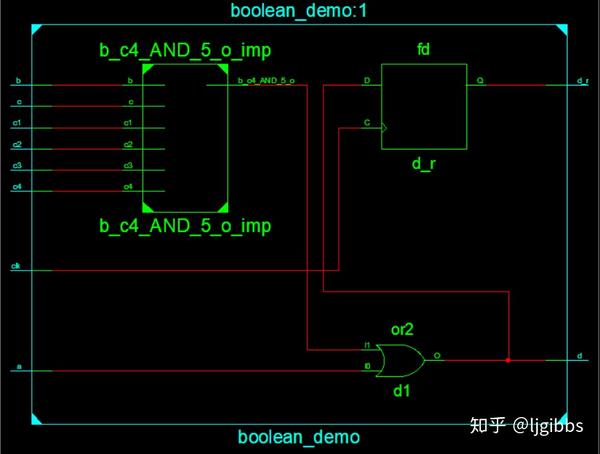

上文中都是组合逻辑,FPGA 中另一项重要资源 FF ,触发器都还没派上用场。如果我们为逻辑门的输出进行一拍同步打拍的话,那就可以综合出一个触发器。

always @(posedge clk) begin

d_r <= d;

end

因为加入了一个时钟信号的关系,消耗的资源增加了一个时钟输入端的 buff,BUFG,这同样是一种重要资源。

综合完成后,先检查一番

搁作者以前,每次综合通过后都开心得不得了,往往心急火燎地开始布线,但最后因为一些错误的存在,布线步了也白布。

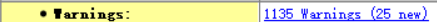

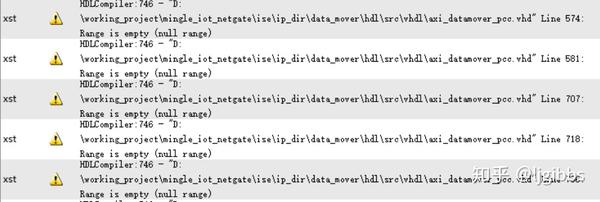

我们在综合完成后,最好的习惯自然是查看一下综合报告中的 Warning(自不用说:Error 你肯定会看),当然 Warining 存在一个小问题,那就是数量实在太多了。一个很迷你的 Demo,不到 1W 个 LUT,却有

上千个错误。。放谁身上也没法一个个看个仔细。但其实我们需要关心的只有那么两类错误:有没有漏连或者连错线,以及有没有错误地截断信号,这往往是造成很多怪异的,不明所里的错误现象的原因。

上述警告是因为有变量在赋值时被截断了,重点检查是否符合设计,最好完全避免这类位宽不一致的问题,以减少风险。

上述警告是因为有变量/连线因为未被连接所以被优化去除了,此时要检查是否连线正确。

其实很多警告看上去多,实际上只是充数的,比如这些。可以看到他们所在的路径实际上在 ip 核内,ip 核的警告我们实际上也就不需要理会了。

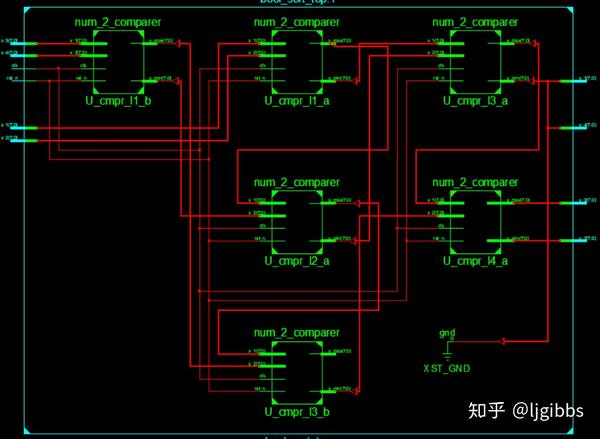

如果实在不想看警告,实际上有个偷懒的方法,查看综合后的 RTL 图,如果图中的信号连接混乱,被插入了不必要的非门,有的信号甚至被直接接地,那你就需要好好检查一番了。可能不光是信号连线的问题,也有可能是信号位宽有误,比如下述这种情况:

输出信号直接接地还怎么玩

错误的原因在于中间信号位宽与模块输入输出信号位宽不匹配,从 RTL 图上根本看不出来啊。

报 Warning 了,能直接报 Error 就好了

结束语

本文通过几个简单的 demo 初探了 verilog 可综合语句在综合过程中的硬件映射问题,另外还给出了一个检查综合报告的忠告。后续的文章会在这方面继续深入,也会做一些其他的,有意思的 Verilog 实验。

如果你喜欢这个系列或者本篇文章,可以点赞,感谢,收藏以及关注我和我的专栏。