本系列中我们将一起探寻 Xilinx FPGA 的硬件开发环境 Vivado,发现 Vivado 的 Design Flow,使用 Tips...或许再来一些 BUG?Happy Design in Vivado!

作者:李凡

来源:https://zhuanlan.zhihu.com/p/92225385

- 注:我好像不怎么想去翻 UG xxx 来写这系列文章 -\_- ,有错欢迎大家翻着 UG 指出。

- 注2:如无意外,本系列将持续使用 2018.3

二·时序分析说了什么

在添加时钟约束后,原先显示 INF 的时序报告就可以查看了。

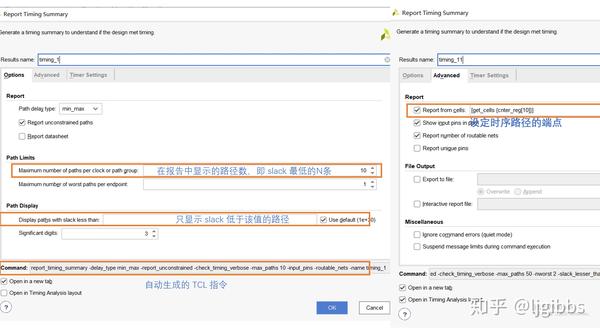

定制时序报告

生成时序报告界面中,可以定制待生成时序报告的属性。

一般比较常用的设置有这些:

· 报告中显示的路径数,因为报告是按照路径的 slack 从低到高显示的,所以这项设置的意思就是显示 slack 最低的 N 条路径。

· 过滤显示 slack 低于设置值的路径。

· 图片右侧带框项,表示的显示起点或者终点为某个信号的路径。

根据用户在 GUI 中的设置,Command 一栏会生成相应的 TCL 指令,直接运行这条 TCL 指令就可以生成一份时序报告,报告还按这次的图形界面中的值来设置。

其实 Vivado 中所有的图形化操作,都会生成一条 TCL 指令,选中下方的 console 栏,按 “ ↑ ”键就可以看到。

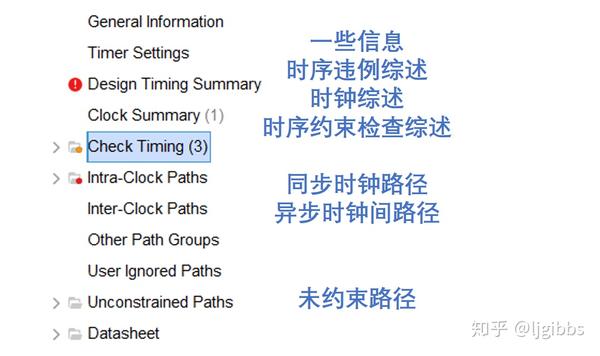

瞧瞧时序报告

时序报告由以下项目组成,一般出现在时序报告界面左侧。

时序报告包括一些时序检查的信息,比如某些检查规则是否开启等。

Design Timing Summary

当你关注你的设计是否产生时序违例,或者关心关键路径的长度时,首先关注 Design Timing Summary。它给出了最直观的信息——是否发生了 Setup/hold 违例,以及在同步设计中一般不需要关心的 Pulse widith。

给出的数据有,

最严重的时序违例有多严重: Worst Negative Slack

违例的检查点数量,以及占总检查点数量的比例: Failing Endpoint / Total Endpoint

直观地反映了你的设计需要多努力的时序优化,还是说...没救了。

但当时序违例相当严重的时候,先检查是否进行了正确的时序约束。即这位病人其实可能是时序假死。

Design Timing Summary(上) / Checking Timing (下)

Design Timing Summary

Checking Timing

通过 Checking Timing 界面可以反映是否适当地添加了时序约束。比如上图中有两个 High ,警告说有两个输入端口,输出端口没有约束输入输出延迟。是一个严重的问题。

输入输出端口的时序检查依赖于用户给出的延迟,在没有设定的情况下,delay 会默认为 0,假设是用户是忘记添加了真实的 delay ,情况就自然会很糟糕了。

还有一些节点没有时钟驱动,或者时钟为常量,那问题自然也很严重了额,这些节点上的寄存器可能并不会工作。

Checking Timing 中还会汇总一些其他约束的情况,比如添加了生成时钟的约束等等,作为约束和时钟信息的汇总。

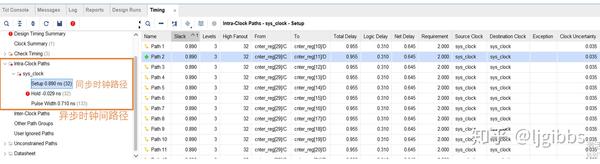

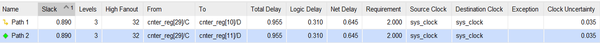

intra/inter clock Path

在 intra/inter clock Path 中可以分别查看同步时钟或者异步时钟的关键路径,分别有 setup/hold 路径两类,右侧给出了时序路径的相关信息,包括

Slack 时序裕度,Level 组合逻辑的级数,Hign Fanout 信号的扇出数量,

From/To 路径打哪开始,到哪结束,逻辑与连线延迟,时钟不确定度等等。

以 setup 为例,双击上方的路径,可以打开详细的时序路径分析:

有三条路径:

源时钟路径,是这条时序路径的开始

数据路径,是时序路径的终点,是为 Arrival Time

目的时钟路径,数据的采样路径,是为 Required Time

两者的差值,决定时序 setup 违例是否发生,若 slack 小于 0,则建立违例。

Slack = Required - Arrival

展开后可以看到经过一级 LUT 或者触发器的逻辑延迟与线延迟,也可以看到当前累积的延迟。

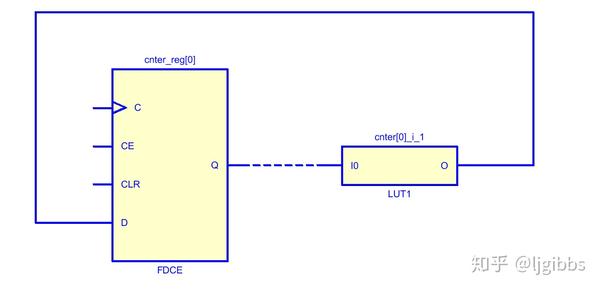

原理图及相应的延迟信息

查看路径原理图

为了更好地理解综合器综合出的电路图,在选中路径的情况下,点击左栏 synthesis design 中的 schematic,可以查看该条路径的原理图。

比如你知道为什么计数器 cnter\_reg[0], 计数器最低位会综合出上述的电路么

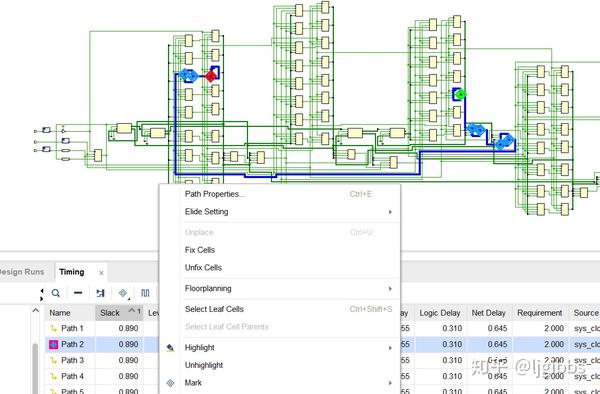

Highlight 与 Mark

另外,如何这么醒目地在一坨电路中,标记出这条关键路径呢。

右击路径,选择 Highlight ,可以给 path 上色,好比 Word 中的轮廓上色。

选择 Mark,可以给节点上色,比如图中的绿点代表起点,红点代表终点,而蓝色就是我们自定义的 Mark 节点颜色了,就好比是 Word 中的填充上色。

下回分解:三·尝试几种优化时序的办法

推荐阅读

关注此系列,请关注专栏FPGA的逻辑