本系列中我们将一起探寻 Xilinx FPGA 的硬件开发环境 Vivado,发现 Vivado 的 Design Flow,使用 Tips...或许再来一些 BUG?Happy Design in Vivado!

作者:李凡

来源:https://zhuanlan.zhihu.com/p/92153443

- 注:我好像不怎么想去翻 UG xxx 来写这系列文章 -\_- ,有错欢迎大家翻着 UG 指出。

- 注2:如无意外,本系列将持续使用 2018.3

当我还是一个(现在还是,并在长期内仍将是)FPGA 初学者时,我并不关心时序问题。那时候我满脑子想的就是,功能仿真正确。

但当时序报告出现 "赤字" 时,

严重时序赤字

当我们要对一个设计做性能优化,扣扣搜搜就是为了降低时序的赤字,想要查看最终能够到达多大的频率时,

就需要关注时序约束与分析。

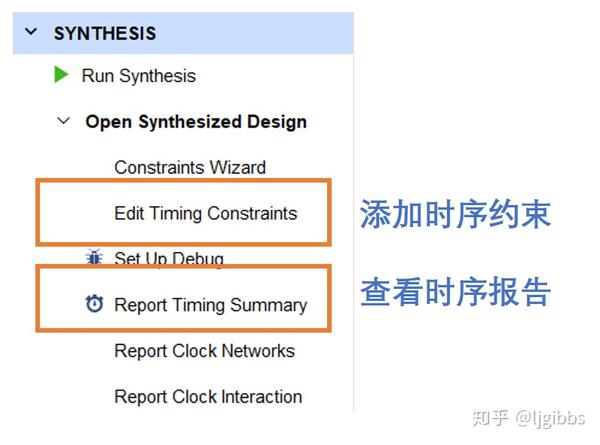

在综合之后的设计阶段,对时序做出合适的约束,并看的大致明白时序报告在说啥。

在综合后或者布局布线后两个设计阶段都可以查看时序报告,区别在于综合后时序分析的走线延迟 (Net Delay)基于经验预估值,而布局布线后的时序分析则基于真实的走线,更加精确。

这里以综合后时序分析为例。

一 · 从创建时钟约束开始

时序系统离不开时钟,时钟的脉动驱动系统。在你创建第一个时钟之前,时序分析是 tan90°(不存在)的。

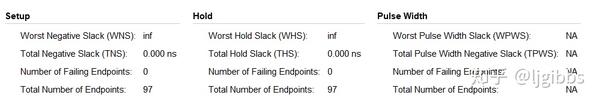

inf 的时序报告

添加时钟之前先需要思考三个问题

- 我从哪来....时钟的源

- 我是谁....时钟的信息:频率,占空比等等

- 又往何处去 ...时钟的目的地

其中在添加约束时需要手动添加的是前两个问题。

时钟的源头来自哪里?

可以来自一个外部引脚,比如晶振输入管脚

可以是一个内部信号,比如来自锁相环输出的倍频时钟,所以需要制定。

时钟的频率等信息将会参与时序路径的计算,需要设定一个接近实际情况的值。

时钟的目的地,也就是时钟的传播路径,将会由工具进行分析。

接下来我们就跟着指引在图形界面创建时钟。等你成为一个成熟的 FPGA 开发者之后你就可以写 xdc 文件里添加约束了。(这是后话了)

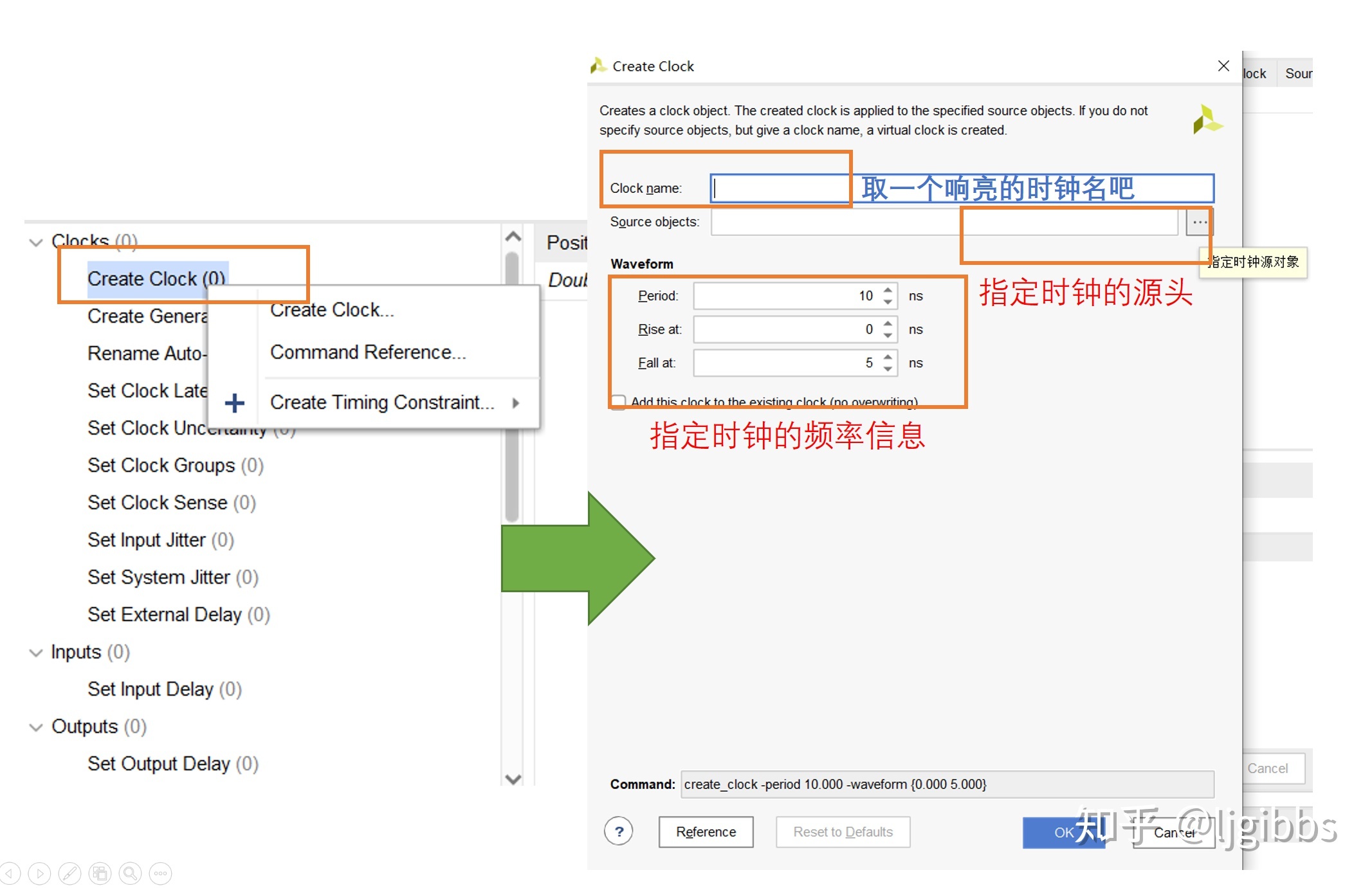

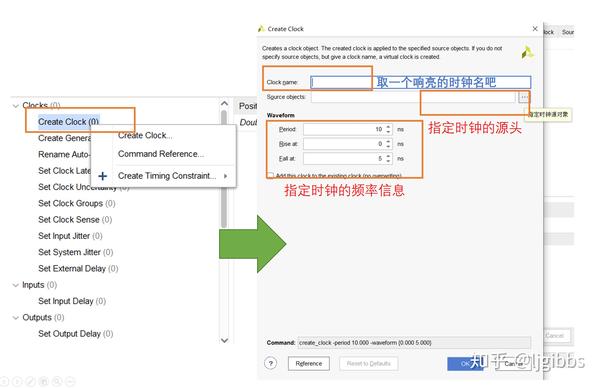

在添加时序约束界面,选择 create clock

设定一个时钟名,这个名字在之后的时序分析等过程中会作为时钟的标识,所以起个响亮的名字能给工具和你都省麻烦。

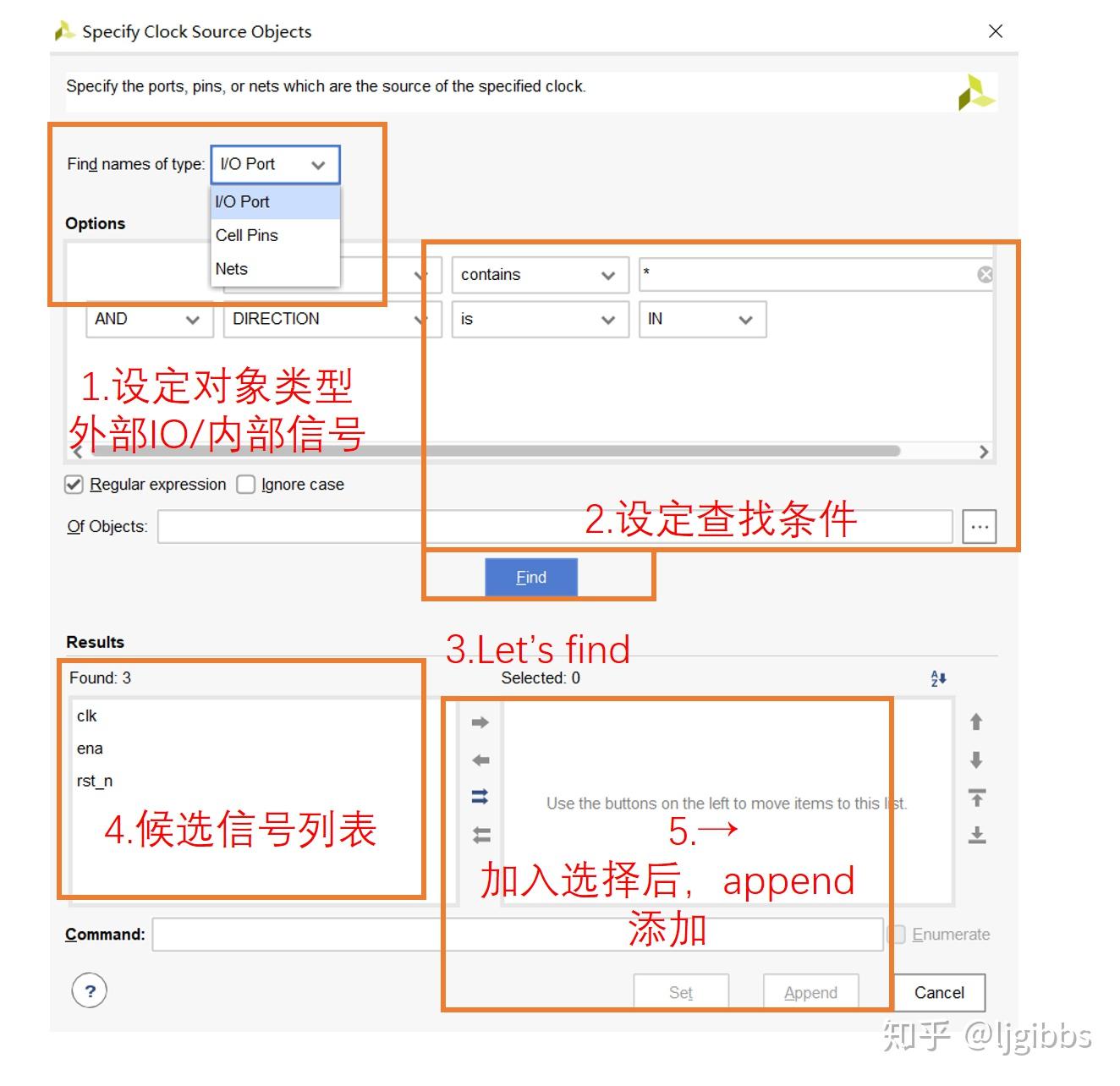

在指定时钟源 source object 时,可以使用 ... ,打开一个 Vivado 工程统一信号对象搜索器,搜索你要找的时钟源。

5 步完成时钟源选择,比如这里选择外部 IO 引脚,来自顶层的 clk 引脚作为时钟源。

至此就完成了时钟创建,时钟约束中的重要一步。更多的时序约束,我们会在后续文章(用到的时候)中介绍

下回分解:二·时序分析说了什么

推荐阅读

关注此系列,请关注专栏FPGA的逻辑