GICv3架构是GICv2架构的升级版,增加了很多东西。变化在于以下:

◾使用属性层次(affinity hierarchies),来对core进行标识,使gic支持更多的core

◾将cpu interface独立出来,用户可以将其设计在core内部

◾增加redistributor组件,用来连接distributor和cpu interface

◾增加了LPI,使用ITS来解析

◾对于cpu interface的寄存器,增加系统寄存器访问方式

一、gicv3结构

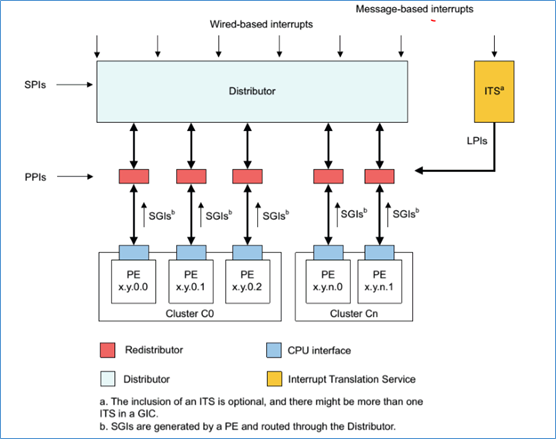

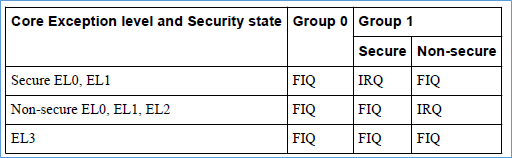

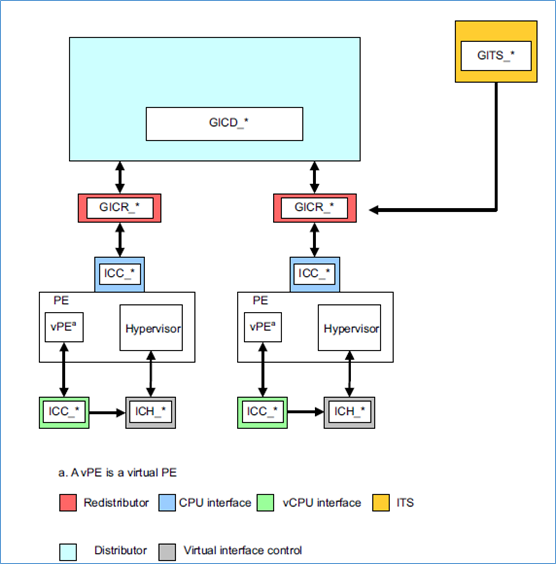

下图是gicv3的架构。

包含了以下的组件:

◾distributor:SPI中断的管理,将中断发送给redistributor

◾redistributor:PPI,SGI,LPI中断的管理,将中断发送给cpu interface

◾cpu interface:传输中断给core

◾ITS:用来解析LPI中断

其中,cpu interface是实现在core内部的,distributor,redistributor,ITS是实现在gic内部的。

cpu interface和gic的redistributor通信,通过AXI-Stream协议,来实现通信。

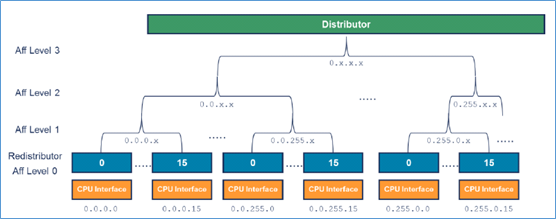

二、属性层次

gicv3的一大变化,是对core的标识。对core不在使用单一数字来表示,而是使用属性层次来标识,和arm core,使用MPIDR_EL1系统寄存器来标识core一致。

每个core,根据属性层次的不同,使用不同的标号来识别。如下图所示,是一个4层结构,那么对于一个core来说,就可以用 xxx.xxx.xxx.xxx 来识别。

这种标识方式,和ARMv8架构的使用MPIDR_EL1寄存器,来标识core是一样的。

每个core,连接一个cpu interface,而cpu interface会连接gic中的一个redistributor。redistributor的标识和core的标识一样。

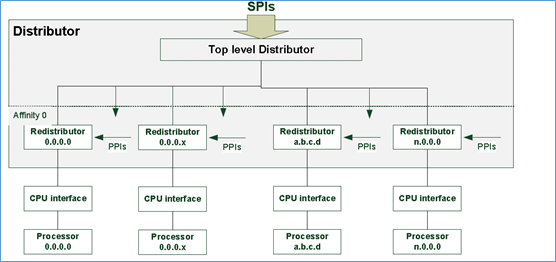

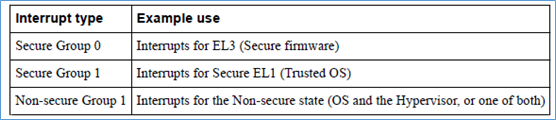

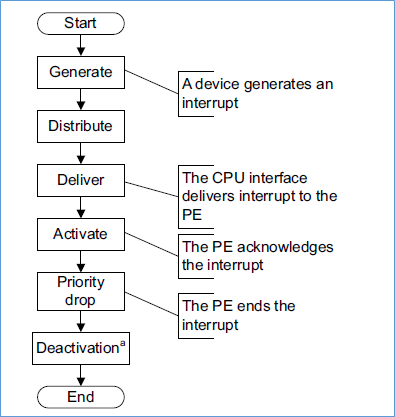

三、中断分组

gicv3,将中断分成了2个大组,group0和group1。

◾group0:提供给EL3使用

◾group1:又分为2组,分别给安全中断和非安全中断使用

如下图所示:

以下是IRQ,FIQ与组的对应关系。

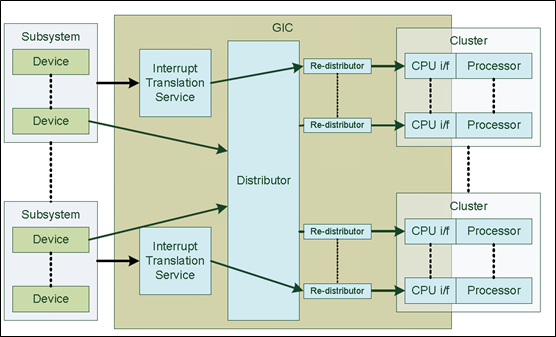

四、中断生命周期

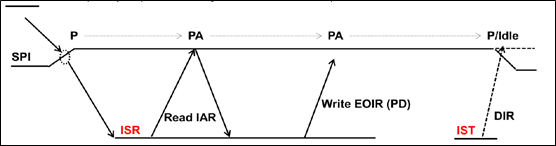

中断生命周期,如下图所示:◾generate:外设发起一个中断

◾distribute:distributor对收到的中断源进行仲裁,然后发送给对应的cpu interface

◾deliver:cpu interface将中断发送给core

◾activate:core通过读取 GICC_IAR 寄存器,来对中断进行认可

◾priority drop: core通过写 GICC_EOIR 寄存器,来实现优先级重置

◾deactivation:core通过写 GICC_DIR 寄存器,来无效该中断

这个中断生命周期,和gicv2的中断生命周期是一样的。

五、中断流程

下图是gic的中断流程,中断分成2类:

◾一类是中断要通过distributor,比如SPI中断

◾一类是中断不通过distributor,比如LPI中断

中断要通过distributor的中断流程

◾外设发起中断,发送给distributor

◾distributor将该中断,分发给合适的re-distributor

◾re-distributor将中断信息,发送给cpu interface。

◾cpu interface产生合适的中断异常给处理器

◾处理器接收该异常,并且软件处理该中断

LPI中断的中断流程

◾外设发起中断,发送给ITS

◾ITS分析中断,决定将来发送的re-distributor

◾ITS将中断发送给合适的re-distributor

◾re-distributor将中断信息,发送给cpu interface。

◾cpu interface产生合适的中断异常给处理器

◾处理器接收该异常,并且软件处理该中断

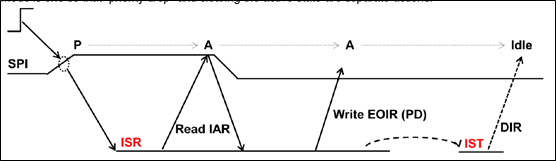

六、中断处理

中断处理,分为边沿触发处理和电平触发处理

1、边沿触发处理

外部边沿中断到达,中断状态被置为pending状态。

软件读取IAR寄存器值,表示PE认可该中断,中断状态被置为active状态

软件中断处理完毕后,写EOIR寄存器,表示优先级重置。过一段时间后,写DIR寄存器,中断状态被置为idle状态。

2、电平触发处理

外部高电平中断到达,中断状态置为pending状态。

软件读取IAR寄存器,表示PE认可该中断。但中断依然为高,中断状态进入pending and active状态。

软件中断处理完毕后,写EOIR寄存器,表示优先级重置。过一段时间后,写DIR寄存器,中断状态被置为idle状态。

七、寄存器

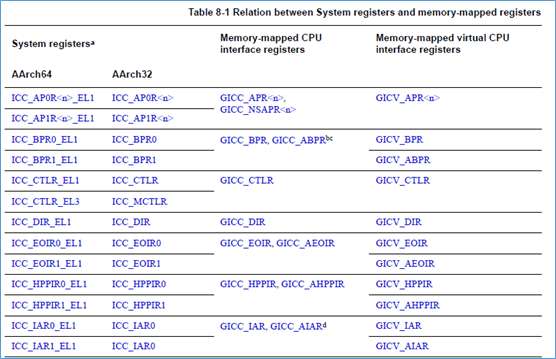

gicv3中,多了很多寄存器。而且对寄存器,提供了2种访问方式,一种是memory-mapped的访问,一种是系统寄存器访问:

memory-mapped访问的寄存器:

◾GICC: cpu interface寄存器

◾GICD: distributor寄存器

◾GICH: virtual interface控制寄存器,在hypervisor模式访问

◾GICR: redistributor寄存器

◾GICV: virtual cpu interface寄存器

◾GITS: ITS寄存器

系统寄存器访问的寄存器:

◾ICC: 物理 cpu interface 系统寄存器

◾ICV: 虚拟 cpu interface 系统寄存器

◾ICH: 虚拟 cpu interface 控制系统寄存器

下图是gicv3中,各个寄存器,所在的位置。

对于系统寄存器访问方式的gic寄存器,是实现在core内部的。而memory-mapped访问方式的gic寄存器,是在gic内部的。

gicv3架构中,没有强制,系统寄存器访问方式的寄存器,是不能通过memory-mapped方式访问的。也就是ICC, ICV, ICH寄存器,也是可以实现在gic内部,通过memory-mapped方式去访问。但是一般的实现中,是没有这样的实现的。

下图是ICC的系统寄存器,和memory-mepped方式寄存器的对应关系的一部分,更多的就要查看gicv3的spec。

那么,问题来了,gicv3中,为什么选择将cpu interface,从gic中抽离,实现在core内部?为什么要将cpu interface的寄存器,增加系统寄存器访问方式,实现在core的内部?这样做,是有什么好处?

我认为,gicv3的上述安排,第一是为了软件编写能够简单,通用,第二是为了让中断响应能够更快。

首先要先了解,在gic的寄存器中,哪一些寄存器,是会频繁被core所访问的,哪一些寄存器,是不会频繁被core所访问的。毫无疑问,cpu interface的寄存器,是会频繁被core所访问的,因为core需要访问cpu interface的寄存器,来认可中断,来中断完成,来无效中断。而其他的寄存器,是配置中断的,只有在core需要去配置中断的时候,才用访问得到。有了这个认识,那么理解之后我所讲述的,就比较容易了。

在gicv2中,cpu interface的寄存器,是实现在gic内部的,因此当core收到一个中断时,会通过axi总线(假设memory总线是axi总线),去访问cpu interface的寄存器。而中断在一个soc系统中,是会频繁的产生的,这就意味着,core会频繁的去访问gic的寄存器,这样会占用axi总线的带宽,总而会影响中断的实时响应。而且core通过axi总线去访问cpu interface寄存器,延迟,也比较大。

在gicv3中,将cpu interface从gic中抽离出来,实现在core内部,而不实现在gic中。core对cpu interface的访问,通过系统寄存器方式访问,也就是使用msr,mrs访问,那么core对cpu interface的寄存器访问,就加速了,而且还不占用axi总线带宽。这样core对中断的处理,就加速了。

cpu interface与gic之间,是通过专用的AXI-stream总线,来传输信息的,这样也不会占用AXI总线的带宽。

gicv3架构的内容,比较多,我这边会拆成几个部分。

下一部分,会介绍gic stream协议。也就是cpu interface与gic之间的通信。

系列其他篇

原文首发于骏的世界博客

作者:卢骏.

更多Arm技术相关的文章请关注Arm技术博客极术专栏,每日更新。