GICv3架构中,对中断进行了分组。分成了以下三个组:

◾group0,用于EL3处理的中断

◾secure group1:用于secure EL1处理的中断

◾non-secure group1:用于non-secure的EL2和non-secure的EL1。

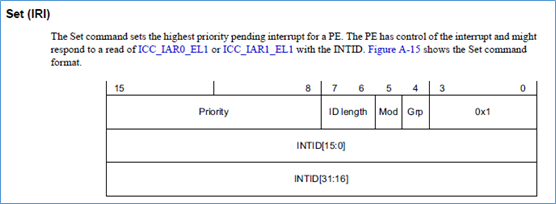

对于redistributor的set命令,带有Mod和Grp参数。

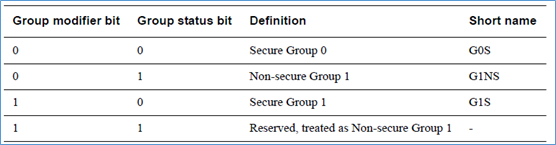

Mod与Grp共同表示,中断所属的组。其组合如下图所示:

对于每一组中断,有一个系统寄存器,来控制该组中断是否有效。

◾ICC_IGRPEN0_EL1:针对group0的中断

◾ICC_IGRPEN1_EL1:针对group1的中断,该寄存器分为non-secure和secure访问,不同的secure下,是访问当前secure下的寄存器

而每个中断的分组,由以下两个寄存器来决定:

◾GICR_IGROUPR<n>: interrupt group registers

◾GICR_IGRPMODR<n>:interrupt group modifier registers

每个中断,占寄存器中的1个bit,使用中断号进行索引。

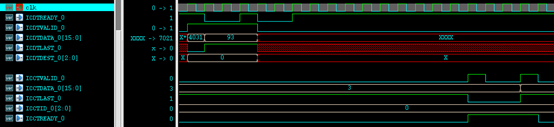

当gic给cpu interface通过set命令发送中断,cpu能够响应该组中断,会回发activate命令,认可该中断。

如果cpu不能响应该组中断,会回发release响应。如下图所示:

gic给cpu interface通过set命令发送中断,中断号为93,优先级为0x40,Mod和Grp均为1,表示non-secure的group1。

cpu interface不能响应该中断,回发release响应。

系列其他篇

原文首发于骏的世界博客

作者:卢骏.

更多Arm技术相关的文章请关注Arm技术博客极术专栏,每日更新。