上次回忆了Setup的概念并介绍了后端设计中常用的解决setup violation的手段,本篇文章将讲述hold的概念和常用的解决hold violation的方法。

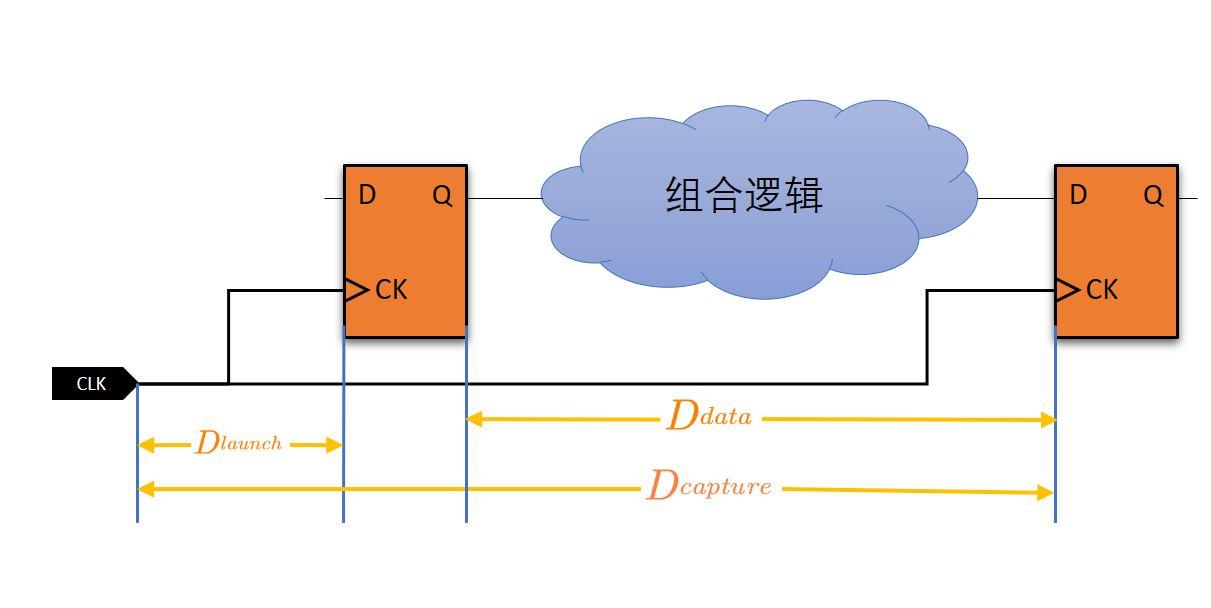

同样,我们先回忆一下hold timing check的概念。下图-1展示了一条典型的timing path以及hold time的计算方法:

图1

其中:

对于图-1中的timing path,hold check需要满足如下条件:

同上篇中的setup相同,在实际设计中,因为会有一些margin加入,所以计算公式与上述略有不同,但本质没有改变。那么,遇到hold violation一般怎么修呢?根据上面的公式可以看出,主要有三类方法:

1. 增大data line delay

此方法为后端设计中最常见的手法。具体操作是在data line上插入buffer 或者delay cell去增加delay。在此提出一个问题请大家思考:插入buffer或者delay cell的位置,是靠近launch端还是capture端,还是并无任何要求呢?答案下期揭晓~

2. 增大launch clock delay

增加launch clock delay的方法理论上可行,但是在实际中不到万不得已我们是不希望动到clock的,因为动clock line不仅需要确认前后级path是否有足够的margin,有时候还会遇到影响范围不可控或者实现不方便等诸多限制。

3. 减小capture clock delay

此方法也具有方法2的缺点,同时还因为剪短clock delay在物理上无法实现的风险,因此应用更少。

总结来说,与setup不同,hold因为与clock cycle并无关系,只要clock tree做的比较balance,hold就比较容易收敛。但是因为setup和hold其实是一对相互制约的约束,也就是说修了hold后setup的slack就会变小甚至变负,因此越是高频的path,setup和hold相互制约就越严重,甚至会出现修了setup后hold就修不掉的所谓“互卡”现象。

以上就是后端设计中对hold violation的常用处理方法。同样,关于这部分内容的脚本化处理方法,将在以后的tcl学习文章中逐步介绍,敬请关注。

相关文章

如果大家有任何后端技术与职业发展方面的问题,抑或关于数字后端感兴趣的技术话题想要了解和探讨,欢迎关注我的知乎专栏: 数字IC后端设计工程师修炼之路同时欢迎关注微信公众号:数字后端芯讲堂,一起探讨技术,共同提升!

本极术专栏也会同步更新芯片设计后端的技术干货,也请关注数字IC后端设计工程师修炼之路。