Legalization是后端设计中的基本概念之一,我们可以简单地理解为工具尝试找到合适的位置放置standard cell (以下简称stdcell)。但是stdcell【合适的位置】的定义却随着工艺的演进变得越来越复杂。一般来说工具认为一个【legalized stdcell】通常要满足以下基本条件:

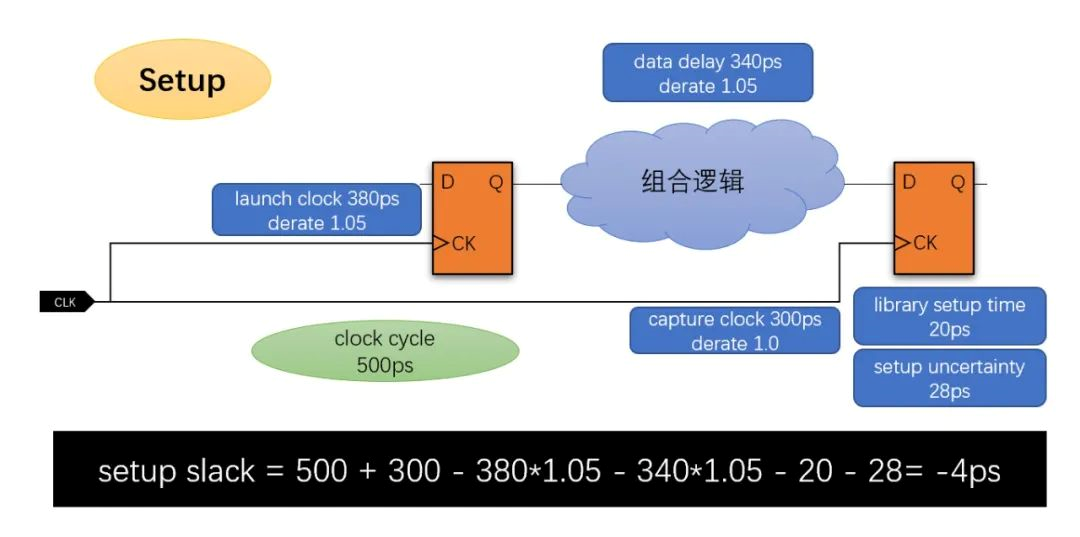

OCV的概念对于数字后端设计来说是非常重要的基础概念,读过小编文章的同学一定都不陌生。如果对此概念还不太熟悉,可以回顾以下两篇文章:

想写本篇的初衷源自于最近的几次面试提问。小编自认为并不是喜欢刁难人的面试官,对“面试造火箭,工作拧螺丝”的现象也感深恶痛绝,因此许多提问都是针对实际中可能遇到的问题。最近面对多名面试者,有两个问题很少有人能准确地给出答案,不管是工作一两年还是三五年甚至六七年的,总有很多人不能完全理解,甚至不少人的...

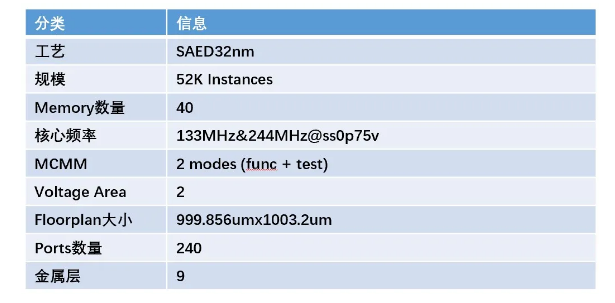

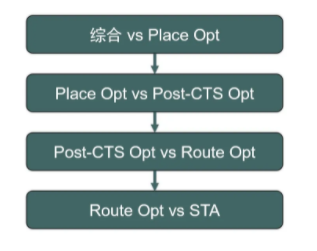

上篇文章我们大致介绍了7nm实现中Innovus和ICC2常见的DRC问题【后端进阶系列:Innovus+ICC2对比7nm工艺的后端实现(物理篇)】,本篇将简要归纳一下二者在时序(Setup&Hold)、面积、Inst数量、Power和runtime等具体参数上的差异。

Innovus和ICC2在先进工艺的下的表现本身已有定论,毕竟大部分公司已经用脚投票了。尽管如此,对于大部分没有从事过工艺和工具评估的同学来说,很难直接认识到它们在结果上的差距。最近终于有机会实现这样一件事,借此机会将大部分结果分享出来供大家参考。由于篇幅较长,本期只将二者的整体对比和在物理DRC方面的比较贴...

本篇致力于分享小编收集并整理的精品IC前后端设计相关文档,大家可以根据自己的需要获取,如果有其他想要的文档可以私信或者加微信chen2mao2574联系小编帮忙寻找。

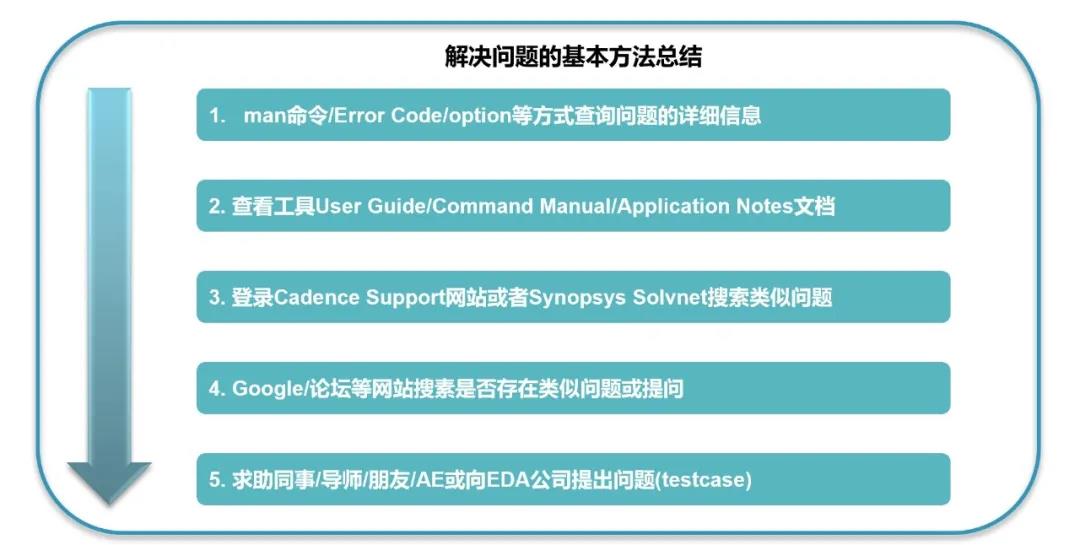

很长一段时间来,通过网站论坛学到了很多东西,也有热心的网友无私提供了很多非常宝贵的实验素材,这些东西都对自己的学习有非常大的帮助。有鉴于此,自己也思考了一下是否可以为初学者贡献点什么,最终决定将自己做的一个lab和对应脚本公开,供有需要的人参考。

在整个数字后端实现过程中,有多种验证需要保证芯片最终的正常工作,其中时序收敛是非常重要的一环,它确保的是芯片在特定PVT条件下能够达到产品定义的既定性能指标。

本文包含了过去半年中自己、同事和朋友等多位候选人的面试经历和感受,小编尽量做到客观陈述,但不免掺入主观感受,因此所有观点仅供大家参考,也欢迎大家留言讨论你的面试经历。

内容预警:本文仅从技术方面讨论数字后端新人的成长建议,大量内容包含作者的主观感受,如有不同意见欢迎留言讨论!文章较长需要些时间,请保持耐心。

内容预警:本文仅从技术方面讨论数字后端新人的成长建议,部分观点包含作者的主观感受,如有不同意见欢迎留言讨论!文章较长需要些时间,请保持耐心。

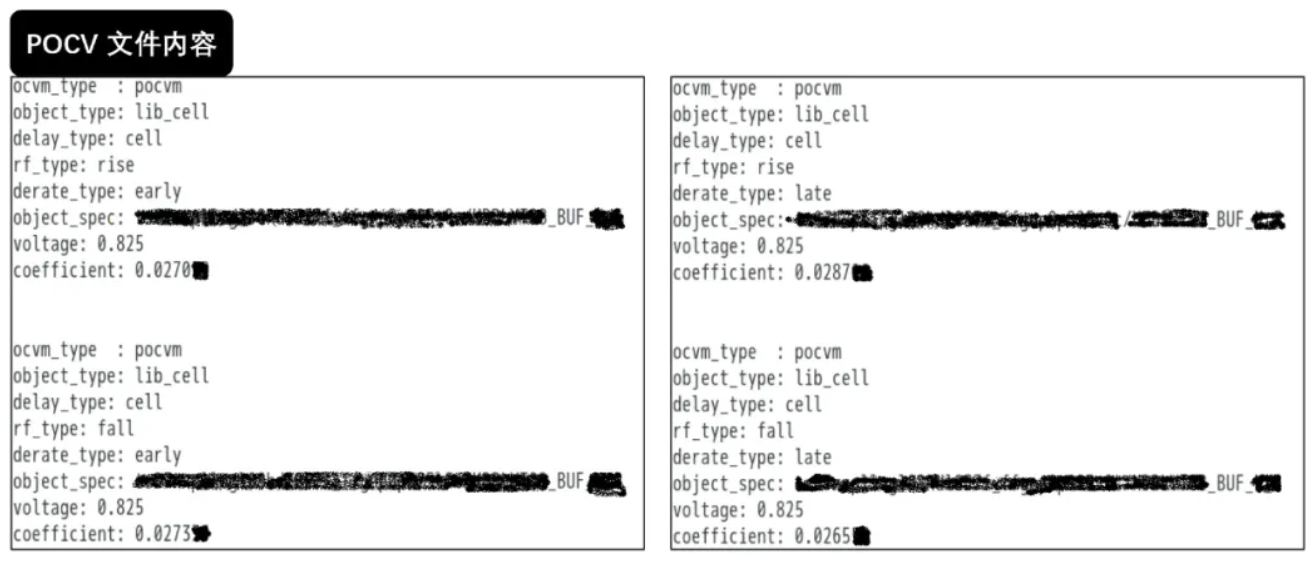

OCV大家应该都了解,对应的AOCV想必也不陌生。之前小编也专门介绍各类OCV的概念,如果还有同学不太了解则可以温习一下这两篇文章:

后端设计中有几种常见的特殊cell类型,它们基本上都是physical only cell,但是各自的特点却又不同,而且不同的工具设置和插入他们的方式也不尽相同。

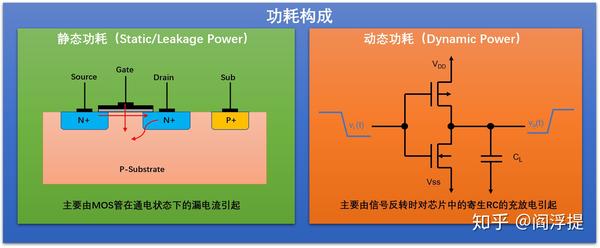

之前的文章我们引入了不少低功耗设计的基本概念,同时也介绍过芯片的总体功耗计算方法,其中就包括internal power的定义。今天想深入挖掘internal power以及它在应用过程中有哪些细节需要大家注意。

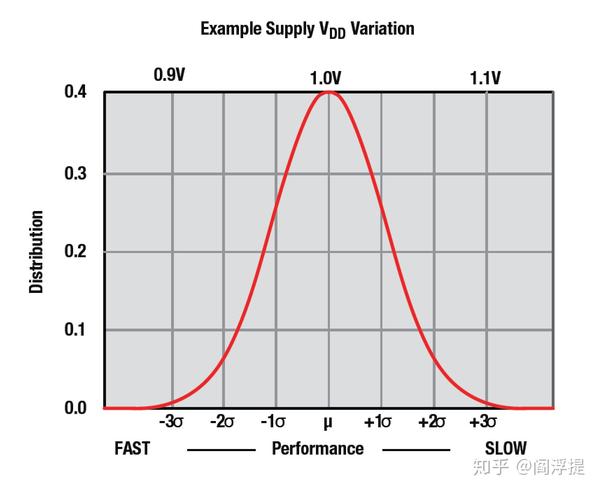

我们知道所有芯片在设计之初都需要规划好芯片的参数和应用场景,统称为芯片的spec。在spec中通常会定义一个或几个典型的应用场景以及它对应的工作条件如电压、频率和功耗上限等。因此绝大多数芯片的工作条件尤其是电压和频率在一开始就是比较固定的。然而在实际流片后,往往会出现不同芯片的最高频率不同的情况,最主要...

集成电路发展到今天已经经历了逾半个世纪,超大规模集成电路(VLSI)也已经出现了数十年。尽管工艺从0.13um以上缩小到现在的10nm以下,但是除了工艺研发和后端设计,鲜有人真正了解这些工艺升级背后所遇到的技术和设计挑战。

在2020年的用户大会(SNUG)上,Synopsys介绍了一款新的数字前端工具RTL Architect, 虽然现场没有演讲提供使用体验,但是相信不少公司已经在测试导入了。到底这是一款什么产品呢?让我们来一探究竟!

订阅极术公开课,即时获取最新技术公开课信息

嵌入式端AI,包括AI算法在推理框架Tengine,MNN,NCNN,PaddlePaddle及相关芯片上的实现。欢迎加入微信交流群,微信号:aijishu20(备注:嵌入式)

Arm相关的技术博客,提供最新Arm技术干货,欢迎关注