集成电路发展到今天已经经历了逾半个世纪,超大规模集成电路(VLSI)也已经出现了数十年。尽管工艺从0.13um以上缩小到现在的10nm以下,但是除了工艺研发和后端设计,鲜有人真正了解这些工艺升级背后所遇到的技术和设计挑战。

对于数字后端设计,就我所遇到的相关专业的学生和从业人员,仍然有大量的人并不清楚数字IC后端设计究竟是在干什么。或者即使有人了解,也仅仅局限于“后端不就是跑flow的么”、“后端就是画版图的“等或流于表面或与全定制版图混淆的认知范围。其实造成这种现象的重要原因之一在于集成电路设计制造是一个极其复杂的过程,不仅需要广泛的的知识储备,同时由于分工的精细化,从学校到工作,每个人所能接触和了解的范围被大大限制了。

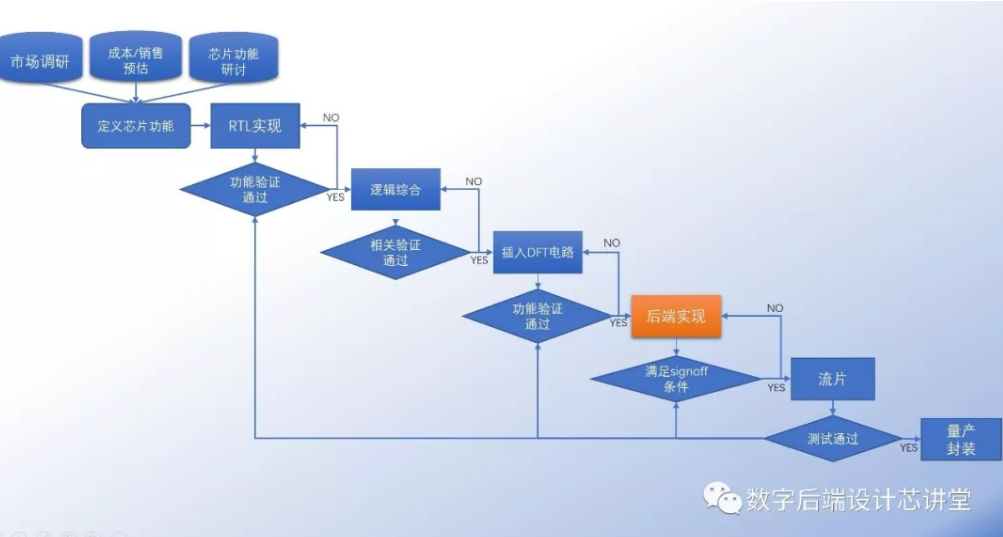

下面的图-1展示了整个芯片从设计到制造的大致流程。在团队比较成熟的企业中,下图中的每一步都由专门的团队负责,甚至每个步骤之内还会分成更小的部分让不同的人去分担。这也就不难理解,为什么除了后端出身的人之外,很少有人真正懂得后端设计的原因了。

图-1

从图中可以看到后端设计只是芯片设计整个流程的一部分,但是在实际设计中,后端却往往是挑战最多,工期最紧,对芯片整体性能影响最大的一部分。

在工艺进入45nm以下,以及市场对低功耗的要求逐渐增加,要想实现最优的性能功耗,往往需要前后端人员的通力合作。可是现实却是,大多数前端工程师并不了解后端,甚至很多人对后端的基本内容都没有任何概念,也无法理解后端反馈回来需要修改电路的原因究竟是什么。结果就是不仅造成大量的重复工作,还对芯片整体的设计周期,成本以及最终性能和功耗造成严重的负面影响。

在芯片设计面临诸多挑战的今天,“个人只扫门前雪,不管他人瓦上霜"的分工和工作方式已经不能满足现状。每个立志成为优秀IC工程师的人,不管是设计还是验证,不管是前端还是后端,都应该了解数字后端的基本流程,在并尽可能在前期设计中考虑到后端可能遇到的问题并加以优化。这样不仅能够加速收敛,同时对提升芯片性能,降低流片成本也会有重要意义。

本文转载自微信公众号:数字后端设计芯讲堂

原文链接:https://mp.weixin.qq.com/s/7EehMCtw1N\_GuLxaTCmZQw

未经作者同意,请勿转载!

推荐阅读

如果大家有任何后端技术与职业发展方面的问题,抑或关于数字后端感兴趣的技术话题想要了解和探讨,欢迎关注我的知乎专栏: 数字IC后端设计工程师修炼之路同时欢迎关注微信公众号:数字后端芯讲堂,一起探讨技术,共同提升!

本极术专栏也会同步更新芯片设计后端的技术干货,也请关注数字IC后端设计工程师修炼之路。