实现AHB-Lite系统需要单独的读写数据总线,不使用三态总线。

HWDATA

master在写传输期间驱动写数据总线。如果传输被延长,master必须保持数据有效,直到传输完成,此时HREADY = HIGH。

对于比总线宽度窄的传输,例如在32位总线上进行16位传输,master需要驱动对应的byte lanes,然后slave选择来自正确byte lanes的数据。

有效的byte lanes取决于系统的字节顺序(endianness)。因为AHB-Lite没有指定endianness,所有master和slave需要使用相同的endianness。

HRDATA

在读传输期间,被选择的slave驱动读数据总线。如果slave通过保持HREADY LOW延伸读传输,然后slave必须在传输的最后一个周期提供有效的数据,此时HREADY = HIGH。

对于比总线宽度窄的传输,slave只需要提供特定byte lanes的有效数据。master从正确的byte lanes中获取数据。

当传输使用OKAY完成传输时,slave才需要提供有效数据。ERROR响应不需要提供有效数据。

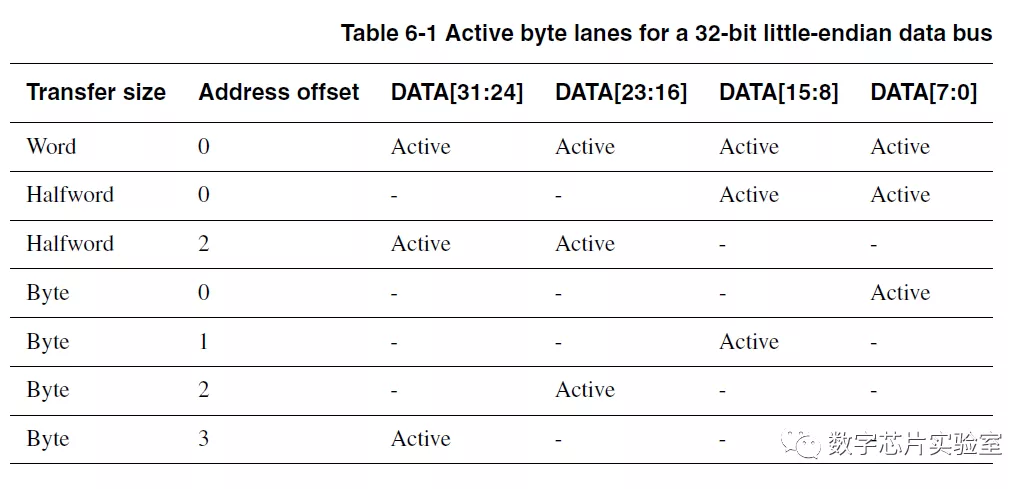

下表分别列出了在**小端(little-endian)**系统中32位总线上有效的byte lanes。

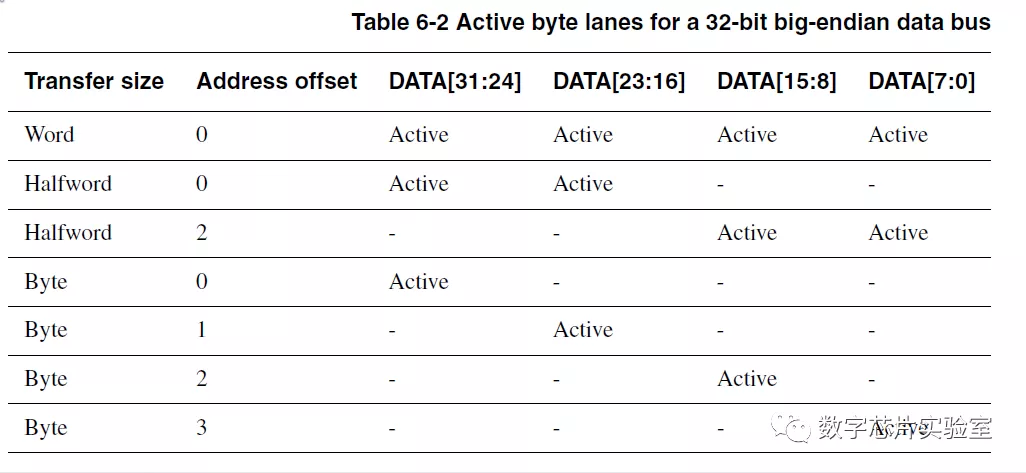

下表分别列出了在大端**(big-endian)**系统中32位总线上有效的byte lanes。

对于传输数据宽度小于总线宽度的Burst传输,每个节拍(beat),具有不同的有效byte lanes。

Endianness

所有模块都必须具有相同的字节顺序(Endianness),以使系统正常运行。

不支持动态Endianness,因为在大多数嵌入式系统中,这导致显着的冗余硬件开销。

如果模块应用广泛,可以设计成bi-endian的,通过配置位来选择Endianness。对于更多的模块,固定的Endianness(little-endian或big-endian)具有更低功耗,更高性能接口。

Data bus width

一种在不增加操作频率的情况下改善总线带宽的方法是使用更宽的片上总线。金属层的增加和嵌入式DRAM等大型片上存储器的使用使更宽的片上总线成为可能。

指定固定的总线宽度在许多情况下不是最适合的。因此,有时候需要采用一种具有灵活总线宽度的实现方法,确保模块之间的正常通信。

AHB-Lite协议允许数据总线为8,16,32,64,128,256,512或1024位宽。但是,对于几乎所有应用,最小总线宽度32,最大总线宽度256位足够适用了。

对于读写传输,接收模块必须从总线上正确的byte lane中选择数据。

Implementing a narrow slave on a wide bus

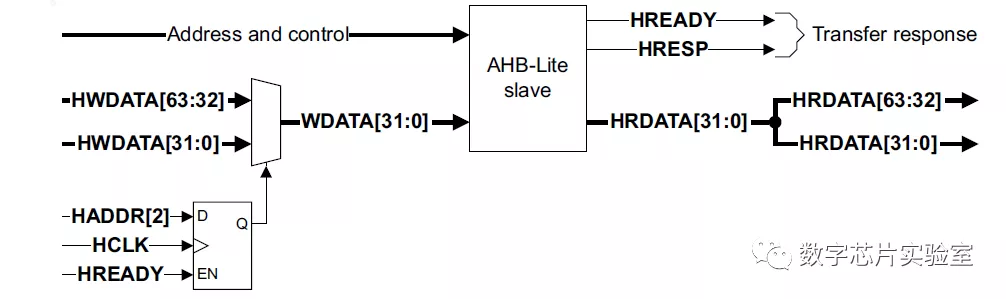

下图显示了64位总线上在实现32位slave 。只需要添加外部逻辑,而不需要任何的内部设计更改。

slave 只能接受与其相同宽度的传输。如果是master尝试传输比slave 更宽的数据,然后slave 会发出错误响应。

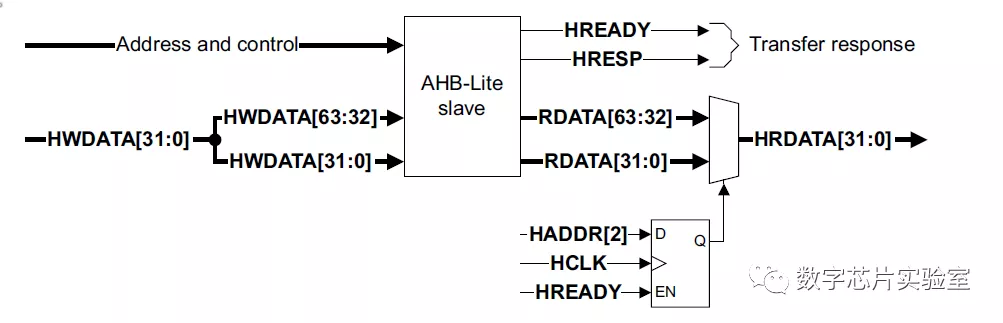

Implementing a wide slave on a narrow bus

可以通过使用外部逻辑来调整预先设计好或导入的slave以使用更窄的数据总线。

Implementing a master on a wide bus

和修改slave一样,可以修改master 以在比最初预期更宽的总线上工作。

不能让master在比原来预期的更窄的总线上工作,除非在master中实现一些机制来限制master的传输宽度,即master不得尝试在比HSIZE指定宽度窄的数据总线上进行数据传输。

本文转载自公众号:芯片数字实验室

原文链接:

https://mp.weixin.qq.com/s/YwcAHW\_YcElLiIFZuGUmcw

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏