现代 SoC 设计通常采用多个时钟,并包含多个时钟域。当数据从一个时钟域跨越到另一个时钟域时,由于异步时钟域交叉(CDC),会出现亚稳态问题的风险。

中国模拟 IC 行业目前处于追赶阶段。与数字芯片相比,国内模拟 IC 企业虽然起步较晚,但近年来发展迅速。目前国内模拟 IC 市场规模超过 1500 亿元,但国产化率不足 30%,大部分市场份额仍被德州仪器、ADI、恩智浦等国际巨头占据。

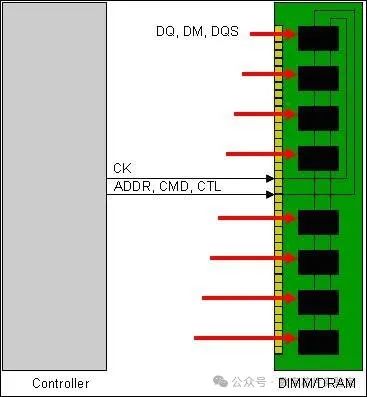

今天和大家分享一下 DDR 内存设计中一个重要的技术 - 写平衡(Write Leveling)。这项技术对于高速 DDR 内存的正常工作至关重要。

最近又听说几个老同事在找工作,有的主动出来看机会,有的是被裁了不得不找。每次聊天,都能感受到那种复杂情绪 - 明明技术硬核,简历丰富,却总是在面试环节栽跟头。

SDC 是“Synopsys Design Constraints”的缩写。SDC 是一种通用的设计约束格式,文件的扩展名是.sdc,几乎所有 Synthesis、PnR(Place and Route)和其他工具都支持。通常,设计的时序、功耗和面积约束通过 SDC 文件提供。

在后端物理实现中,boundary cell 被放置在 memory 之间,以解决与芯片设计、信号完整性和制造相关的几个问题。

对于使用第三方来源进行 SoC 设计的团队来说,半导体知识产权(IP)的质量是一个主要问题。对于高度可配置的 IP 类型来说,质量更加重要,因为客户会灵活配置它,以满足其系统和市场的独特要求。

跨时钟域(CDC)的主要问题是,当目标时钟域采样时,跨时钟域信号可能出现的 setup 和 hold violation 然后出现亚稳态,其中亚稳态可以在整个设计中传播,导致数据丢失,甚至芯片故障。

SDC 是一种行业标准格式,用于指定 ASIC 和 FPGA 设计的时序和操作约束。它对综合、静态时序分析(STA)和 place 和 routing 等各种 EDA 工具至关重要。

DRAM 不再缩放。在辉煌的年代,内存密度每 18 个月翻一番——甚至超过了逻辑。这相当于每十年密度增加 100 多倍。但在过去的十年里,缩放速度如此之慢,以至于密度只增加了 2 倍。

传统观点认为,固态硬盘SSD总有一天会取代所有硬盘,但实际上,事实证明,固态硬盘对DRAM市场来说比对硬盘市场更具挑战性。

Register Transfer Level (RTL) Signoff是一系列定义明确的要求,在IC设计和验证的RTL阶段的时候,进入下一阶段之前必须满足这些要求。下一阶段通常是综合,然后是place & route。RTL Signoff确保在流程中尽早在RTL上执行正确verify、check和fix,而不是等到后期阶段发现它们,从而导致代价高昂的返工。

低功耗和高速度带来了设计复杂性的增加。DDR5与前几代最显著的区别是引入了决策反馈均衡,这是一种用于串行链路系统来提高接收信号完整性的技术。

芯片后端技术的主要目标是将数十亿个晶体管布局在单个芯片上,以创建先进的设备和片上系统。包括数据中心、通信、消费电子、汽车、国防和工业自动化等在内的几个领域广泛依赖芯片。

CDC是Clock Domain Crossing的缩写,当芯片中有多个异步时钟域,信号从一个时钟域到另一个时钟域时,这是数字IC设计中最关键的问题之一。

在Verilog中,文件读取和写入是非常有用的。从文件中读取测试激励输入,并写入输出以供比对。 在Verilog中读取或写入文件的方法很少。如何使用readmemh函数从文件中读取十六进制值。如何使用readmemb函数从文件中读取二进制值。如何使用fopen和fdisplay写入二进制值的文件。如何使用fopen和fdisplay写入十进制值的文件。...

DFT指的是Design for Test,而DV指的是Design Verification。这两种工作都同样具有挑战性,都是芯片设计流程中的关键步骤。

SystemVerilog是一种硬件描述和验证语言,用于描述电子电路的行为和结构。它建立在Verilog的基础上,具有几个附加功能。SystemVerilog标准化为IEEE 1800,是电子设计自动化(EDA)行业广泛接受的语言。它提供了许多优势,可以使验证工程师的工作更轻松。

在直接映射cache中,当发生miss时,新请求的数据块只能映射到一条特定的cacheline。 在这种情况下,此cacheline的内容将替换为新的内存数据块。

在数字时代,DRAM(动态随机存取存储器)扮演着至关重要的角色。它们存储着我们的数据,也承载着我们的记忆。然而,要正确地操作DRAM并确保其高效运行,了解其背后的时序和操作机制是必不可少的。