SRAM是当今处理器上最普遍的内存。当芯片制造商宣布他们已经成功地将更多的电路封装到芯片上时,通常是较小的晶体管引起了人们的注意。但是连接晶体管形成电路的互连也必须收缩。IMEC的研究人员提出了一个方案,可以使SRAM保持良好的性能,并最终能够将更多的晶体管封装到集成电路中。而且还能降低导线电阻和延迟,提高SRAM的执行速度。

SRAM由6个晶体管组成,控制读写的两条连线被称为位线和字线,是两条较长的连线。长而窄的连线电阻更大,延时更长。字线和位线的电阻对SRAM运行速度的提高和工作电压的降低构成了限制。

按照传统方法来实现集成电路需要先在在硅衬底上构建晶体管,然后再在硅衬底上添加互连层,将晶体管连在一起。IMEC的方法则将SRAM单元的电源线埋在硅衬底内,然后利用节省出来的空间使关键的互连线更宽,从而降低导线电阻。在仿真中采用这种方法的SRAM存储单元的读取速度比采用传统方法的SRAM速度快31%左右,而采用新方法SRAM单元所需的写入电压比采用传统方法的SRAM存储单元要低340毫伏,这意味着更低的功率损耗。

未来几代芯片,如使用未来3纳米节点工艺制造的芯片,将需要更宽、电阻更小的位线和字线。总的来说,这些过程需要为一个特定的区域产生更多的电路。Salahuddin和IMEC团队的其他成员找到了两种方法。如果我们能从SRAM位单元中移除电源线,那么在互连层中就有了一些额外的空间。可以利用这个空间扩大位线和字线的金属轨道。

较宽的位线的电阻降低了近75%,新的字线的电阻降低了50%以上,从而提高了读取速度,降低了写入电压。

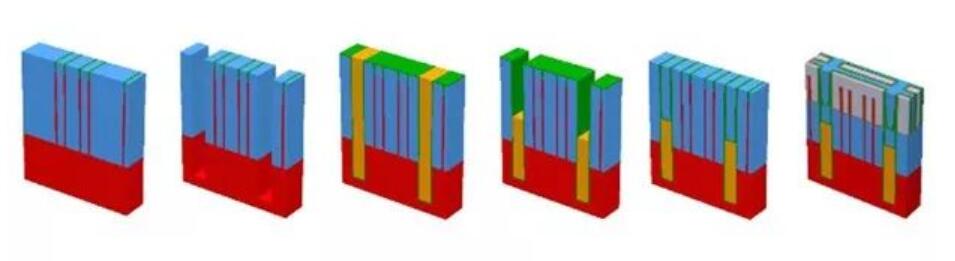

制作埋入式电源线的第一步是蚀刻形成两个沟槽的介电层[蓝色]和硅[红色]。然后在沟槽上铺上一层密封剂[绿色],然后在其中填充金属[金]。在制造FinFET栅极之前,应除去部分金属并用电介质覆盖[灰色]。

然而掩埋电线并非易事。每个SRAM单元同时接触一个高压轨和一个接地轨,这些都必须埋在晶体管散热片之间。基本上解决方法是在晶体管散热片之间蚀刻一个很深很窄的沟道,然后用钌填充。(由于铜的稳定性存在某些问题,芯片行业正转向钴或钌,以获得最窄的互连。)深而窄的沟槽很难建造。更困难的是封装钌以防止它与硅发生任何相互作用。

下一步的技术是看看它在微处理器的逻辑部分产生了什么样的收益,微处理器的几何结构远没有SRAM的规则。研究人员计划以一种可能导致更小电路的方式来扩展这项技术。这项技术被称为“背面能量传递”,涉及到使用垂直连接接触埋在地下的电源线,垂直连接从芯片背面向上延伸通过硅。这将在互连层中节省更多的空间,可能将电路所需的面积缩小15%。它还可以节省电力,因为埋在地下的铁轨与芯片电源之间的电阻路径更短、更低。