扰码是在数字传输系统中,对于数字信息进行随机化处理的一种技术,被广泛应用于通信各个领域。其作用是对数 据源发送的数字序列随机化处理,变换为近似于白噪声的数字序列。当今,扰码技术已与线路编码技术融为一体。在EPON系统传输中,需要维持系统的稳定性,保密性和高效性。

作者:Trustintruth

来源: https://zhuanlan.zhihu.com/p/86952053

首先扰码器的设计离不开移位寄存器,那么移位寄存器的设计,首先长度即移位寄存器的寄存器个数应该由输入位长决定,但是输入与输出之间的关系,例如第一位输入和第一位输出之间的关系,离不开这位之后几位的取值。而具体是几位,还是要看寄存器的个数的。

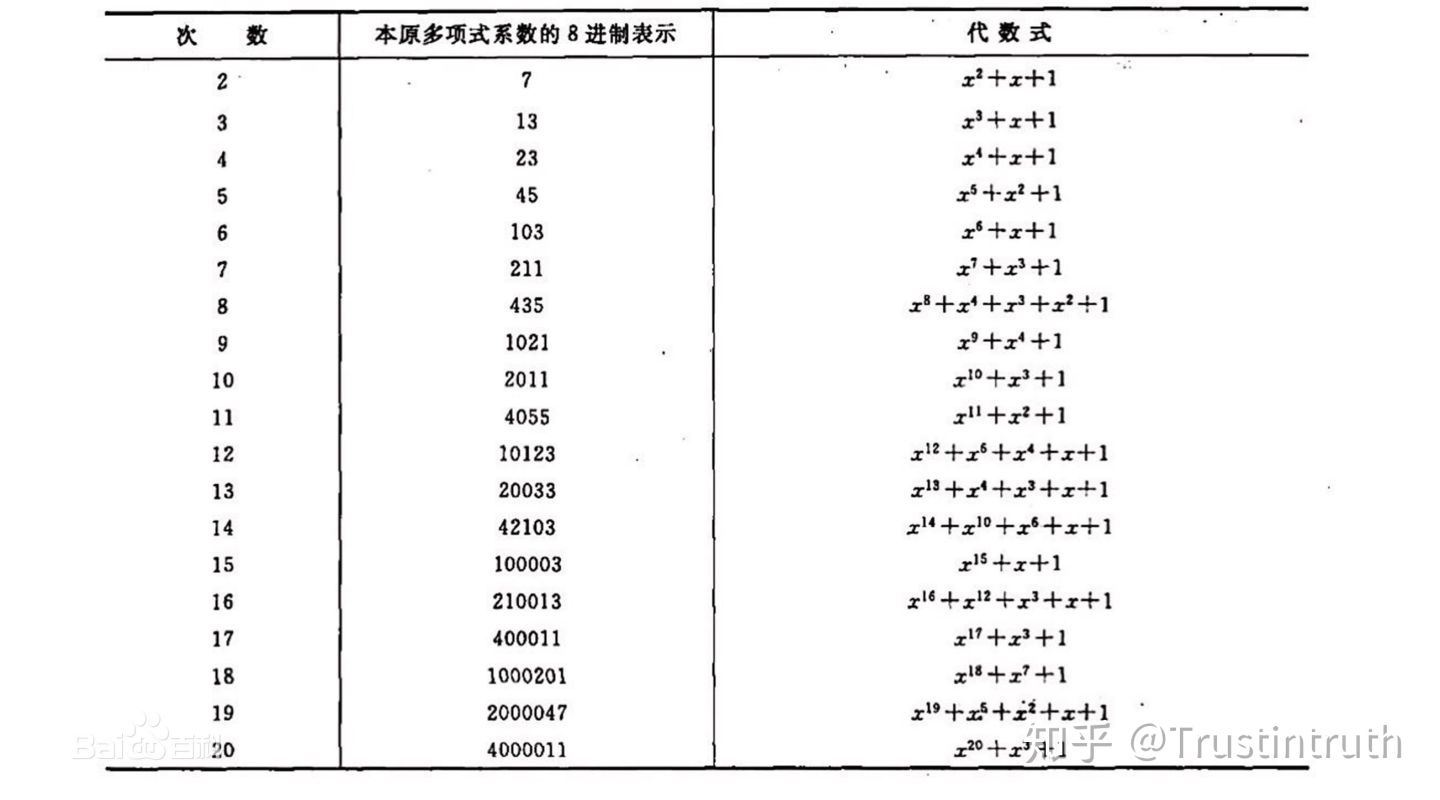

现在的疑问在于如何确定本源多项式以及如何做并行化处理。

并行化处理时将数据一次性读入8位,是不是应该同时输出8位,但是输出时需要他之后的几位该如何处理?接下来我们一点一点来解决这些问题。

扰码的目的是抑制线路码中的长连“0” 和长连“1” ,便于从线路信号中提取时钟信号。由于线路信号仅通过扰码,所以SDH的线路信号速率与SDH电口标准信号速率相一致,这样就不会增加发端激光器的光功率代价。

另外,扰码还可以将不同的终端或基站区分开来,同时,扰码还有助于提高通信的保密性。加扰不改变信号的带宽,只是将来自不同信源的信号区分开来。这样,即使多个发射机使用相同的码字扩频也不会出现问题。——摘自 百度百科

接下来就来说一说如何实现

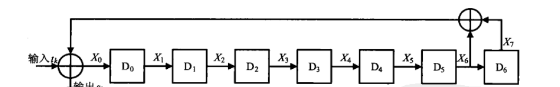

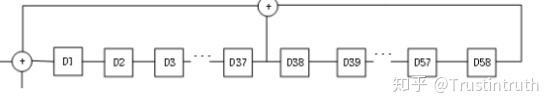

扰码产生是通过循环移位寄存器来实现的,而扰码生成多项式决定循环移位寄存器的结构。例如:

使用的扰码生成多项式: X7 + X6 + 1

则对应的循环移位寄存器应当为

实现的本质在多项式中的常数项为1的项给模二计数器输出进行模二加法运算。

有了这个图之后就很好设计我们的串行扰码器了。应用状态机控制将数据按顺序进入循环移位寄存器就好。

有些并行化的想法很幼稚,就是最一开始居然想级联几个串行扰码器来实现并行,但是扰码是一个和你前后数据息息相关的设计,拆分并行并不可取,因为他只是将串行转化成并行而已,丝毫没有速度的提升,那如何转变成为并行呢?

如果要想做扰码器,首先要知道自己的扰码器最长周期是多少位的。例如在我们的工程中,由于扰码只是其中的一个部分,他需要承接上面发送数据的格式,这样一来,根据相关标准中指定的扰码多项式选择这样的一个扰码多项式。如果单纯的去做一个扰码器可以选择其他周期较短较简单的扰码多项式。

确定扰码多项式之后,下一个工作就是设计。

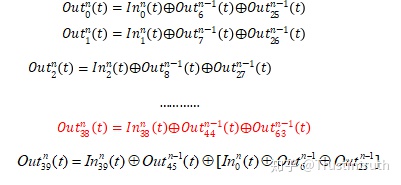

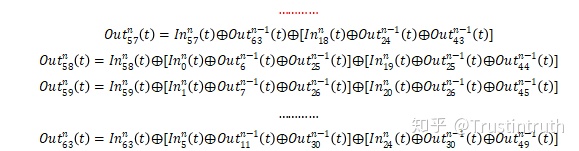

扰码的规则就是根据本原多项式系数为一的项的指数进行扰码。简单话说,扰码当前状态输出的扰码数值,是由当前状态和之前发送状态数值进行模二加法运算(异或)将结果输出。而具体是之前的那个状态呢?就是本院多项式中系数为一的项,如我们上面的例子中系数为1的项指数为39和58,那么我们就要将当前状态和前第39项与58项进行模二加法运算,算出来的值输出。示意图如下。

有些小机灵鬼可能已经发现这个图不就是是个电路图吗?没错,它确实也是一个电路图。由于扰码器每一项输出都与之前的状态有关,我们使用移位寄存器逐项存储扰码后的数据值,对应本原多项式中的系数为1的项数值与输入数值进行模二运算输出为当前数据,并将它存储进移位寄存器中供后面扰码时使用。

就这样串行扰码器就设计出来了,

在许多工程项目中,在通信接口的设计中,通信协议对于扰码器的工作频率要求非常高,但是由于串行扰码器是1bit进行的,如果再要求频率过高的话,FPGA是无法实现如此高频率的。所以我们要对其进行并行化处理,以此达到高速的要求。

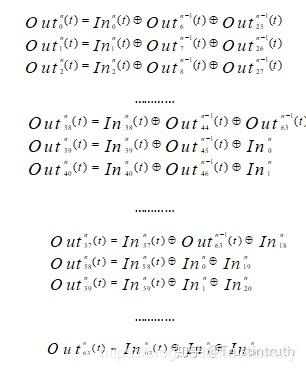

并行扰码器设计基于串行扰码器,其对应的本原多项式依然是,而其输入输出关系可以由上述扰码器输入输出的逻辑关系推导而出。按规则规范,扰码器与解扰器数据位的输入输出均为64位宽。

在上述的扰码器中,将反馈移位寄存器中零时刻存储值为为,扰码器输入与移位寄存器中数据与或的结果,即下一时刻输入至第一个寄存器的数据为,输入数据为scram\_in。表示第S为寄存器在N时刻的存储值。由扰码器的输入输出关系可推导出在下一时钟到来时,各级寄存器中存储的数值满足以下关系:

(1)

以此类推,在第39个时钟到来时,第39位寄存器寄存器中已经是,故将公式中迭代为该公式,即可进行下次运算。

并行扰码结构就是由上述扰码多项式经过严格推演并进行处理,其结果推导为下式,推导出扰码结果的每一位输出都与当前输入以及在此之前的输出相关。由于后电路的要求,每一位一个扰码输出保持到下一次的扰码操作,作为下一次扰码的前一次输出参与下一轮的扰码操作,保持了扰码的连续性。由于扰码/解扰过程与本原多项式都有关,且扰码过程中每一位的输出都与其对应的寄存器数据位有关,故扰码解码实现时必须选择相同的本原多项式和初始值。

https://blog.csdn.net/stanaryblog.csdn.net

最后我的博客也会一直更新新鲜的知识,完整代码已经上传至公共号,欢迎大家获取更多代码与资料,欢迎关注我啊!

推荐阅读

关注此系列,请关注专栏FPGA的逻辑