二、coresight的寄存器

coresight对于每个coresight组件,规定了一些寄存器,这些寄存器的偏移是固定的,这些寄存器,是必须存在的。但是有的,可以不实现该寄存器功能。

1、寄存器一览

coresight架构,对于coresight的组件,定义了若干个固定的寄存器。第一个寄存器的偏移从0xf00开始,直到0xffc。以下是寄存器列表

以上的寄存器的地址,在coresight的组件中,是不能当作其他功能使用的。如果该寄存器,在该组件没有实现,那么该寄存器地址要保留,读取要返回0,写被忽略(read must return zero, and writes must be ignored),而不能当作其他功能使用。

对于coresight的组件,占用1个4k或者整数倍的4k空间的memory空间。而coresight的寄存器,处于组件占用空间的最后一个4K空间的最后一部分。

以下是一个coresight组件占用的memory空间。占用一个4k空间。

寄存器分为两部分:

◾device-specific registers:组件自定义寄存器,从0x000-0xeff。coresight组件利用这些寄存器,实现该组件的功能。

◾coresight management registers: coresight固定的寄存器,从0xf00-0xfff。这部分寄存器的功能是固定的。

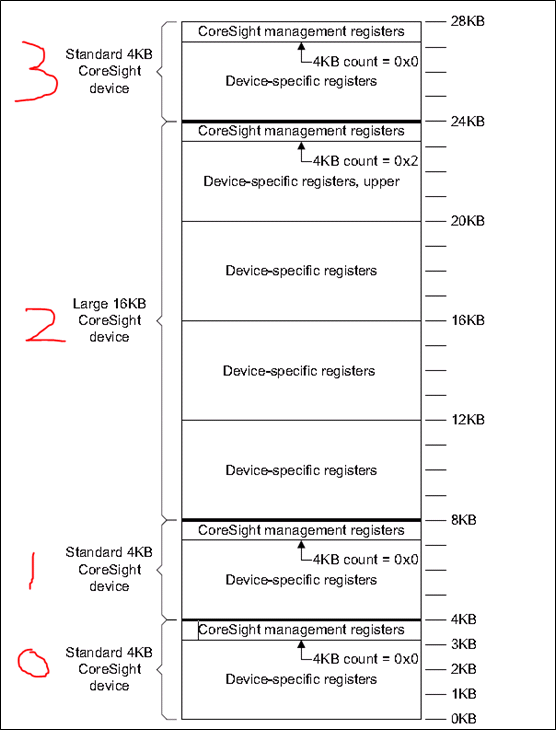

以下是包含了多个coresight组件memory分布,每个组件,占用4K空间的整数倍空间。

对于第2个组件,占用了16k的空间,但是coresight寄存器,是在最后一个空间的最后位置。

而其他3个组件,都只占用了1个4K空间。因此coresight寄存器,在这一个空间的最后位置。

2、ITCTRL,integration mode control register

工作模式寄存器。

对于每个coresight组件,可以工作在两种模式下:

◾functional mode

◾integration mode

两种模式的区别,在于对coresight组件的寄存器的访问,是否会引发寄存器相应的功能。

integration mode是用来topology detection的。当一个debugger连接到一个soc后,此时debugger是不知道soc内部有哪些coresight组件的。因此就需要通过查询,来得知soc中有哪些coresight组件的。而查询,就是通过访问coresight组件的寄存器来实现的。此时soc还不知道组件是什么组件,因此也就不知道组件的寄存器是有什么功能。因此此时是不能随意对组件的寄存器进行访问的。

为了使访问的过程中,不影响组件的功能,就可以让组件工作在integration mode下,此时访问组件的寄存器,不会引发寄存器相应的功能。待debugger查询完毕后,获取到soc中各个coresight组件的信息后,再将组件的模式切换为functional mode。

复位后,组件必须工作在functional mode下。因此外部debugger对组件查询完毕后,可以直接对组件进行复位,这样所有的组件就恢复到了function mode了。

3、CLAIM寄存器

这个寄存器是一个32位的不可见寄存器。只能通过访问CLAIMCLR和CLAIMSET这两个寄存器,来设置或者获取该寄存器的值。

该寄存器,可以用来表示该组件的状态。这个是由实现来定义的,比如可以规定,该寄存器的最低位,表示最近该寄存器被读取过,第1位,表示最近该寄存器被写过。

CLAIMCLR寄存器:

CLAIMSET寄存器

4、DEVAFF,device affinity register

组件关联功能寄存器。

有时候,组件需要和其他组件,联合起来工作,这样,就需要指示该组件是和另外的什么组件进行关联,就可以用这寄存器。

比如一个ETM,追踪一个core的trace信息,那么这个寄存器,就保存core的MPIDR寄存器信息,这样debugger就可以通过DEVAFF寄存器,得知这个ETM是关联的哪一个core。

DEVAFF0寄存器:

DEVAFF1寄存器:

5、lock 寄存器

对于coresight组件的寄存器,ARM定义了如下的一些访问方式:

可以分为两类访问:

◾系统寄存器访问:通过MSR,MRS指令(aarch64),MCR,MRC指令(aarch32)

◾external debug接口访问:DAP访问,或者是memory-mapped访问,也就是软件通过load store访问

对coresight组件寄存器的访问,是有权限要求的。对于系统寄存器访问和memory-mapped访问,ARM定义了software lock这个权限限制。当software lock有效的时候,软件是不能访问coresight组件寄存器的。

software lock的目的,是为了防止软件意外的修改coresight组件的寄存器,从而修改当前系统状态,或者获取一些不该获取的信息。可以用来防黑客。

software lock提供了两个寄存器,一个是LAR,一个是LSR。LAR是用来设置software lock状态,而LSR是保存当前的software lock的状态。

往LAR写入0xc5acce55,software lock状态切换为unlock, software可以正常访问coresight组件的寄存器,写入其他值,software lock状态切换为lock,software不可以正常访问coresight组件的寄存器(实现自定义)。

对于DAP访问,software lock是没有用的。因为要通过DAP访问,是必须要debugger连接芯片的。

所以coresight组件要能够区分,当前的访问是DAP访问,还是非DAP访问。

6、AUTHSTATUS,authentication status register

debug功能的认证接口。

debug可以分为non-invasive和invasive。non-invasive就是self-hosted,而invasive就是external debug。

实际中,可以根据不同的应用需求,可能会需要支持debug,但是也可能需要支持debug中的一种,也有可能不需要支持debug功能。因此考虑到这些需求,ARM定义了认证接口。

认证接口总共包括4个。这4个接口是每个ARM的core要实现的。这些接口是debug功能的总开关。

◾DBGEN: invasive debug enable

◾SPIDEN: secure invasive debug enable

◾SPNIDEN: secure non-invasive debug enable

◾NIDEN: non-invasive debug enable

而这个authentication status寄存器,就是保存了这4个接口信号的状态。

DBGEN使能的时候,NIDEN被忽略,即NIDEN被认为是使能。

SPIDEN使能的时候,SPNIDEN被忽略,即SPNIDEN被认为是使能。

7、DEVARCH,device architecture register

这个寄存器,标识了coresight组件的架构信息。

这里主要关心ARCHID这个位域。

8、DEVID, device configuration register

这个寄存器的功能,由实现进行定义,总共包括3个寄存器,DEVID,DEVID1,DEVID2,每个寄存器32位,只读。

DEVID寄存器:

DEVID1寄存器:

DEVID2寄存器:

9、DEVTYPE,device type identifier register

组件的具体类型信息。依靠MAJOR位域和SUB位域来表示。

以下是组合情况:

可以看出,arm对组件分成了7大类:

◾miscellaneous: 杂散类,

◾trace sink: 最终接收trace信息的组件,包括有TPIU,ETB,router。

◾trace link:trace信息传递过程中需要的中间组件,包括有router, filter, FIFO

◾trace source: 产生trace信息的master

◾debug control:debug的控制器

◾debug logic: 具有debug功能的master

◾performance monitor: 性能的检测器检测的master

10、PIDR0-PIDR7,peripheral identification registers

外设识别寄存器。

这里面,我们关心的是SIZE,和Part number。因为其他的值在一个soc中,所有的组件的值是固定的。

◾SIZE:表示这个组件,占用4k空间的块数。如果只占用一个块,那么值是0,如果占用两个块,值是1。占用的块数为 2^SIZE。

以下是SIZE对应的组件占用的大小。以及需要访问这个组件需要的地址宽度。

◾part number:组件的唯一编号。soc中有多个coresight的组件,为了较好方便的管理这些组件,给每个组件分配了唯一的编号。这个编号就保存在part number中。

对于JEP106,这个是JEDEC标准,可以查阅以下网站;

www.jedec.org

11、CIDR0-CIDR3,component identification registers

这四个寄存器,每个寄存器只有最低8位有效。这四个寄存器的组合,用来标识组件的类型。

对于ARM的组件,CIDR寄存器的有些位是固定的。比如对于CIDR0,CIDR1[3:0],CIDR2,CIDR3,是有固定值的。

CIDR1寄存器中有一个CLASS位域,用来表示组件属于哪一个类。ARM对自己的组件,也划分了若个的类。

这里,我们关心如下的class:

◾0x1: rom table

◾0x9: coresight组件。

◾0xf: corelink组件

读取组件的CIDR寄存器,即可知道这个组件是属于哪一类。

对于rom table, 固定为 0xb105_100d

对于coresight组件,固定为 0xb105_900d

对于corelink组件, 固定为 0xb105_f00d

系列其他篇

原文首发于骏的世界博客

作者:卢骏.

更多Arm技术相关的文章请关注Arm技术博客极术专栏,每日更新。