在仿真中,出现了以下奇怪的问题。

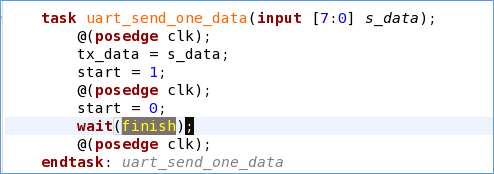

如下Tb代码,uart_send_one_data任务,发送一个数据后,要等待finish为高后,才可以发送下一个数据。

但是在实际仿真过程中,发现finish信号,并没有变高,wait语句条件就成立了,然后退出该task。又重新发送了一个数据。

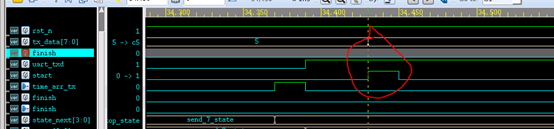

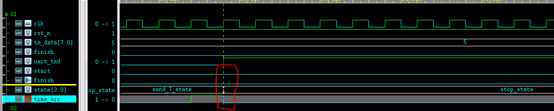

波形如下:

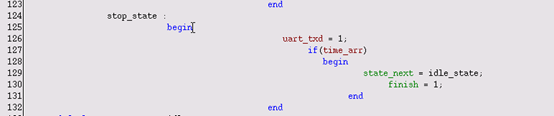

finish逻辑代码如下:

通过各种调试手段,包括单步调试,都没有找到原因。最后通过看finish信号生成的代码,发现了问题所在。

究其研究,是因为finish信号的生成,是一个组合逻辑。依赖于state状态和time_arr信号。

当state状态为stop_state状态,finish信号由time_arr决定,而在红线框这个位置,time_arr信号从高变成低。因此finish信号就有从低变高,然后从高变为低,只是这个过程太短暂,出现了上冲毛刺,因此在fsdb波形中,没有体现出来。

但是仿真工具却采集到了这个毛刺,认为finish信号,有变为高电平过,因此在tb中,wait(finish)成立,执行之后的代码。从而造成错误。如果把wait,换成@(posedge)和@(negedge),也是一样的效果。

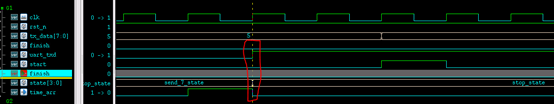

修改DUT代码,将finish输出,通过寄存器打一拍输出。上述问题消失。

从上图波形看出,修改代码后,没有毛刺信号,因为wait(finish)不成立。和预期一致。

更多相关阅读

IES low-power中的set_sim_control命令

pxp的ixcom模式,memory不能定义太大问题

sv的dvfs的时钟实现