今天有童鞋告诉我,看了我的文章对他找到工作颇有助益,让我十分开心,也坚定了继续写下去的信念。

最近大半年IC行业的招聘市场比较动荡,不少新创公司高薪挖人,加上一些原本有成熟产品的企业也开始拉队伍自研芯片,开出了不菲的offer,连带着不少一线IC大厂的offer也在水涨船高。本人也未能免俗,趟了趟已经被搅浑的水。有机会把我的一些面试经历和耳闻和大家说说,也方便大家有个参考。

因为上面的缘故和一些私事占用大量时间,近期文章的更新频率比较低。不过目前一切都趋于稳定,以后的文章更新也会慢慢变快,请大家随时关注。

今天我想和大家聊聊Noise。Noise分析又称Signal Integrity分析,它作为一个物理现象,基本只和后端和之后的环节有关,也只有(广义的)后端工程师会关注noise的以及如何去解决这些问题。

广义的noise有很多,除了后端会遇到的芯片级noise,还包括package, PCB等板级噪声。今天我们主要想说说后端在做timing signoff 时遇到的noise(噪声)问题:crosstalk。

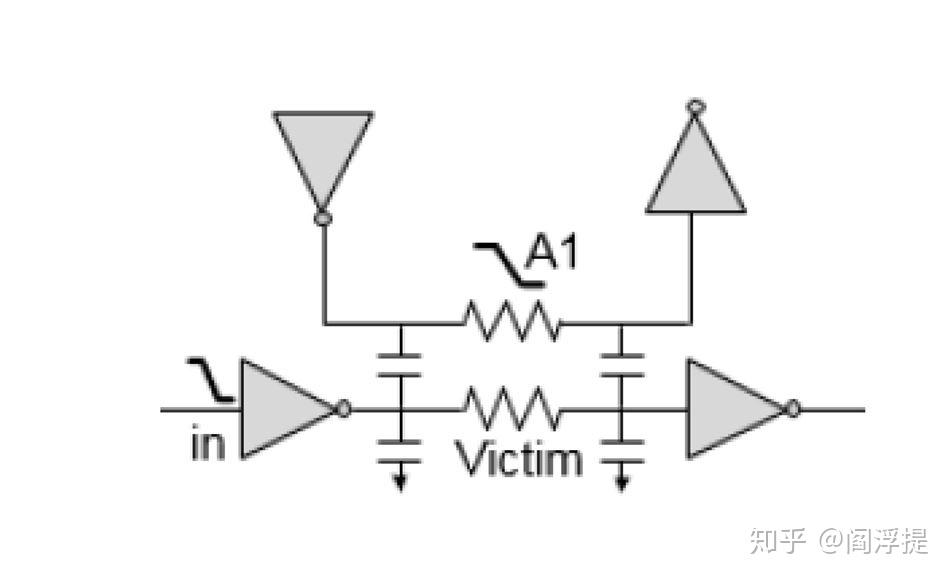

Crosstalk主要指的是下面一种现象:当两条或两条以上的net在物理上相隔较近时(如下图所示),他们之间会因为coupling capacitance而产生相互之间的信号干扰。这种干扰在最终会带来两种结果:增加delay或者产生逻辑错误。下面我们将依次详细讲解它们。

Noise示意图

- noise增加delay

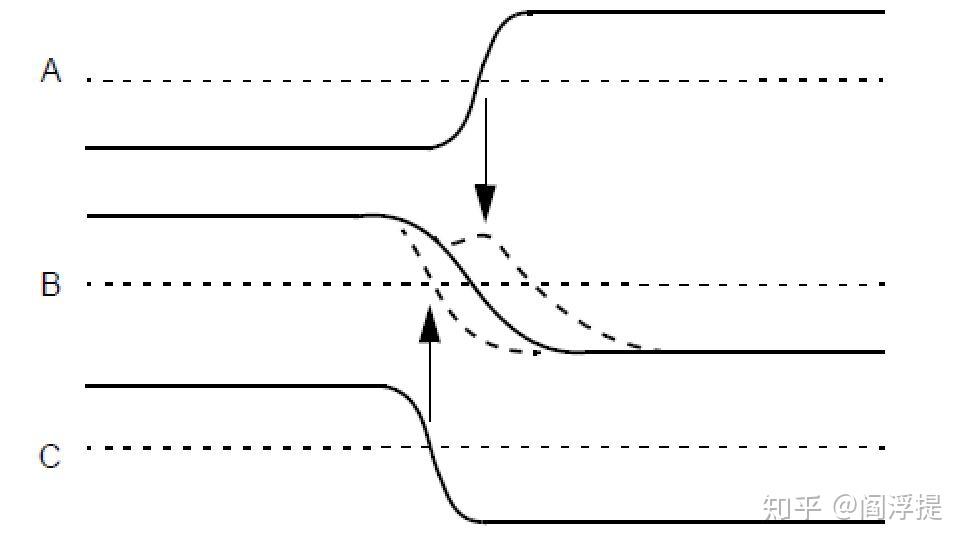

其基本原理非常简单:假设在信号B翻转之时,如果相邻net的A信号或者C信号也正在翻转且这几条线之间的coupling capacitance足够大,就会影响到B信号的翻转时间从而影响其delay。在noise分析中,被影响的信号称为victim,施加影响的信号称为aggressor。具体的示意图如下所示:

可以看到,在上图中的B(victim)信号在1-0的翻转过程,若受A(aggressor)信号0-1翻转的影响,则会增加B信号的delay,若收C(aggressor)信号1-0翻转的影响,则会减小B信号的delay。而当delay的影响足够大的时候,就会影响到时序的收敛,从而影响整个芯片的性能。尽管如此,如果时序在考虑noise的情况下仍能收敛,则这部分的noise可以无视。如果想要提高芯片的性能,则noise的改善是一个可以考虑的方向。

- noise影响逻辑功能

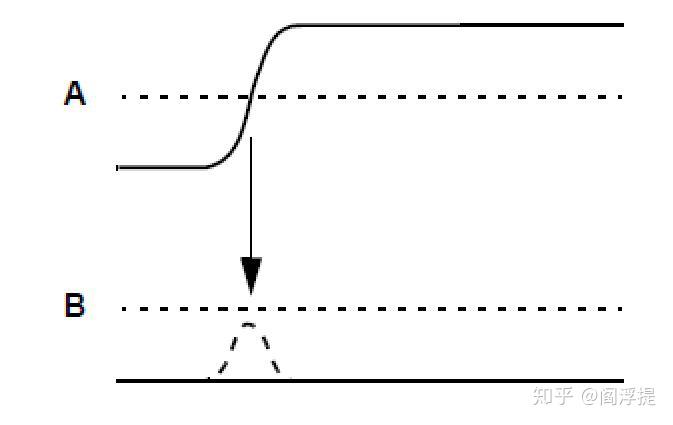

Noise除了上述delay方面的影响,还有可能引起逻辑错误,这种现象又称为glitch。其基本原理如下:

当B(victim)信号处于平稳的0状态时,相邻的A(aggressor)信号正在翻转,此时通过coupling capacitance可以使B(victim)信号出现一个小的尖峰,当这个尖峰足够高且持续时间足够长的时候,就可能被电路捕捉到被认为B变成了1,从而产生错误的逻辑结果。这种现象是STA中不能容忍的错误,因此只要出现glitch violation就需要修掉。

那么一般如何修noise violation呢?在实践中一般有以下几种方法:

降低aggressor net的driver cell size;

增加victim net的driver cell size;

增加aggressor和victim之间的间距;

为victim加shielding;

给victim net插入buffer。

对于以上方法,有疑问的同学可以留言或者加群讨论。

相关文章

如果大家有任何后端技术与职业发展方面的问题,抑或关于数字后端感兴趣的技术话题想要了解和探讨,欢迎关注我的知乎专栏: 数字IC后端设计工程师修炼之路同时欢迎关注微信公众号:数字后端芯讲堂,一起探讨技术,共同提升!

本极术专栏也会同步更新芯片设计后端的技术干货,也请关注数字IC后端设计工程师修炼之路。