Multi-Vth在当前的IC设计中使用如此广泛,以至于我们说起低功耗的设计手法时经常将其忽略。尤其是工艺进入深微亚米后,Multi-Vth基本上变为工艺的标配,不管是否为低功耗设计,多种Vth的cell混用已经成为通用做法,因此一般也很少有人强调多Vth cell在低功耗设计中的作用。

尽管如此,多Vth作为为数不多的后端可控的低功耗手段之一,有必要在此做个简单解说。

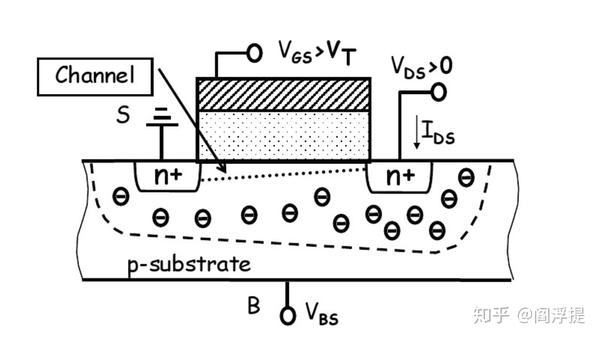

在门级电路中,任意一个门,从简单的反相器(Inverter)到复杂的锁存器(DFF),其内部都是由多个CMOS晶体管构成的。晶体管可以通过开启和关闭实现二进制0和1的逻辑,也就是现代所有电子设备的根本。关于CMOS晶体管的构造,可以参考如下截面图:

上述NMOS管可以通过在栅极(Gate,简称G端)和源极(Source,简称S端)施加电压来控制器件的开关。那么,判别晶体管是处于开启还是关闭状态的决定因素就是Vth(或Vt),也叫阈值电压。当此电压Vgs大于Vth的时候,晶体管处于开启状态,反之则处于关闭状态。

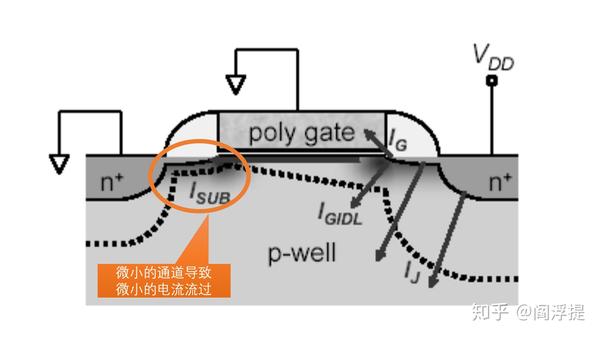

那么Vth与功耗有什么关系呢?其实实际情况是即使在晶体管关断状态下,仍然存在着极小的电流通过各个PN结在MOSFET中流通,而其中最大的一部分就是一种叫做sub-threshold的电流,在如下的MOSFET截面图中,橘黄色圆圈中标示的地方就是sub-threshold电流流过的地方:

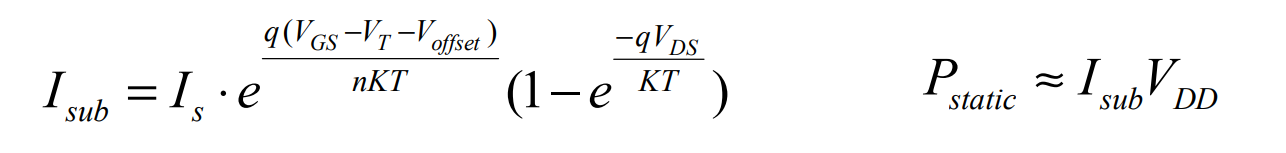

在此我们不过多地解释器件内部的所有现象以及每种现象的数学推导,但是希望大家了解,sub-threshold电流Isub和Vth存在如下关系:

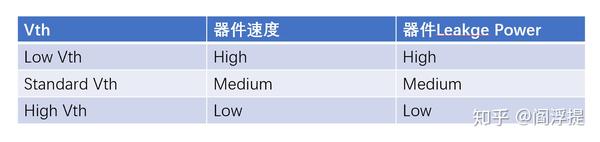

可以看出,Vth(Vt)越大,对应的Isub越小,反之Isub就越大。进一步地说,就是Vth越小,leakage power越大,Vth越大,leakage power越小。同时我们知道Vth还与器件的速度息息相关,那我们就可以总结出Vth与速度,leakage之间满足如下关系:

在此我们不讨论具体的Vth数值,因为在实际的设计过程中,所有的standard cell都是以上述3种(或再加Utra Low Vth) 时序和物理库的形式参与设计的。

在后端设计中,由于不同Vth的cell与速度和功耗由上述关系,那么反映在每条timing path上,如果design的频率较高,就需要cell delay更小,也就是需要用到很多Low Vth甚至Ultra Low Vth的cell,但是对应的leakage功耗就会上升;反之如果用了大量的High Vth的cell,就会导致cell的delay增大,虽然leakage功耗降低,但是对应的design的性能也会降低。

这种相互制约的关系给低功耗设计带来很大困难,因为我们对于设备的性能要求越来越强劲,但是对低功耗要求也越来越高,而真正实现性能和功耗的平衡是芯片设计工程师需要做的重要工作。

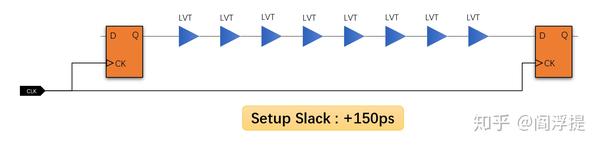

那么如何在设计中应用我们上述提到的多种Vth的组合来降低功耗呢?假设有一条timing path有如下情况:

当前path的data line上全部用了Low Vth的cell来满足时序要求,但是计算后发现setup有正150ps的slack。此时,过多的Low Vth显然消耗了多余的leakage power。因此,常见的作法就是把一部分Low Vth的cell换成Standard Vth甚至High Vth的cell,在保证setup不出现violation的前提下尽量减小LVT(low Vth)的使用量,这也是工具在做power优化的时候的常见手法。

当然这种方法只有对性能要求不太高的设计比较有效。在low power设计中,更加有效的方法是把一个或者多个模块所能使用的Vth cell种类限制在某一两种cell之中。

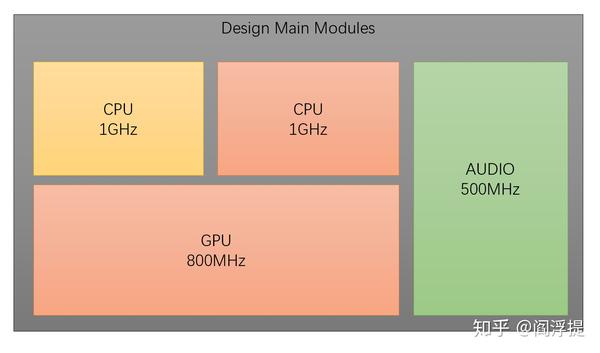

假设有如下design:

各个主要模块的频率不尽相同,CPU/GPU等性能需求高,但是音频解码AUDIO对性能要求较低,那么我们可以通过控制优化过程中AUDIO模块只允许使用High Vth cell或者Standard Vth cell来减小其整体leakage 消耗。当然这样会给设计带来额外的复杂度,有时也需要前端设计者配合优化一些timing path。

这基本上就是多种Vth cell在功耗优化种所扮演的角色。当然,针对上述多个模块对性能要求不同的design,还有更有效的低功耗手法,我们将在接下来的文章中介绍。

相关文章

如果大家有任何后端技术与职业发展方面的问题,抑或关于数字后端感兴趣的技术话题想要了解和探讨,欢迎关注我的知乎专栏: 数字IC后端设计工程师修炼之路同时欢迎关注微信公众号:数字后端芯讲堂,一起探讨技术,共同提升!

本极术专栏也会同步更新芯片设计后端的技术干货,也请关注数字IC后端设计工程师修炼之路。