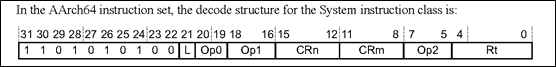

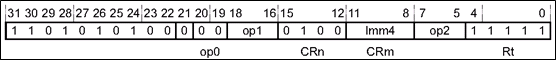

system指令,也就是sys,sysl指令,的编码如下所示:

L: 传输方向

0: 寄存器传输到系统寄存器,sys指令

1: 系统寄存器传输到寄存器,sysl指令

op0:系统指令类型

2'b00: 访问PSTATE,访问当前PE状态,hint指令,barrier指令,CLREX指令

2'b01: cache维护指令(DC),TLB维护指令(TLBI),地址转换指令(AT)

2'b10: 访问debug,trace系统寄存器

2'b11: 访问特殊功能寄存器和非debug系统寄存器

op1: 最低访问权限的EL

最低EL0访问: 值为3

最低EL1访问: 值为0,1,2

最低EL2访问: 值为4

最低EL3访问: 值为6

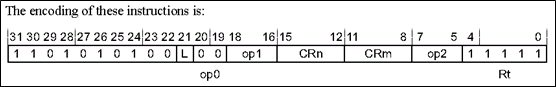

一、op0==2'b00

编码格式如下:

CRn: 指令类型

◾4'b0010 hint指令

◾4'b0011 barriers和CLREX

◾4'b0100 访问PSTATE

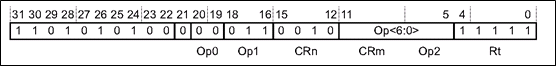

1、hint指令

编码如下,不需要寄存器参与,因此Rt固定为5'b11111。

对于Op<6:0>

◾7'b000_0000: nop

◾7'b000_0001: yield

◾7'b000_0010: wfe

◾7'b000_0011: wfi

◾7'b000_0100: sev

◾7'b000_0101: sevl

◾其他:未分配,当作nop

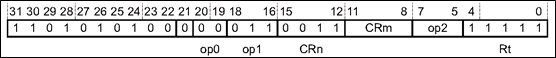

2、barriers和CLREX

编码如下,不需要寄存器参与,因此Rt固定为5'b11111。

对于op2:

◾3'b010: CLREX

◾3'b100: DSB

◾3'b101: DMB

◾3'b110: ISB

◾其他: undefined

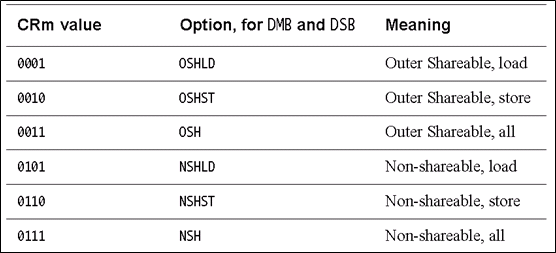

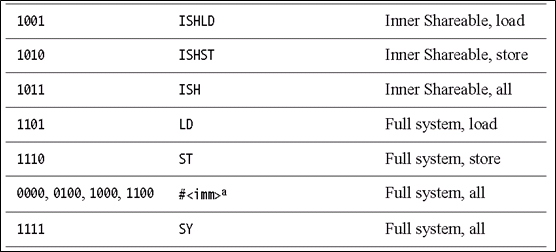

对于CRm,是指令的选项

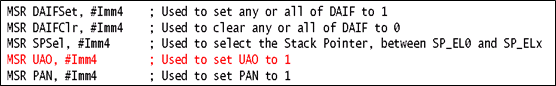

3、访问PSTATE

编码如下,不需要寄存器参与,因此Rt固定为5'b11111。

共有以下一些指令:

对于op2:

◾3'b011: MSR UAO, op1必须是0,至少EL1访问

◾3'b100: MSR PAN, op1必须是0,至少EL1访问

◾3'b101: MSR SPSEL, op1必须是0,至少EL1访问

◾3'b110: MSR DAIFSet, op1必须是3,由SRCLT_EL1.UMA配置,是否可以EL0访问

◾3'b111: MSR DAIFClr, op1必须是3,由SRCLT_EL1.UMA配置,是否可以EL0访问

二、op0==2'b01

编码格式如下:

CRn和CRm决定指令类别。

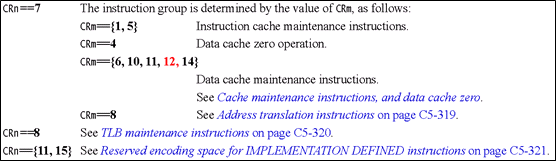

对于CRn:

7: cache维护指令和地址转换指令

对于CRm:

1,5: 指令cache维护指令

4: 数据cache清零操作

6,10,11,12,14: 数据cache维护指令

8: 地址转换指令

8: TLB维护指令

其他,设计定义。

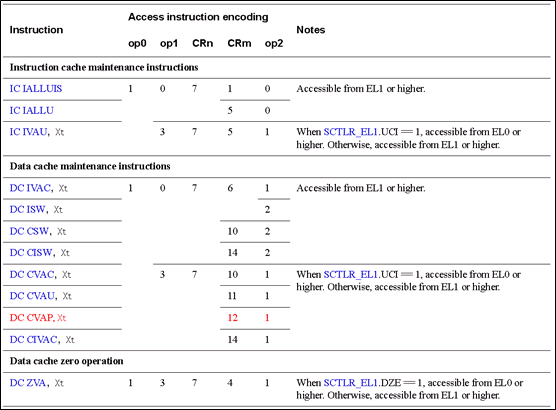

1、cache维护指令(DC)

下表,列出了编码和对应的DC指令

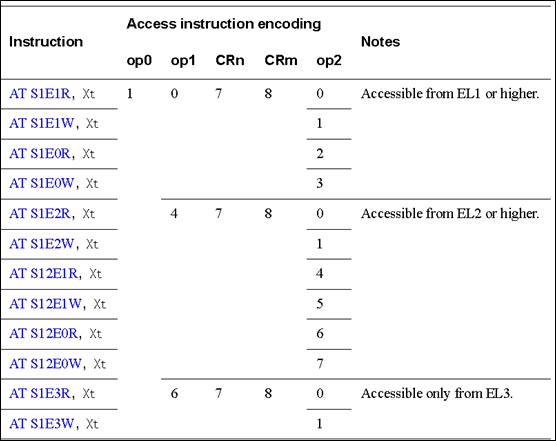

2、地址转换指令(AT)

下表,列出了编码和对应的AT指令。

AT指令,获取指定VA地址的PA地址。

对于AT指令,汇编语法为:

AT <operation>, <Xt>

<operation> 就是上表中的操作

<operation>结构为 <stage><level><read|write><stages>:

S1: stage1 转换

S12: stage1转换完后,接着stage2转换

<level>: 需要进行地址转换的EL

E0: EL0

E1: EL1

E2: EL2

E3: EL3

如果<level>是高于当前的EL,那么指令产生UNDEFINED

<read|write>,是针对于读,还是写进行地址转换

R: 读

W: 写

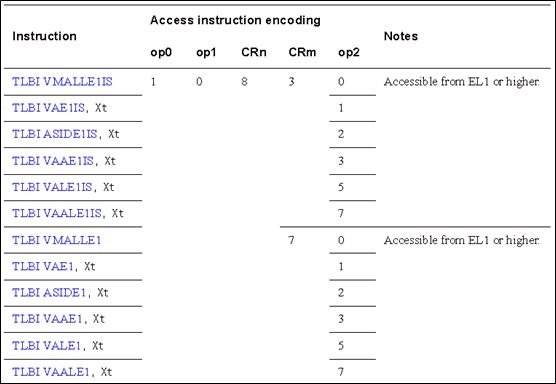

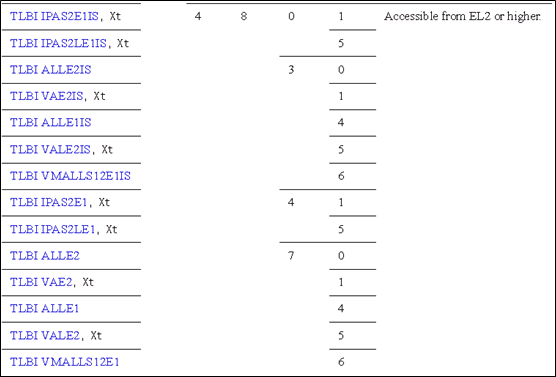

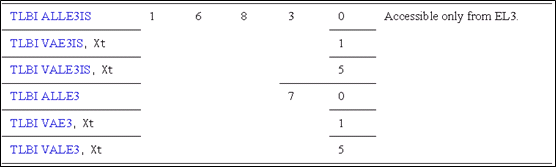

3、TLB维护指令(TLBI)

下表列出了编码和对应的TLBI指令。

TLBI指令,针对TLB操作的指令,对指定的TLB,进行invalid操作。

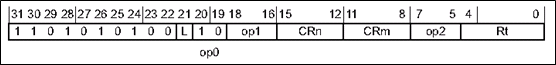

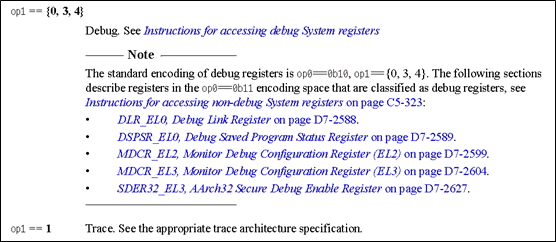

三、op0==2'b10

访问debug和trace系统寄存器

其编码格式如下:

op1的值,决定是访问debug寄存器还是trace寄存器,而CRn,CRm,op2的组合,决定了访问哪一个系统寄存器。

四、op0==2'b11

访问非debug系统寄存器和特殊功能寄存器。

编码格式如下:

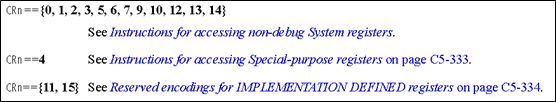

CRn,决定访问寄存器类型。

非debug寄存器,就太多了,这里就不列举了。

对于特殊功能寄存器,有以下:

系列其他篇

- [coresight(七)coresight的两大功能](https://aijishu.com/a/1060000...)

- coresight(八)soc-400套件

原文首发于骏的世界博客

作者:卢骏.

更多Arm技术相关的文章请关注Arm技术博客极术专栏,每日更新。