对于编写的systemverilog代码,在linux下,可以使用vcs编译,但是编译的时候,要注意,要加入几个选项。

整个过程,linux使用的是64位的redhat,vcs使用的是vcs2015,verdi使用的是verdi2015。

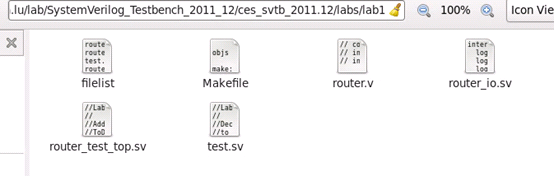

如以下的systemverilog代码。

其中router_test_top.sv是顶层的代码。

使用命令

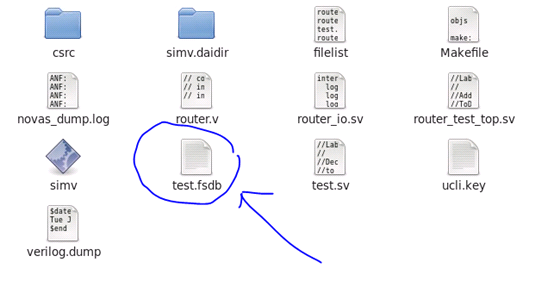

执行完毕后,就会生成 simv了。但是别忘记要执行以下simv,因为执行了,才会生成fsdb文件。

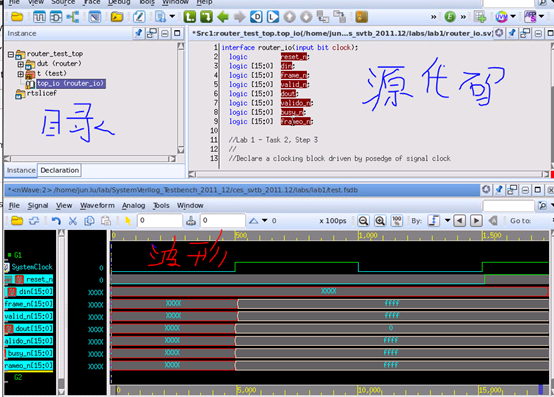

生成fsdb后,就可以用verdi打开了。

Verdi软件,需要源代码以及fsdb文件。

命令:

verdi -sv -f filelist –ssf test.fsdb

其中:

-sv: 表示 Verdi 软件 要支持systemverilog

-f filelist: 源代码的文件列表

-ssf test.fsdb: 指定fsdb文件

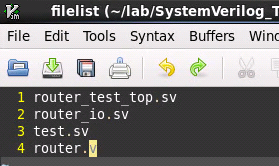

源代码的文件列表:

执行后,就启动verdi了。

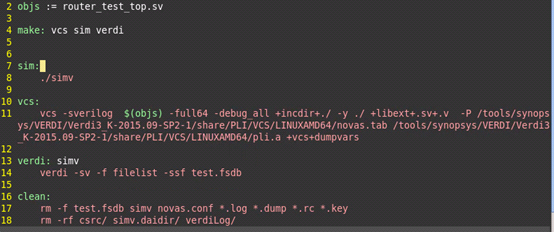

将上述的命令,封装成makefile

以后,只需要将objs的变量修改下,修改为当前设计的顶层。然后直接make命令,就可以对systemverilog代码进行编译,然后仿真,最后启动verdi查看波形。