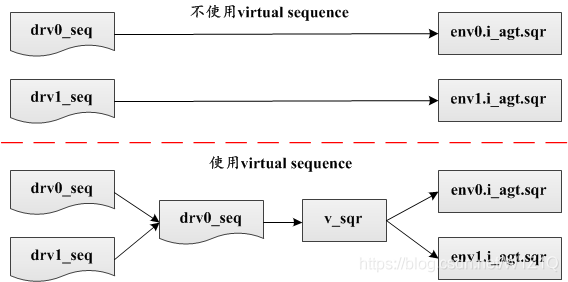

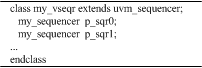

virtual sequence是用来实现sequence之间的同步。从字面上理解,即虚拟的sequence。虚拟的意思就是它根本就不发送transaction,它只是控制其他的sequence,起统一调度的作用。如图1所示,为了使用virtual sequence,一般需要一个virtual sequencer。virtual sequencer里面包含指向其他真实sequencer的指针:

图1 virtual sequence示意图

图2 代码清单

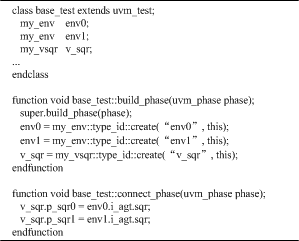

在base_test中,实例化vsqr,并将相应的sequencer赋值给vsqr中的sequencer的指针:

图3 代码清单

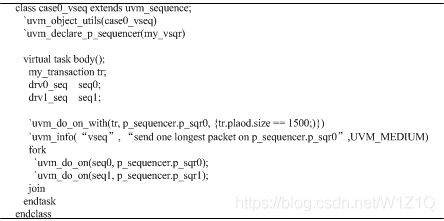

在virtual sequence中则可以使用uvm_do_on系统宏来发送transaction,uvm_do_on用于显式地指定使用哪个sequencer发送此transaction,它有两个参数,第一个是transaction的指针,第二个sequencer的指针。virtual sequence是uvm_do_on宏用得最多地方(P175-P176)

图4 代码清单

在case0_vseq中,先使用uvm_do_on_with在p_sequencer.sqr0上发送一个最长包,当其发送完毕后,再启动drv0_seq和drv1_seq。这里的drv0_seq和drv1_seq非常简单,两者之间不需要为同步做任何事情。virtual sequence的body是顺序执行,所以只需要先产生一个最长的包,产生完毕后再将其他的sequence启动起来,没有必要刻意地同步。在使用uvm_do_on宏的情况下,虽然seq0是在case0_vseq中启动,但是它最终会被交给p_sequencer.p_sqr0,也即env0.i_agt.sqr而不是v_sqr。这个就是virtual sequence和virtual sequencer中virtual的来源。它们各自并不产生transaction,而只是控制其他的sequence为相应的sequencer产生transaction。virtual sequence和virtual sequencer只是起一个调度作用。由于根本不直接产生transaction,所以virtual sequence和virtual sequencer在定义时根本无需指明要发送的transaction数据类型。

virtual sequence的使用可以减少config_db语句的使用。virtual sequence作为一种特殊的sequence,也可以在其中启动其他的virtual sequence。

另外一个需要注意的是最好只在最顶层的virtual sequence中控制objection。因为virtual sequence是起统一调度作用的,这种统一调度不只体现在transaction上,也应该体现在objection的控制上。

作者:谷公子

首发博客:https://blog.csdn.net/W1Z1Q/article/details/104358385

更多IC设计相关的文章请关注IC设计极术专栏,每日更新。