自从开启《企业存储技术》这个公众号以来,我写了不少PCIe SSD闪存组件的东西,这次也来写一篇闪存系统方面的。

应该有不少同行朋友听说了,今年的Facebook OCP峰会上有一家中国公司做了演讲,主题为“the ALL-FLASH Software Defined Storage for CLOUD”——所指的产品就是NetBRIC S5。

软件定义这个词,似乎总是和x86标准化硬件放在一起谈论,NetBRIC S5却严重淡化了CPU,而是大量使用FPGA。有点像Memblaze想在Device-based PCI闪存卡上将FPGA发挥到极致,NetBRIC搞的是一个更大的工程。

本文的目的,是希望读者能够比较全面地了解NetBRIC S5,也会简单讨论另外几款全闪存阵列的特点。还是那句话:一家之言仅供参考,水平有限欢迎批评指正!

针对云计算和互连网 只为性能和QoS的架构

在一个3U 19英寸机箱内,放480TB裸容量闪存、16个40GbE网口,最大800万8KB随机读写IOPS,而且延时只有100μs,数字确实可观。

NetBRIC S5针对的是云计算和互联网行业,因此除了性能和密度,强调的就是QoS(可以理解为资源隔离和资源分配),包括针对虚拟机/租户来设置。至于快照和复制等那些传统磁盘阵列标配的高级数据保护功能,并不是它的核心功能(注)。所谓Scale-out,是通过S5软件在主机端识别多个S5设备,实现横向扩展。

注1__:NetBRIC__表示也提供高级数据保护功能,但是是借助于现有的开源技术,并不是他们研发的主要投入。

笔者尝试先抛出几个问题:

NetBRIC S5的硬件上有没有完全的冗余设计?即每种组件都不存在单点故障?是否支持热更换?

从上图来看,电源模块是2+1冗余,风扇有2排应该可以从上面拔出,当然这只是些没有逻辑的支持组件了。

接下来,随着更多资料的列出,我还会抛出更多的问题并逐一解答。

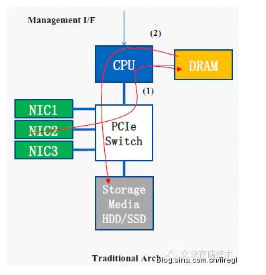

NetBRIC S5抛弃了上图中的传统Flash存储系统架构。这里描述了I/O路径的问题,即网络接口进来的数据,需要先经过PCIe Switch流进CPU控制的内存,然后再次经过PCIe Switch写入到存储介质;如果读操作就是这个路径反过来。此时CPU容易成为性能瓶颈,前提一方面是闪存足够快,同时CPU可能还要运行RAID保护、重删、压缩等数据服务,如果提供QoS也要由在CPU上运行的存储软件来处理。

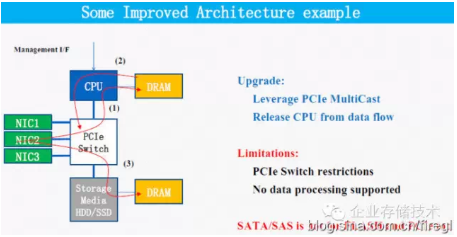

再来看看“经过一些改进的架构”——利用PCIe MultiCast(多播)来将CPU从数据流中释放出来,我理解是PCIe Switch可以为2个目标设置同样的地址,一个数据包过来CPU和存储介质上的DRAM(缓存)同时收到。这个应该只对写入有效,读的时候还是要经过CPU的。

该方案的限制,一方面是PCIe Switch——现在我了解到的单芯片最大信道数量是96,而当前的企业级PCIe/NVMe SSD基本都是x4接口(PCIe1.0/2.0时还有x8的)。还有就是数据路径中没有了数据处理支持,比如重删、压缩、全局FTL,CPU控制的内存也无法用于写缓存了。

NetBRIC还提出一个观点:“SATA/SAS不是针对FLASH(设计的),PCIe也是如此”。也就是说他们没有使用PCIe了?目的是什么呢?

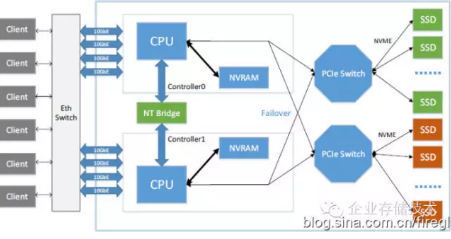

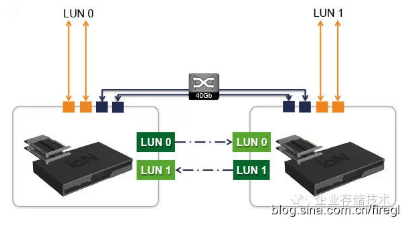

上图来自我的朋友@刘爱贵 的ppt《闪存技术与应用方法》,传统存储厂商要做一个双控闪存阵列比较容易想到的硬件架构,像Memblaze等也许会考虑这样搞吧:)(我瞎猜的)

基于PCIe Flash搞全闪存阵列,我在《破解PCIe SSD进化:从踩坑到解决方案》一文中曾经简单讨论过,有兴趣的朋友可以参考下。

在NVMe盘支持双端口之前,上图要想实现高可用只能在绿色SSD和红色SSD之间做镜像(如RAID 10)了。

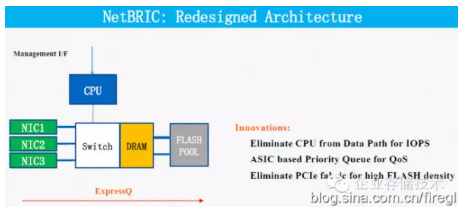

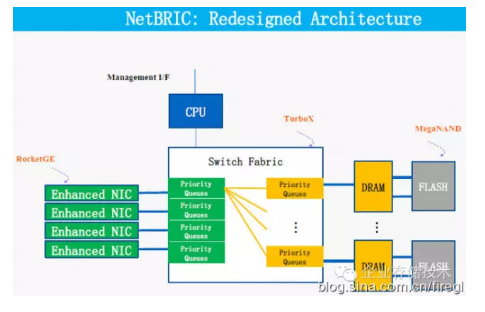

在NetBRIC的“ExpressQ”架构中,从数据路径中消除了CPU以避免其成为IOPS瓶颈,CPU在这里只负责提供管理接口;QoS是由“基于ASIC的优先级队列”来实现(在NIC板卡的FPGA芯片上);消除PCIe Fabric以达成高闪存密度。

这时我想起SanDisk的InfiniFlash闪存JBOD使用了SAS Flash模块互连,同样高密度,但性能只有78万IOPS。不知道价格上是否有竞争力?

既然Switch和DRAM做在一块PCB上,有朋友问了怎样做写缓存掉电保护?回答是和EMC XtremIO一样——靠外部的UPS。

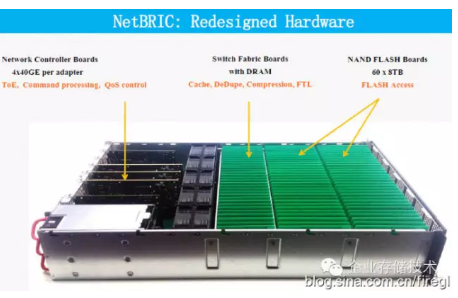

从这张图可以看出,左边的网络控制(NIC)板一共是4块四端口40GbE网卡,除了基本的主机连接功能之外,还提供ToE卸载、指令处理和QoS控制。也就是说,NetBRIC利用芯片上的资源做了更多的事情。

中间30个带有DRAM的Switch Fabric(Switch+DRAM)板,处理缓存、重复数据删除、压缩和闪存的FTL等;右边是60个8TB NAND闪存板,数据存放介质。也就是说,NAND闪存板应该不做FTL而是直接把comman dqueue形式的block读写接口暴露给Switch Fabric板。

回到本文开头提到的性能数字,平摊到每个网卡上就是200万IOPS。当几年前我看到Broadcom推出一款4端口10GbE控制器时,宣称的性能是200万IOPS,不过那很可能是512byte测试出的极限性能。NetBRIC还要用网卡上的FPGA干更多活,所以实测性能也不低了。

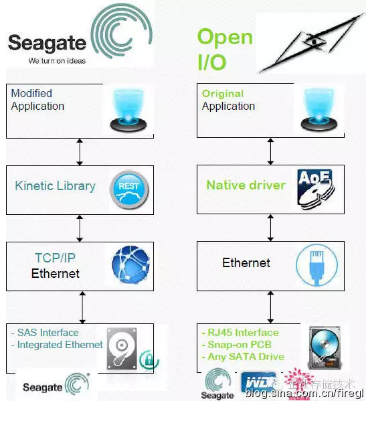

NetBRIC S5的40GbE主机接口跑的是iSCSI协议吗?答案是否定的,因为效率不够高。他们使用了类似AoE(ATA over Ethernet)的私有协议,这样就需要安装客户端驱动来访问。据了解目前提供的驱动包括主流版本Linux和KVM支持,由于面向云计算客户,OpenStack Cinder Volume Driver正在开发中,未来还考虑做VMware ESXi的驱动。

就着这个图谈谈组件的热插拔:Switch Fabric板和NAND闪存板物理和电气上应该都不难实现,只要是在打开机箱上盖的情况下;网络控制板可能麻烦点,因为还有一颗螺丝固定。尽管看上去它可能是通过PCIe物理兼容的连接器插在底板上,但整个设备内应该没有标准PCIe连接,因为对于搞芯片设计出身的周文和他的团队来说,PCIe显得厚重了,有更加简单高效的办法,而FPGA也提供这样的灵活性。

上面这张图,我在《OCP开源硬件1:以太网硬盘&存储密度》整理的ppt中曾经列出过,右边的Open I/O标准,就是用AoE原生驱动来访问以太网接口的硬盘。国外的存储系统厂商Coraid是AoE的推动者,由于不需要像iSCSI那样在IP上面跑SCSI协议,在以太网存储网络方面的性能表现更好。

上图中的绿色和黄色部分,均代表在一个板卡组件上实现的不同逻辑功能,Switch Fabric在这里指的是跨板卡互连部分。代号RocketGE的增强NIC与代号TurboX的Switch+DRAM板之间是点对点的连接,而每个Switch+DRAM向后有2个闪存通道连接MegaNAND闪存。

我还是再画一个图吧。

根据自己理解绘制的NetBRIC S5架构图(不含管理CPU)

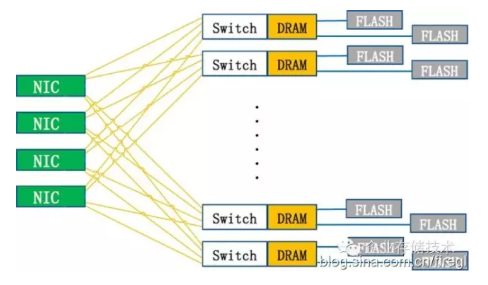

这个看上去是不是更清晰点?4个NIC与30个Switch+DRAM板之间是点对点连接,每个Switch+DRAM连接2个闪存板(共60个)。

首先,NIC与每一个Switch+DRAM之间的带宽应该不是特别大,但可以并行读写,所以负载能够平衡到每一个闪存板。

NIC在这里有点存储系统控制器的地位,为什么这样说呢?因为数据操作没有CPU参与,“网卡”要做的事情更多了。据了解,像链路聚合和负载这些只能在一块NIC板卡的4个40GbE端口之间实现。因为NIC卡本身是无状态的(没有缓存),技术上一个块设备(LUN)可以同时通过多个NIC卡映射给主机,但是因为设备本身不保证同一时间通过多个NIC卡写数据时的一致性,所以不建议这么用。

当有NIC板卡故障时,有点像是控制器的切换,这个我记得可以通过网络层(SDN)高级功能来配合;如果没有SDN,S5-client也会检测网络状态,根据网络情况进行目标NIC切换。

接着是Switch+DRAM板的单点故障情况,这意味着后面连接的2个闪存板都不可用了。NetBRIC表示采用了多副本(我理解是双副本)的机制来预防Switch+DRAM板和闪存板的故障,结合上重删和压缩一起考虑,宣称的可用容量为裸容量的1.5倍(典型情况)。那么这里至少要有一个伪随机或者Hash的算法,每个闪存板上的数据打散镜像到其它Switch+DRAM连接的闪存板上。

在4个NIC板之间,还有30个Switch+DRAM板之间,从有限的资料来看好像没有数据通道,也就是说重复数据删除等都是每个Switch+DRAM板局部在做?那么这样的数据缩减效果肯定没有EMC XtremIO的全局重删好,不过也没有了网络等方面的开销,这个到后面我会再拿图来讨论。

简析FlashSystem、Violin和XtremIO架构

接下来我们再来看看IBM FlashSystem(TMS)和Violin Memory全闪存阵列的硬件架构,各有哪些特点,NetBRIC与它们有哪些异同。

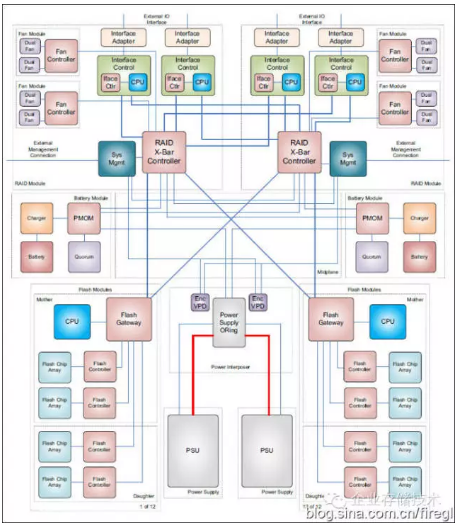

FlashSystem同样使用了大量的FPGA,从双控核心RAID X-Bar Controller到闪存模块上的Flash Gateway,再到每一颗闪存控制器… 从这个详细的架构图来看,它的主机接口模块稍显复杂,分为Interface Control和Interface Adapter两个部分。NetBRIC相当于用NIC板卡实现了主机接口和RAID X-Bar Controller两块的功能,还有QoS。当然,多副本应该要比闪存模块之间的RAID 5算法简单。

而在对应Flash Gateway的位置,NetBRIC的Switch+DRAM板还实现了缓存、重复数据删除、压缩和闪存的FTL等功能。IBM为FlashSystem增加高级软件特性的方案是配置SVC网关,这样会带来性能的损失。

无论从TMS这家老牌半导体存储厂商还是IBM来看,双控制器高可用性和可维护性方面,基本上要比NetBRIC完善。因此对于传统企业级数据中心应用而言,FlashSystem应该更加合适。

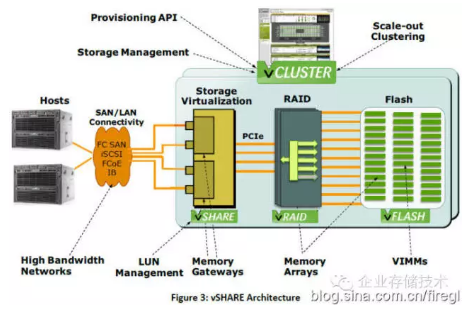

这张图有点老了,Violin Memory闪存阵列真正的控制器,应该是中间的那个深色的vRAID,它负责底层vFLASH(VIMM)闪存模块的RAID保护。如果是主机直接用PCIe连接就ok了,而FCSAN、iSCSI、FCoE和IB这些接口需要通过vSHARE存储虚拟化网关,为了获得“数据服务”,我记得他们先后与赛门铁克、飞康和DataCore有过合作。

Violin Memory 3000系列需要外置网关,6000系列以“刀片”形式内置了网关但也提供PCIe直连。惠普当年联合销售Violin Memory时推的Oracle数据库方案,就是PCIe直连VMA3210来实现更好的性能。

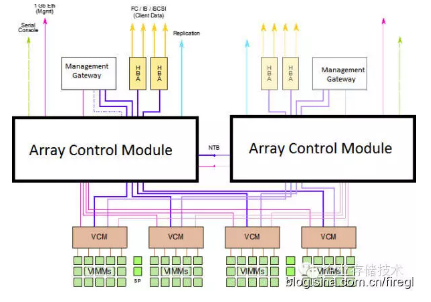

为了确认我脑子里的东西是不是有些过时,下面找到了最新的架构图看看。

这个图的VCM和Array Control Module之间,用的估计还是PCIe连接,而插在后者上面的HBA卡想来也是PCIe了。在x86阵列控制模块之间有NTB(over PCIe)连接,可以做缓存镜像,感觉比之前的存储虚拟化网关耦合紧一些,本质上变化不是太大。

论单机性能,FlashSystem和Violin Memory能达到100万IOPS左右的水平,比其他国外的Scale-up乃至部分Scale-out全闪存阵列不落下风或者处于同一水平。与以上FPGA定制化方案不同的是,现在市场占有率第一的EMC XtremIO则是x86+SAS SSD标准化硬件的代表。

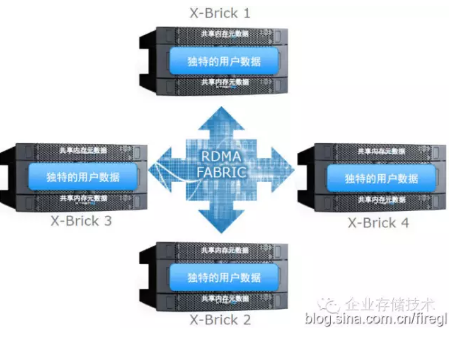

上图中XtremIO的4台X-Brick(4对控制器)通过InfiniBand RDMA高速网络互连,现在能够做到6台了。我曾看到同行朋友说:“好像单个CPU在线去重每个SSD分到数据量才40MB”(未经笔者证实),这样按25个SSD算只有1000MB/s,另一个CPU还要跑RAID和其它数据服务?

有业内专家表示:“XtremIO的重删在L1 Cache 就做了,写时代价较大,LUN LBA元数据存的强Hash,读要两次查找加分布式的转发。”

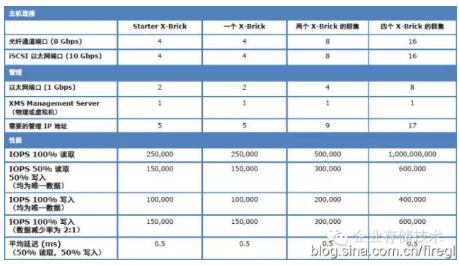

上图来自刚刚从EMC网站下载的资料

XtremIO支持丰富的软件功能,全局重删和压缩提高了可用容量;常规的快照和复制保护;听说还有很好的GUI界面易用性。可以想象如果未来从Symmetrix上移植过来的SRDF远程复制等高级特性,就可以更好地替代传统高端阵列了。而这一切的代价是,每个X-Brick的读IOPS只有25万,写IOPS10万(唯一数据)/15万(数据缩减率2:1)。

另外,共享内存元数据量限制了整个Scale-out集群的进一步扩展。为了支持更大的容量,数据切块大小已经从4KB增大到8KB。内存若加大,对用于掉电保护的UPS也会进一步增加要求。

3年前我曾经写过一篇《Fusion-io软件定义存储:全闪存阵列DIY时代?》,上面就是这款ION的架构图,简单到每台服务器插上多块PCIe闪存卡,JBOD或者软RAID 0/10之后对外映射为LUN,并利用DRBD通过40Gb以太网在两台之间同步复制,以为互备。

与ION相比,NetBRIC S5无论硬件设计还是软件的技术含量都要更高了。不过除了数据保护和QoS之外,它相对传统存储阵列的软件功能还是要“轻量级”不少,正因为这一点才实现了如此高的性能。如果用于Cache加速器,对其可靠性的要求也会降低。

总结:NetBRIC S5的机遇和挑战

如果XtremIO没有被EMC收购,料想不会有今天的发展;TMS要是没有抱上IBM的大腿,也许就一蹶不振了;曾经全闪存阵列销量第一的Violin Memory,则因为惠普终止合作推广自家3PAR而下滑明显,IPO也不过是让投资人解套而已。

一位NetBRIC的朋友曾经说,他们的产品有点像中国的Violin Memory(其实也不太像,Violin还是CPU参与IO路径的,并且是基于PCIe Switch)。尽管Violin Memory几乎一直在烧钱没有盈利过,但这与美国的人工成本和各种费用开销高有很大关系。国内的人工成本会低很多,再加上符合OCP风格的台湾代工,还是有的期待。

不支持标准主机连接协议,我觉得是把双刃剑。NetBRIC S5的目标市场,与上面列出的几家传统存储厂商不同,云计算和互联网会更看重性价比,而操作系统支持包括内核版本的广泛性要求要低一些。

NetBRIC第一步瞄准了美国市场,像Facebook这样的大客户几乎曾一手捧红过Fusion-io。当然大客户也会看重品质,所以量产和稳定性是接下来要解决的问题,这一阶段投入的成本不会小,听说资金已经不是问题了。我想对于一家做芯片出身的公司来说,可靠性等各种测试的重要性不言而喻。

五一之后很快就是EMC World大会,应该会宣布DSSD更多的消息。让我们看看有没有新的颠覆性闪存架构出现吧:)

推荐阅读

本文转载自企业存储技术微信公众号原文链接点这里注:本文只代表作者个人观点,与任何组织机构无关,如有错误和不足之处欢迎在留言中批评指正。 进一步交流技术可以加我的微信/QQ:490834312。

尊重知识,转载时请保留全文,并包括本行及如下二维码。感谢您的阅读和支持!《企业存储技术》微信公众号:HL_Storage,也欢迎关注企业存储技术极术专栏,定期更新。