UVM中启动sequence的方式有两种方式,分别为手工启动和自动启动。

第一种(手工启动):在某个component的main_phase中启动sequence,如以my_env和my_sequencer为例:

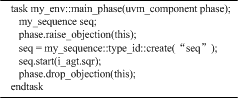

my_env:

my_env中启动代码清单

首先创建一个my_sequence的实例seq,之后调用start任务。start任务的参数是一个sequencer指针,如果不指明此指针,则sequence不知道将产生的transaction交给哪个sequencer。在UVM中,objection一般伴随着sequence,通常只在sequence出现的地方才提起和撤销objection。

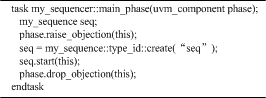

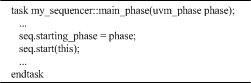

my_sequencer:

my_sequencer中启动代码清单

在my_sequencer中启动与在my_env中启动相比,唯一区别是seq.start的参数变为了this。

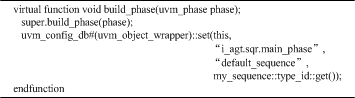

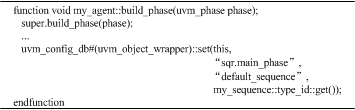

第二种(自动启动):default_sequence方式启动sequence,只需要在某个component(如my_env)的build_phase中设置如下代码即可:(最好在最顶层的class里面启动sequence,比如uvm_test类或其衍生类,即测试向量 )

set的第一个参数和第二个参数构成了sequencer的路径。由于除了main_phase外,还存在其它任务phase,如configure_phase、reset_phase等,所以必须指定是那个phase,从而使sequencer知道在哪个phase启动这个sequence。第三个和第四个参数,以及uvm_cofig_db#( uvm_object_wrapper)中为什么是uvm_object_wrapper而不是uvm_sequence或者其它,则纯粹是由于UVM的规定,用户在使用时照做即可。

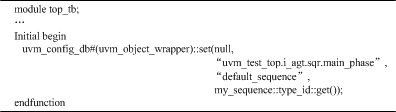

其实,除了在my_env的build_phase中设置default_sequence外,还可以在其他地方设置,比如top_tb:

这种情况下set函数的第一个参数和第二个参数应该改变一下。另外,还可以在其他的component里设置,比如my_agent的build_phase里:

只需要正确地设置set的第二个参数即可。

通常config_db都是成对出现的,有set就有相应的get。但是在这里不需要再sequencer中手工写一些get相关的代码,UVM已经做好了这些,读者无需再把时间花在这上面。

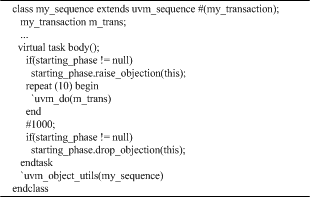

在uvm_sequence这个基类中,有一个变量名为starting_phase,它的类型是uvm_phase,sequencer在启动default_sequence时,会自动做如下相关操作,seq是sequencer中自带一个sequence类型句柄:

因此,可以在sequence中使用starting_phase进行提起和撤销objection,只有将sequence作为sequencer的某动态运行phase的default_sequence时,其starting_phase才不为null:

从而,objection完全与sequence关联在一起,在其他任何地方都不必再设置objection。

还有一种是virtual sequence启动,也是自动的,流程差不多,不多赘述。

更多相关阅读

UVM中的PHASE类别及PHASE同步

SystemVerilog与功能验证

作者:谷公子

首发博客:https://blog.csdn.net/W1Z1Q/article/details/100865789

更多IC设计相关的文章请关注IC设计极术专栏,每日更新。