UVM中通过objection机制来控制验证平台的关闭。在每个phase中,UVM会检查是否有objection被提起(raise_objection),如果有,那么等待这个objection被撤销(drop_objection)后停止仿真;如果没有,则马上结束当前phase。raise_objection语句必须在第一个消耗仿真时间的语句之前,如$display语句是不消耗仿真时间的,这些语句可以放在raise_objection之前,但是类似@(posedge top.clk)等语句是要消耗仿真时间的。当所有的phase都执行完毕后,就会调用$finish来将整个验证平台关掉。

采用run_test来启动UVM验证平台:

加参数run_test启动uvm验证平台

run_test语句会创建一个my_case0的实例,并会自动调用my_ case0的main_phase。仔细观察run_test语句,会发现传递给它的是一个字符串。UVM会根据这个字符串创建了其所代表类的一个实例(前提是这个类进行宏注册过了)。在UVM验证平台中,只要一个类使用uvm_component_utils注册且此类被实例化了,那么这个类的main_phase就会被自动调用,所以在driver中,最重要的就是实现main_phase。

UVM也提供对不加参数的run_test的支持:

不加参数run_test启动uvm验证平台

在这种情况下,UVM会利用UVM_TESTNAME从命令行中寻找测试用例的名字,创建它的实例并运行,如下所示的代码也可以启动my_case0:

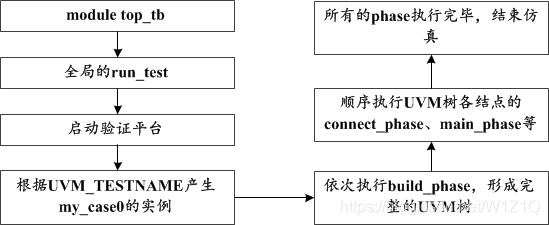

整个UVM验证平台启动及执行的流程如图所示:

测试用例启动及执行流程

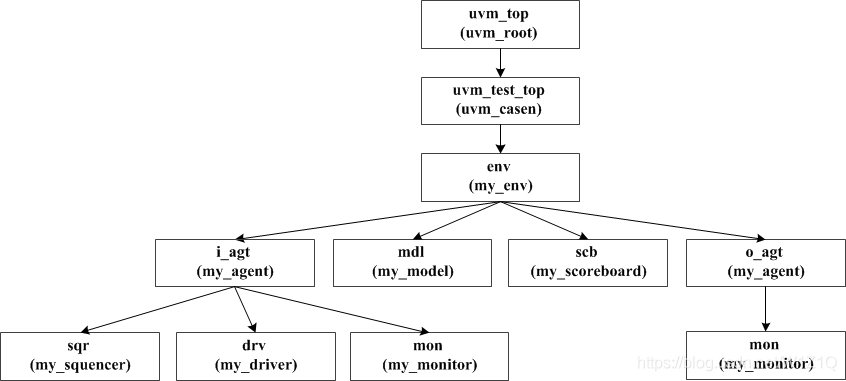

启动后,整棵UVM树的结构如图所示。完整的UVM树

uvm_top是一个全局变量,它是uvm_root的一个实例(而且也是唯一的一个实例),而uvm_root派生自uvm_component,所以uvm_top本质上是一个uvm_component,它是树的根。uvm_test_top的parent是uvm_top,而uvm_top的parent则是null。uvm_root的存在可以保证整个验证平台中只有一棵树,所有结点都是uvm_top的子节点。

更多相关阅读

芯片验证Systemverilog用例可重用方法

Makefile文件

作者:谷公子

首发博客:https://blog.csdn.net/W1Z1Q/article/details/100864767

更多IC设计相关的文章请关注IC设计极术专栏,每日更新。