转载自:知乎

首先附上传送门:

Popcount255 - HDLBits

Problem 40 Combinational for-loop: 255-bit population count

设计电路来计算输入矢量中 ’1‘ 的个数,题目要求建立一个255bit输入的矢量来判断输入中 ’1‘ 的个数。

Hint

像这种重复的工作,我们可以采用for循环来计算。

module top_module(

input [254:0] in,

output [7:0] out );

integer i;

always @ (*)

begin

out = 8'b0000_0000; //为了后面的计数累加,此处先初始化为0.

for (i=0; i<255; i++)

begin

if(in[i] == 1'b1)

out = out + 1'b1;

else

out = out + 1'b0;

end

end

endmodule

Problem 42 Generate for-loop: 100-bit binary adder 2

通过实例化100个全加器来实现一个100bit的二进制加法器。该加法器有两个100bit的输入和cin,输出为sum与cout。为了鼓励大家使用实例化来完成电路设计,我们同时需要输出每个全加器的cout。 故cout[99]标志着全加器的最终进位。

Hint

有好多加法器需要实例化,可采用实例化数组或generate语句来实现。

解析:

相当于例化100个1bit的全加器来实现100bit的带进位的加法器,我在这里偷懒了,首先想到两个always语句之间是并行的,然后就可以仅使用for循环来实现电路设计了。

考虑到for循环中只有cin与cout是变化的,每次计算中cout是本次计算的输出,也是下次计算的输入(cout就是下次计算的cin)。故我们先计算出cout[0] 和 sum[0]。

assign cout[0] = a[0] & b[0] | a[0] & cin | b[0] & cin;

assign sum[0] = a[0] ^ b[0] ^ cin;

然后开始for-loop

module top_module(

input [99:0] a, b,

input cin,

output [99:0] cout,

output [99:0] sum );

assign cout[0] = a[0] & b[0] | a[0] & cin | b[0] & cin;

//输出cout[0] == 下一次计算cin[1]

assign sum[0] = a[0] ^ b[0] ^ cin;

integer i;

always @ (*)

begin

for (i=1; i<100; i++)

begin

sum[i] = a[i] ^ b[i] ^ cout[i-1]; //这里cout[0]相当于cin[1]

end

end

always @ (*)

begin

for(i=1; i<100; i++)

begin

cout[i] = a[i] & b[i] | a[i] & cout[i-1] | b[i] & cout[i-1];

//cout[1] 等于下一次计算的输入cin[2].

end

end

endmodule

当然我的代码和题目要求是不符的,如果大家有好的代码可在评论区上传。

Problem 42 Generate for-loop: 100-digit BCD adder

本题已经提供了一个名为bcd\_fadd的BCD一位全加器,他会添加两个BCD码和一个cin,并产生一个cout和sum。

module bcd_fadd {

input [3:0] a,

input [3:0] b,

input cin,

output cout,

output [3:0] sum );

我们需要实例化100个bcd\_fadd来实现100位的BCD进位加法器。该加法器应包含两个100bit的BCD码(包含在400bit的矢量中)和一个cin, 输出产生sum 和 cout。

Hint

实例化数组和generate语句在这里很有用。

解析:

在本题中我们采用generate语句,什么是generate语句?

生成语句可以动态的生成verilog代码,当对矢量中的多个位进行重复操作时,或者当进行多个模块的实例引用的重复操作时,或者根据参数的定义来确定程序中是否应该包含某段Verilog代码的时候,使用生成语句能大大简化程序的编写过程。

使用关键字generate 与 endgenerate来指定范围。generate语句有generate-for、generate-if、generate-case三种语句,本题中我们使用generate-for语句。

generate-for语句:

(1) 必须有genvar关键字定义for语句的变量。

(2)for语句的内容必须加begin和end(即使就一句)。

(3)for语句必须有个名字。

例:

//创建一个2进制转换器

Module gray2bin

#(parameter SIZE = 8)

(

input [SIZE-1:0] gray,

output [SIZE-1:0] bin

)

Genvar gi; //在generate语句中采用genvar声明

generate

for (gi=0; gi<SIZE; gi=gi+1)

begin : genbit //for语句必须有名字

assign bin[i] = ^gray[SIZE-1:gi];

end

endgenerate

endmodule

//但是看Verilog Pro上写generate-for语句中,generate与endgenerate是可有可无的。

Verilog Generate Configurable RTL Designs - Verilog Pro

解析:

module top_module(

input [399:0] a, b,

input cin,

output cout,

output [399:0] sum );

wire [399:0] cout_temp;

genvar i;

bcd_fadd inst1_bcd_fadd (

.a(a[3:0]),

.b(b[3:0]),

.cin(cin),

.cout(cout_temp[0]),

.sum(sum[3:0])

);

//与上题同理,还是先计算cout[0],我声明一个wire型的cout_temp来存放每次计算后cout的值。

generate

for(i=4; i<400; i=i+4)

begin: bcd

bcd_fadd inst_bcd_fadd(

.a(a[i+3:i]),

.b(b[i+3:i]),

.cin(cout_temp[i-4]), //上次计算输出的cout

.cout(cout_temp[i]), //本次计算输出的cout,在下次计算中变为cin

.sum(sum[i+3:i])

);

end

endgenerate

assign cout = cout_temp[396];

endmodule

Problem 43 Wire

实现如下电路:

解析:一个简单的wire型输出,直接assign即可

module top_module (

input in,

output out);

assign out = in;

endmodule

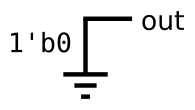

Problem 44 GND

实现如下电路:

解析: 接地

module top_module (

output out);

assign out = 1'b0;

endmodule

推荐阅读

- HDLBits:在线学习Verilog(八 · Problem 35-39)

- HDLBits:在线学习Verilog(七 · Problem 30-34)

- HDLBits:在线学习Verilog(六 · Problem 25-29)

关注此系列,请关注专栏FPGA的逻辑