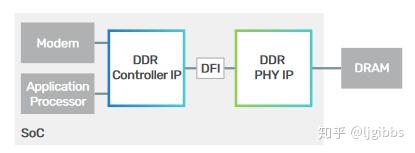

转载自:知乎DDR 是 SOC 的重要组成部分之一,随着 DDR 的速度不断提升,DDR 模块的设计难度也随之增大。目前 IC 设计公司一般从第三方购买 DDR IP。下图是一个典型的 SoC 系统的 DDR 部分,DDR 模块一般包括控制器与 PHY 两部分,其间通过标准的 DFI 总线连接。

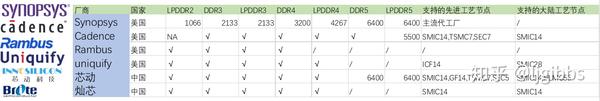

本文整理了各公司官网的产品信息,一图了解目前(2020年)主要的 DDR IP 供应商。

参考资料

Synopsys

DesignWare DDR IP Solutions :

https://www.synopsys.com/designware-ip/interface-ip/ddr.html

Rambus

接口 IP :

https://www.rambus.com/%e6%8e%a5%e5%8f%a3-ip/?lang=zh-hans

Cadance

DDR/LPDDR PHY IP:

https://ip.cadence.com/ipportfolio/ip-portfolio-overview/memory-ip/ddr-lpddr/ddr-phy-ip

Denali High-Speed DDR PHY IP for SMIC:

https://ip.cadence.com/uploads/1269/denali-high-speed-ddr-phy-ip-for-smic-pdf

Uniquify

DDR Memory IP Product Brochure

https://www.uniquify.com/wp-content/uploads/2020/08/Uniquify\_DDR\_brochure.pdf

芯动科技

据官方介绍,芯动科技DDR5/4 / LPDDR5/4 PHY&Controller全套高性能内存接口解决方案,可提供4200Mbps速率的DDR4/LPDDR4和6.4Gbps速率的DDR5/LPDDR5。同时支持定制延展DDR5/LPDDR5高端解决方案,支持全定制硬核和SI封装方案、一站式PHY&Controller 封装和PCB、PI/SI全套,为国内芯片设计提供了高性能、低功耗、小尺寸、可扩展设计的最佳国产方案,同时性能量产上也不输国外。

2020 年,芯动科技(Innosilicon)宣布,基于中芯国际14nm工艺的多款高性能国产自主可控高速接口IP(DDR/MIPI/)在国内主流客户SOC产品上,一次验证成功,进入商用量产。本次进入量产投片的高速接口IP,包括MIPI DSI&CSI /LVDS combo IP、DDR4/3/LPDDR4/3 combo 等通用 IP。(http://www.innosilicon.com.cn/news/31.html)

灿芯半导体

总部为中国上海的芯片定制设计与 IP 公司灿芯半导体在 2015 年宣布获得 Uniquify 的DDR架构技术授权。该授权为灿芯半导体提供经过验证的DDR设计架构技术,灿芯半导体可以基于中芯国际40纳米和28纳米工艺为客户开发先进的DDR解决方案。

该技术授权不仅包括Uniquify的DDR控制器(controller), PHY和I/O,而且包括特别开发的调试和测试软件。这些技术已经经过大量的产品验证,支持基于40纳米、28纳米和14纳米工艺下的LPDDR2、 DDR3、LPDDR3、DDR4和LPDDR4应用。

官网新闻链接:http://www.britesemi.com/zh/news/488024.htm

在随后的 2016 年,灿芯半导体宣布其DDR4 IP在中芯国际 40 纳米工艺上实现了2400 Mbps速率,并宣布其可实现3200 Mbps传输速率的28纳米DDR/LPDDR4将会很快通过流片验证。(http://www.britesemi.com/zh/news/496621.htm)

2018 年,灿芯宣布推出基于SMIC40LL工艺的第二代DDR低功耗物理层IP,该IP与第一代的低功耗DDR PHY相比面积减少20%, 功耗减少37%,物理实现时间减少50%。支持 DDR3/3L/3U/LPDDR3 1333Mbps, DDR2/LPDDR2 1066Mbps。(http://www.britesemi.com/zh/news/563402.htm)

2020 年,灿芯宣布为一家著名的NVDIMM供应商提供完整的NVDIMM控制器芯片解决方案。灿芯半导体提供DDR4控制器/PHY解决方案可以支持3DS、RCD (寄存器时钟驱动器)、DB (数据缓冲器)、ONFI 4.1控制器/PHY、ECC(BCH / LDPC)、加密(AES-XTS / TRNG)和低功耗MCU,可帮助NVDIMM供应商缩减芯片上市时间。(http://www.britesemi.com/zh/news/618680.htm)

推荐阅读

关注此系列,请关注专栏FPGA的逻辑