【嘉德点评】华为发明的卷积运算芯片,能够在提高阵列资源利用率的同时降低RAM访问次数,进而减小RAM的访问压力。

集微网消息,目前,深度神经网络技术已经成为人工智能领域的代表性算法,基于深度神经网络技术的字符识别、图像分类或语音识别等关键技术,已经广泛应用于搜索引擎和智能手机等产品中。

其中,当前最为有效且应用最为广泛的神经网络算法是卷积神经网络算法,简称“卷积运算”。在现有技术中,CNN算法的核心计算单元是乘加运算,乘法累加器阵列常用于矩阵乘法运算,而卷积运算可以转换为矩阵乘法运算。因此业界广泛采用MAC(乘累加器)阵列为计算核心的专用加速硬件,例如:现场可编程门阵列(FPGA)、专用集成电路(ASIC)等,以加速卷积运算的运算速度。

但是目前卷积计算也存在着一些问题,一方面,当MAC阵列中存在多个卷积窗口同时进行卷积运算时,这些卷积窗口分布在MAC阵列中的不同位置,使得MAC阵列的利用率非常低。另一方面,存在大量重复数据被从RAM输入到MAC阵列,这样会增加RAM的访问次数。

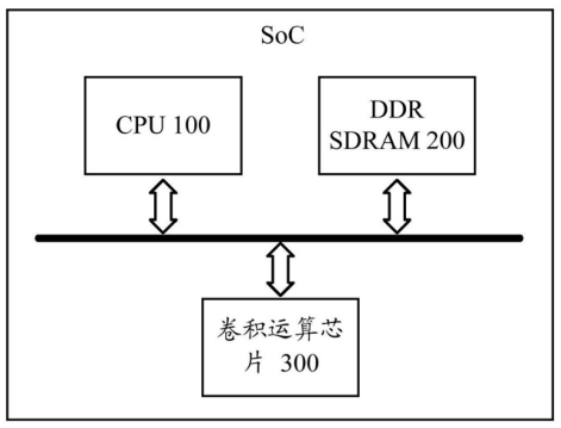

为了解决这样的问题,华为发明了将CPU、RAM和卷积运算芯片集成在同一数据总线上的AI芯片,2016年12月29日,华为发明了一项名为“卷积运算芯片和通信设备”的发明专利(申请号:201611243272.X),申请人为华为机器有限公司。

根据该专利目前公开的资料,让我们一起来看看华为的这项新架构AI芯片吧。

如上图,为该专利中发明的硬件设备的示意性框架图,硬件架构中包括中央处理器100、双倍速率同步动态随机存储器(DDR SDRAM)200以及卷积运算芯片300。CPU用来控制卷积运算芯片启动卷积运算,DDR SDRAM用于向卷积运算芯片的数据缓存模块输入多个卷积数据和多个卷积参数,然后卷积运算芯片根据这些数据来完成卷积运算。

当得到运算结果后,就会将运算结果写回到DDR SDRAM事先设定好的内存地址中,并同时通知CPU完成运算,以从内存地址中提取结果数据。

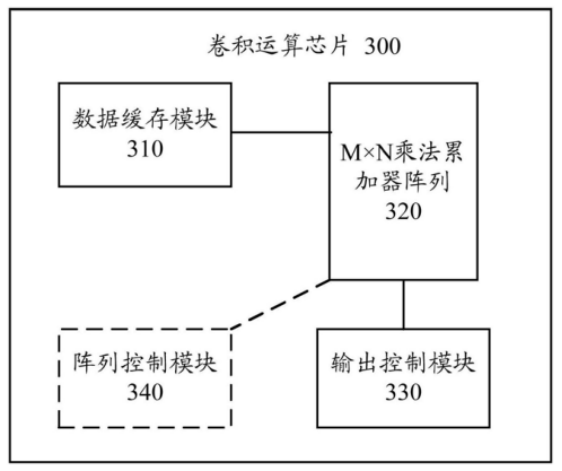

如上图,为上面框架中的卷积运算芯片的结构示意图,这种卷积运算芯片包括数据缓存模块310、M*N乘法累加器阵列320、输出控制模块330和阵列控制模块340。

数据缓存模块用于向乘法累加器中的第一乘法累加窗口传输用于卷积运算的多个卷积数据和卷积参数,卷积参数由数据缓存模块根据第一卷积参数矩阵确定,而该控制器也是通过在运算器内集成这样的数据缓存器,从而减少了RAM的访问次数,进而减少了RAM的访问压力。

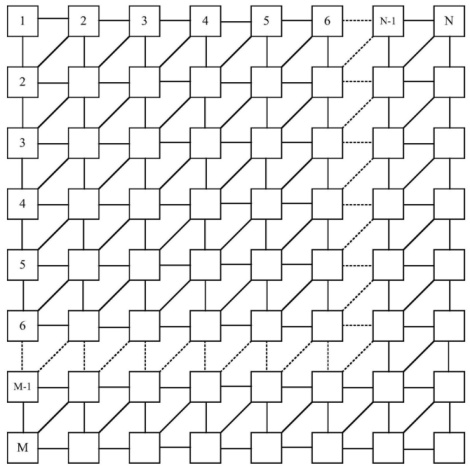

其中MN乘法累加器是该运算芯片的核心运算部件,而这种MN的结构设计方式也是为了进行卷积运算而特意设计的,其具体结构如下图所示。

可以看到,这种乘法累加器包括M*N个处理单元,并且每两行的处理单元之间还存在斜向的数据传输通道,这相比于传统的矩阵式数据传输通道,具有更加灵活的数据传输方式,可以更好的适用于AI芯片进行多种类型的运算。

第一乘法累加窗口可以将数据进行乘法运算,并接着进行加法运算以获得卷积结果,最后由输出控制模块输出卷积神经网络的运算结果,进而完成AI芯片中的任务。

值得一提的是,在该专利中,为了尽可能地提高MAC阵列的利用率以及卷积运算效率,阵列控制模块会根据第一卷积参数矩阵的行数和第一卷积数据阵列的行数来确定第一乘法累加窗口的列数。

以上就是华为发明的卷积运算芯片,这种卷积运算芯片能够在提高阵列资源利用率的同时降低RAM访问次数,进而减小RAM的访问压力。而例如华为发明的昇腾AI芯片也正是基于这样的技术之上,才能实现极高的算力,不管多么复杂的模型都可以轻松训练,且实现极低的功耗。

关于嘉德

深圳市嘉德知识产权服务有限公司由曾在华为等世界500强企业工作多年的知识产权专家、律师、专利代理人组成,熟悉中欧美知识产权法律理论和实务,在全球知识产权申请、布局、诉讼、许可谈判、交易、运营、标准专利协同创造、专利池建设、展会知识产权、跨境电商知识产权、知识产权海关保护等方面拥有丰富的经验。

(校对/holly)