最近几年,一方面由于工艺突飞猛进,另一方面由于应用市场的欣欣向荣,使得IC设计的规模越来越大,逻辑功能越来越复杂,在这样的背景下,作为『游戏运行平台』的EDA工具,必须予以革新,才能应对。

应用市场的繁荣会给数字电路设计实现带来的挑战:近几年被追捧的热点技术,从AI/ML 到IOT 到汽车电子到Cloud datacenter 到 5G, 可谓百花齐放。抛开概念本身,每一个热点背后,都有其独特的『设计特性』,而这每一个『设计特性』都会给设计实现带来挑战:

- AI/ML, Cloud datacenter 和5G 都属于运算逻辑复杂且设计规模巨大设计,对这类设计,要求工具不仅要有大的胃口而且要有极好的消化能力,大的胃口意味着可以处理更大的设计,好的消化能力意味着更优的逻辑优化能力;此外这三类大多都是congestion 敏感的设计,而且基本都会用新工艺,这对physical aware synthesis 提出了新挑战,需要工具从综合开始就去优化congestion, 就去考虑placement 跟elary global routing, 以保证前后端的一致性。

- AI除了运算复杂,congestion 敏感之外,还需要追求极致的效能比,这就要求在满足performance 的基础上,尽量的去优化面积跟功耗。

- IOT 是对功耗要求极其严苛的设计,通常都会有复杂的power domain 划分,而且要求工具对功耗进行极致优化;

- 汽车电子因为安全性的要求,使得整个设计规则都很特别,要求工具在一套新规则里畅游。

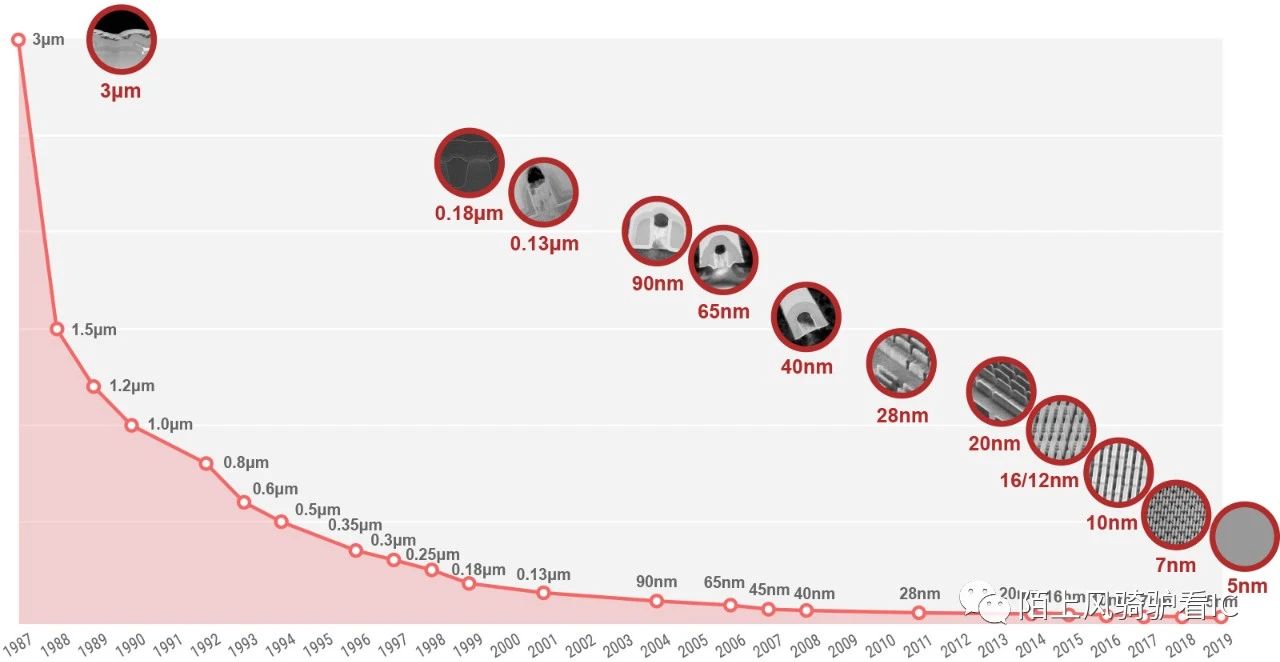

工艺发展带来的挑战:

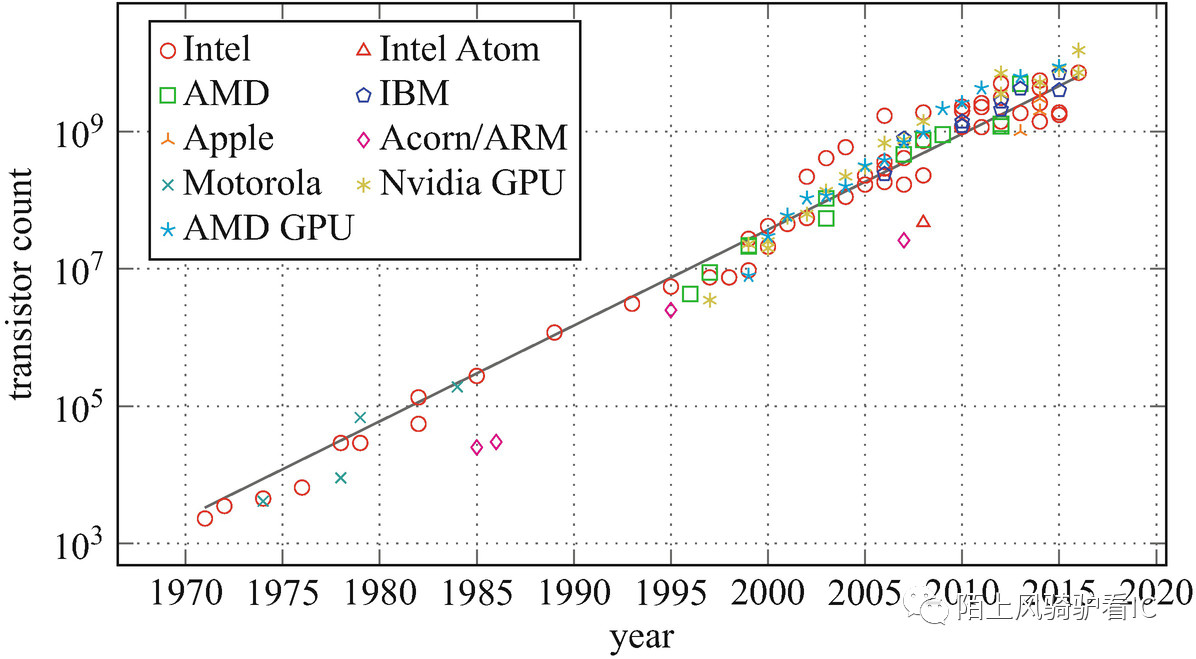

- 15年开始进入FinFet 时代,从16nm开始,期间出现过10nm, 12nm, 7nm, 6nm 到今天已经有5nm 芯片问世,明年也许就可以看到3nm 的芯片,工艺飞速发展使得设计可以以更低的功耗跑到更高的频率,并可以在更小的芯片上集成更多的逻辑,据报道在2019 年已有单颗芯片上超过50亿个晶体管的设计。

- 工艺发展犹如猛虎插翅鞭笞着EDA, EDA人需要一路狂奔,以跟上工艺的步伐。工艺进步带来的诸多好处背后需要EDA工具去模拟并弥合各种『寄生效应、工艺偏差、设计规则』。

在数字实现端,EDA工具遇到的挑战可以分别划归到工具端跟方法学两部分:

在工具端:

- 要求工具本身的『容量』增大,所谓的容量增大就是可以处理更大的设计,比如之前最大可以处理1M instance 的设计,现在要能处理5~10 M instance 或更大size 的设计;

- 工具端要提升自身的处理速度,在设计规模增加之后,运行时间不能增加太多,以前全马4小时可以接受现在必须跑进2小时才行;

- 再就是针对复杂运算逻辑在优化算法上的革新,为了应对日益复杂的设计及丰富多姿的应用需求,必须在逻辑优化算法上做革新,在追求极致效能比的同时平衡PPA.

在方法学上:

- 首先是Correlation的问题,由于设计的复杂化跟寄生效应的复杂化,Corrlation 需要在Congestion 跟timing 两个纬度去衡量,传统的『物理综合』已不足以应对当前设计,必须从方法学上予以革新;

- 其次就是功耗问题,在很长一段时间动态功耗的优化主要靠clock gating 但超低功耗设计的出现要求工具对功耗做极致优化,这一需求催生了带波形文件做综合跟PR的方法, 让工具根据实际场景,做动态功耗优化;

- 最后是工艺偏差的模拟,我们看到从传统的flat OCV 到AOCV 再到SOCV, Foundry 跟EDA 一起不断的在剔除悲观度,以现有的算力尽力精确的去模拟工艺偏差。

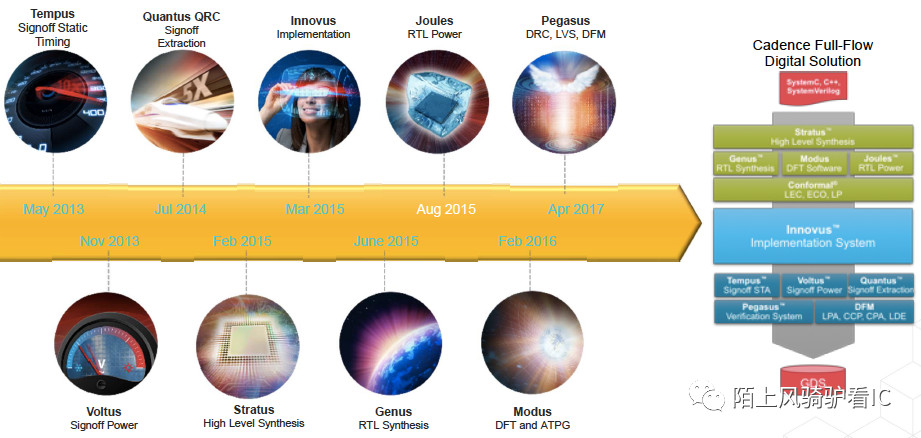

C 记为了应对前述的各种挑战,在整个数字实现端做了一系列革新,呈现给大家的就是诸多新一代工具的诞生,这所有的新一代工具的共同点是:都集成了C 记大规模并行算法,可以更快的处理更大size的设计:

- 2013 年推出新一代timing 跟power signoff 工具Tempus 和Voltus

- 2014 年推出了新一代RC 抽取工具Quantus;

- 2015 年推出新一代综合工具Genus, 新一代PNR 工具Innovus, 跟全新的RTL 功耗分析工具Joules, 以及HLS高级综合 Stratus;

- 2016年推出新一代的DFT 工具Modus;

- 2017 年推出新一代的DRC, LVS, DFM 工具Pegasus;

- 2018年推出新一代的形式验证工具SmartLEC;

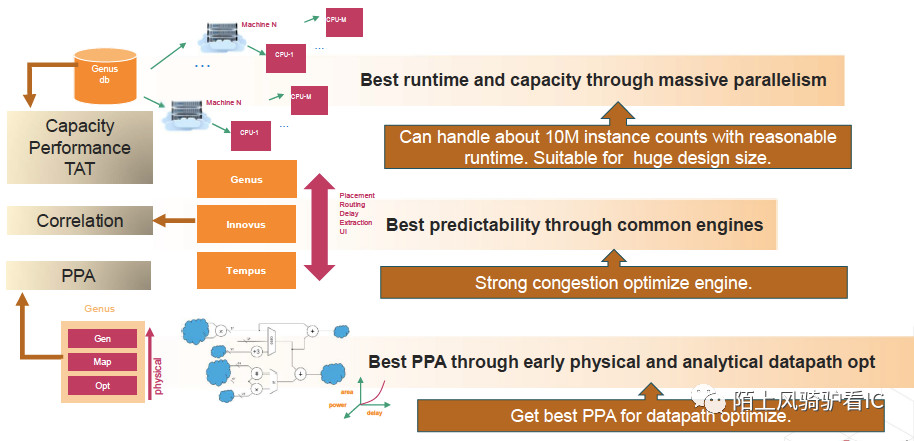

Genus 在应对这些挑战时大体上做了三件事儿:

为了应对大规模设计,整个cadence数字实现工具都采用了一种新的大规模并行算法,具体到Genus端来看,大规模并行算法的核心是如何切割设计,在切割设计的时候要保证:

- criticalpath 不能被切割;

- 被切割的每一块,需要的处理时间接近,避免长尾效应。

为了做到以上两点,Genus在优化过程的不同步骤,会以『拓扑结构+ timing driven』 相结合的方式对设计进行切割。有了大规模并行算法的支撑,Genus可以支持10M instance 或更大的设计,并且可以保证runtime 在可接受范围内。

设计越大需要的机器资源就越多,不能既让驴跑又不给驴吃草,通常:1.5M 以下的设计建议用8个CPU,1.5M ~ 3M 的设计建议用16个CPU, 5M 以上的设计建议用32CPU。

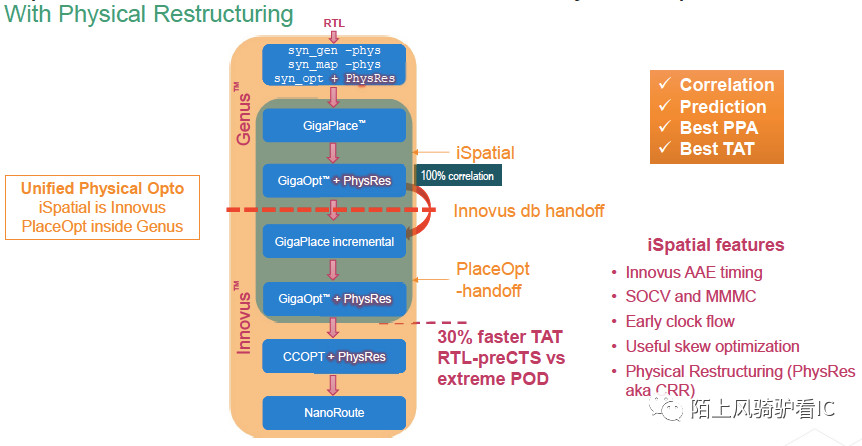

为了应对先进工艺的挑战,Genus在物理综合上做了许多尝试,并最终确定了ispatial flow, ispatial flow 一方面可以保证前后端足够好的 correlation 跟 predication, 另一方面又不会使runtime 过长,同时还具有强大的congestion 优化能力。

为了应对复杂运算逻辑,Genus采用了新的逻辑分析、优化引擎,可以根据不同的设计目标,选择相应优化策略,以得到『恰当』的结果,此处要强调的恰当就是不过优化,不欠优化。

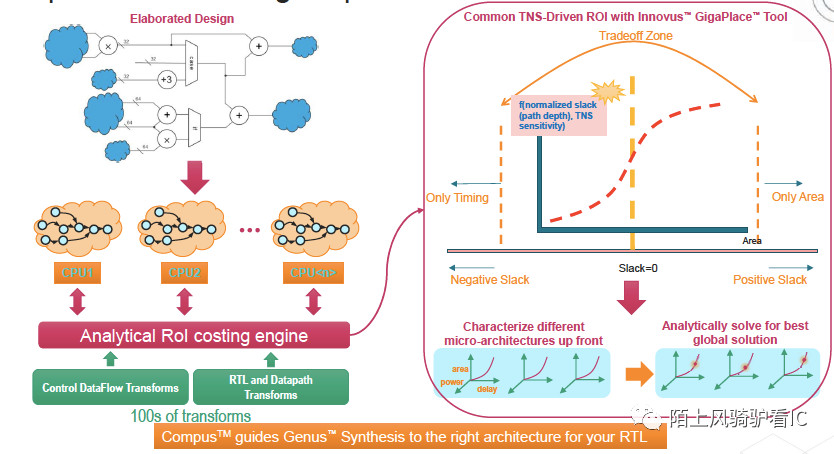

新的运算逻辑优化引擎称为Compus, Compus 有许多新的特性:

- 首先来看Rewrite 功能: 现在许多新的设计都会用SV 的高级语法,抽象级别特别高,代码写出来特别飘逸,而要处理这样的代码,如果用老的方式,会得出面积特别大的东西,在Genus里有个功能叫rewrite, 顾名思义就是把代码用对优化引擎更友好方式重写一下,这一过程对用户是不可见的。这是一个示例,在这个示例中,这样一段风格清奇的代码,经过rewrite 逻辑可以从92000 instance 优化到29000 instance.

- 再来看运算逻辑结构的选择,对加、减、乘、除、取余等每一种运算,在工具中都有多种预定义的结构,Genus在syn\_gen 时做结构选择,结构选择的过程可以看成是对一个三元方程求最优解或近似最优解的过程,三元方程的三个变量就是PPA——performance, Power, Area. 在Genus里对应的算法引擎叫Analytical Rol costing engine.

- 再来看TNS 优化策略:Genus不再是只优化WNS 优化,而是会同时做TNS 的优化,对所有path 都尽可能的去优化,Genus 在做优化的时候,会有这样一个tradoff 区域,以slack 为基准,对slack 负到一定程度的path, 工具会尽最大的努力去做timing 优化,对slack 落在中间这个区域的path, 工具会在面积跟timing 之间做tradoff, 对于slack 正到一定程度的path, 工具会尽最大努力去优化面积。如果是做物理综合,工具在做TNS优化时,会以TNS sensitivity 为基准去做优化,从左边这副图可以看到,同样是improve 50ps 的TNS, 但是由于上面这个逻辑锥有许多load, 而下面的逻辑锥只有一个load, 结果就是对上面逻辑做优化得到的收益相对更大,那它对应的sensitivity 就更高,工具在做placement 的时候,会将sensitivity 更高的逻辑摆放的更集中,以减小net delay, 得到更多收益。

- 再来看对于整个数据路径的优化:大部分数据路径的结构都可以简化成:『选择+ 运算』或『运算+ 选择』;在综合过程中,对mux 的处理是个很讲究的过程,对于选择逻辑,如果选择的比特宽到一定程度,就会引起congestion 问题,需要工具对mux 做拆解,把一级mux 拆成多级,但是拆分的级数又不能太多,否则会导致逻辑级数太长,timing 跟面积都没好处,在工具端这些tradoff 的背后都是数学、算法跟方程。所有的 『选择+ 运算』和『运算+ 选择』之间都可以相互转化,工具在优化的过程中会根据当前的设计目标,去做对应的转换,对于timing要求不高的设计可以把『运算+ 选择』转化成『选择+ 运算』,这样会减少运算逻辑从而大大节省面积;而对于timing要求高的设计,则可以将『选择+ 运算』转化成『运算+ 选择』以得到更好的timing.

这一部分内容可以都是『工具端』事儿,除了更好的PPA内部细节对工具使用者是不可见的。

低功耗一直是数字电路设计实现lin领域的一个热点,如果从整个系统来看,架构、算法、软件决定了整个系统80% 的功耗,剩下的20% 留给数字实现端来发挥。

现今主流方法学秉承早发现早治疗的策略:进入数字实现端,从RTL开始就要去分析功耗,以及早发现设计上的『功耗漏洞』,毕竟设计上的微小更改就可能带来很大的功耗收益。

Joules 是主流的RTL 功耗分析工具,可回顾《不做Hot Lady做Cool Girl》,其特点是:

- 强大的激励处理能力;

- 集成了Genus快速综合引擎,可以将综合所用的所有手段都使上<比如:multibit, DFT insertion, retiming 等>,并且可以模拟clock tree 跟buffer tree,以尽量接近后续实现的真实场景。

- 可以快速跑出相对精准的功耗,并找出设计中的漏洞,反馈给设计人员做设计迭代。

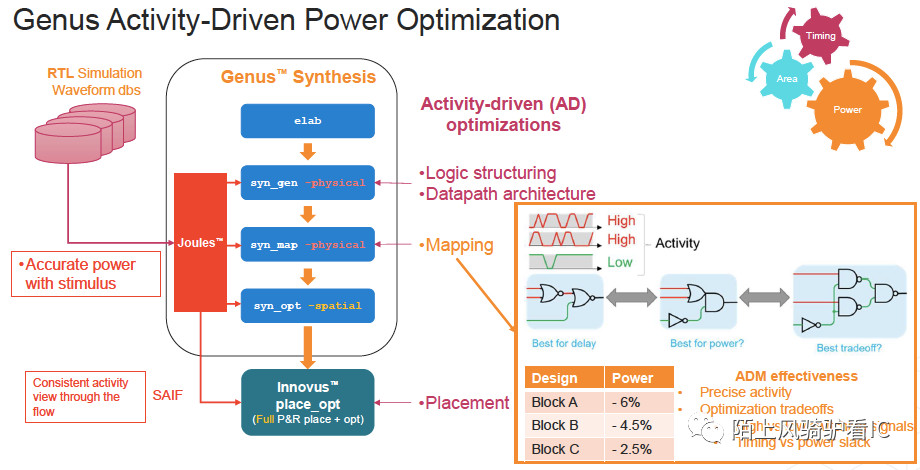

到了综合端,功耗优化手段无非是:clock gating, multibit, Multi-VT, 操作数隔离,定义多电压域,而其中最简单有效的还是clock gating, 但是对于超低功耗设计,比如IOT, 通常应用场景单一,在综合跟PR阶段带着波形文件去做动态功耗优化,可以得到更大收益。对于带着波形做动态优化,通常都会有如下疑问:

什么样的设计适合带着波形文件去优化?是否真有收益?在综合时要注意什么?

- 应用场景单一的设计适合带着波形文件去优化,因为只有应用场景单一的设计才能提供相对完备的波形,对于应用场景单一的设计,带着波形去优化动态功耗,一定是有好处的,如果是28nm 之后的新工艺,带波形综合一定要带物理信息,否则net上的电容没有,优化出的结果跟PR后的结果会有出入。

带波形优化动态功耗,工具基本做几件事:

- 将翻转频繁的信号尽量『往后』移,所谓『往后』就是让其影响的逻辑尽量少;

- 将翻转频繁的信号接到cap更小的pin 上,比如一个与门两个pin的电容不一样大,把翻转多的接到pin电容更小的那一侧;

- 将简单cell合并成复杂cell, 减小cell 之间的net 由于频繁翻转消耗的功耗;

- 将翻转频繁信号的线长做短,减小net电容对功耗的消耗;

- 修transition, 减小internal power 的功耗;

- 尽量去balance 逻辑,减小glitchpower.

多年来clock gating 依旧是降低动态功耗最有效的手段,但ICG cell 本身也会消耗功耗,所以在插入ICG cell 时需要评估,一个ICG 最少驱动几个寄存器才能有足够多的收益,目前常见的min 值是3~4,也就是说一个ICG 至少驱动3~4 个寄存器才有收益,那bank 数少于3~4 的寄存器就不会被gating, 为了进一步挖掘clockg ating 的潜能,XOR clock gating 粉墨登场,但是因为clock gating cell 在clock tree 上,用XOR clock gating 需要十分谨慎,带着波形文件,根据实际的翻转情况去插入XOR clock gating 会更合理。

物理综合,physical aware synthesis 的发展是个逐步递进的过程,在最早40nm 时代,只要工具可以做place 就能保证足够好的correlation 了。但是到了16nm 之后,不只要求工具可以做palcement 而且需要工具做真正的global route, 即layer ware 的global route, 而且需要相对精准的RC 抽取,不只要抽net 的delay 还要抽VIA 的delay.

Ispatial flow 是Genus 的physical aware synthesis flow, 其特点是:

- Early physical: 在syn\_gen 时就做module palce.

- 集成了innovus 的Gigaplace 跟GigaOPt 引擎,具有强大的Congestion 优化能力,极好的Correlation 和prediction.

- Early clock flow.

- Useful skew optimize.

- 以及Innovus 的一些黑科技。

作者:陌上风骑驴

来源:https://mp.weixin.qq.com/s/GZphTVcbZi49xy40HHim0A

作者微信公众号

相关文章推荐

更多IC设计技术干货请关注IC设计技术专栏。