胖友们大家好,太久不见,大家都还好吗?发量减少了多少?脂肪堆积了多少?核酸码绿着吗?股票红着吗?大部分驴友都深陷在口罩围起的囹圄之中,辗转徘徊无可奈何却又不得不逆来顺受,接受这时代落下的粒粒灰尘,背负着转圈或是前行。遥想三年之前,我们踏海攀山远渡重洋去欣赏历史遗留的美好跟自然赠予的壮阔,跟陌生人...

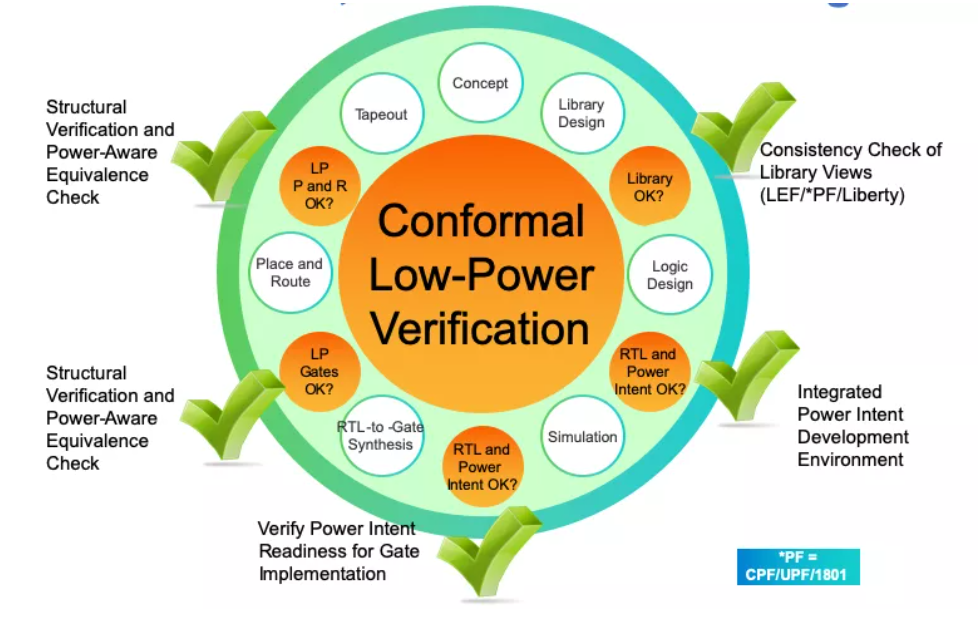

每年都有新客户的感觉特别好,总能遇到新的人结成新的关系摩擦出新的火花,当然公司也能赚到新的钱。从大理浪完回来之后的一周大部分时间都在看UPF 跟CLP,其实这两个点之前也写过,再搬出来写一写,你们可以再看一看,大部分问题自己就可以解决了<巨大的私心>。

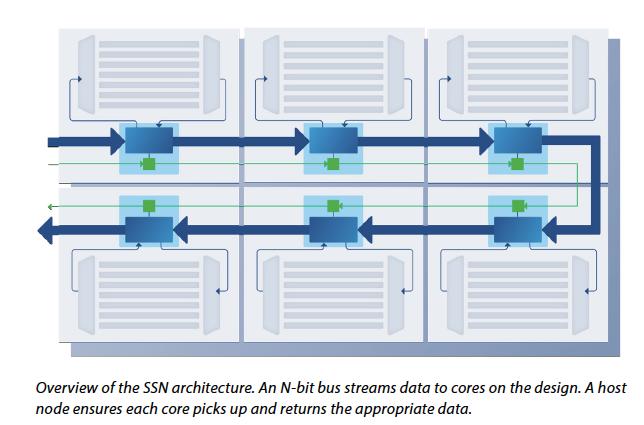

一次酒局,听业内某位DFT 大拿讲DFT 技术革新:先是感慨近几年工艺跟设计踏着一个又一个技术热点或噱头『突飞猛进』,以致整个数字实现链路上的相关技术大都发生了巨变,尤其是在AI 加持下,但DFT 作为数字实现链路上非常重要的一环却似乎一直都『止步不前』;说到起伏处突然话锋一转目露精光,问在座的各位有没有了解过...

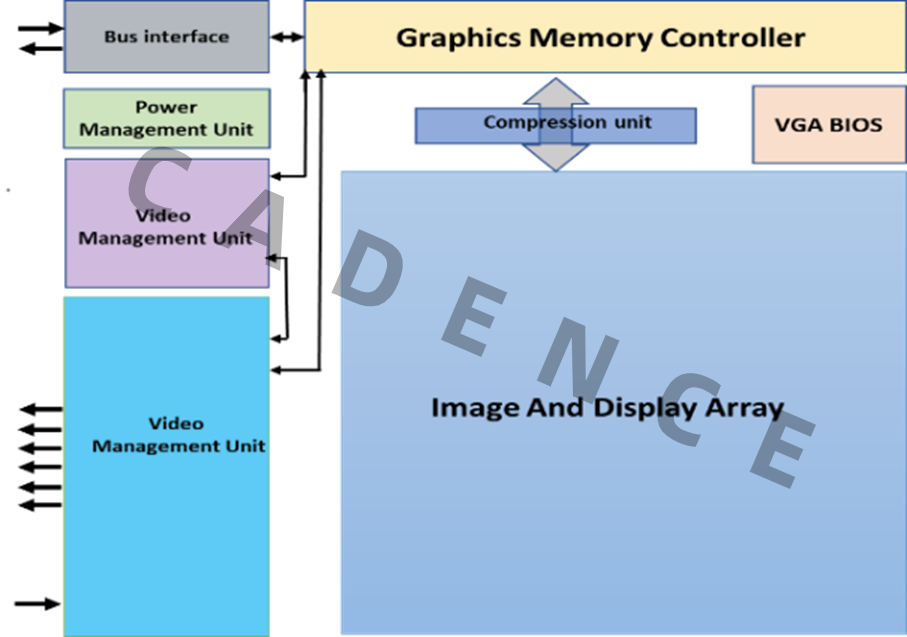

近年来,随着 GPU 在通用计算领域的高速发展,逐渐将应用范围扩展到图形之外,例如人工智能、深度学习和自动驾驶。这些领域的特点要求 GPU 在并行处理海量数据的同时提供更高的访存速度和浮点运算能力。

题记,VLSI System Design 上的这篇文章其实没什么实质性的内容,只是一个特别特别笼统的概述,而且由于年久失修,某些地方的概念欠完备,但该文趣味十足,尤其是文中的手图——阐释了什么叫『简约美』,沉溺于这几张手图,所以一定要转一下,文章前半部分做了非一一对应的翻译,后半部分翻译过来比译制片都搞笑,还是看原...

前文《跟老驴一起学PR | Innovus 输入》阐述了 Innovus 所需要的输入数据有哪些,今天来学习如何将这些数据读入Innovus. 以前熟悉的工具,不论是综合、formal 还是STA 读入数据大多都是read_xxx 命令读入,思维定势之前以为Innovus 也是用一坨read_xxx 的命令读入,然而并不是。

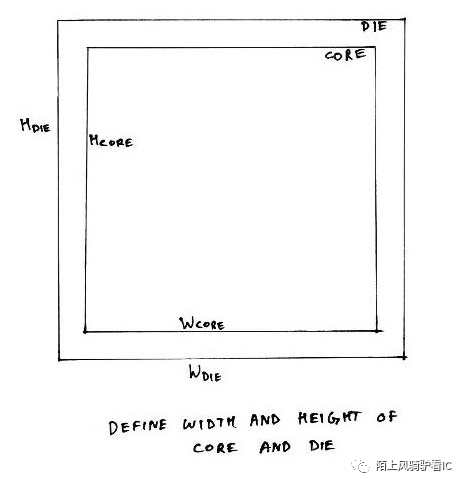

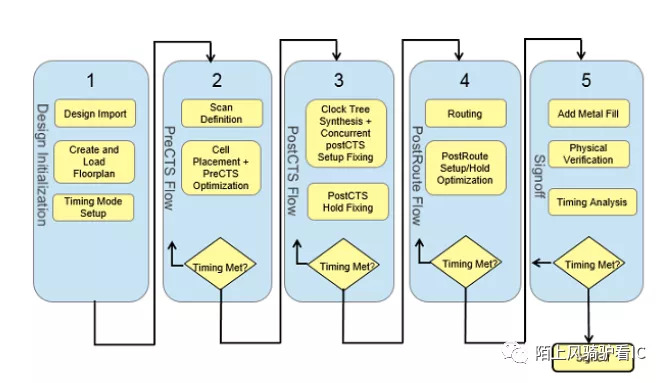

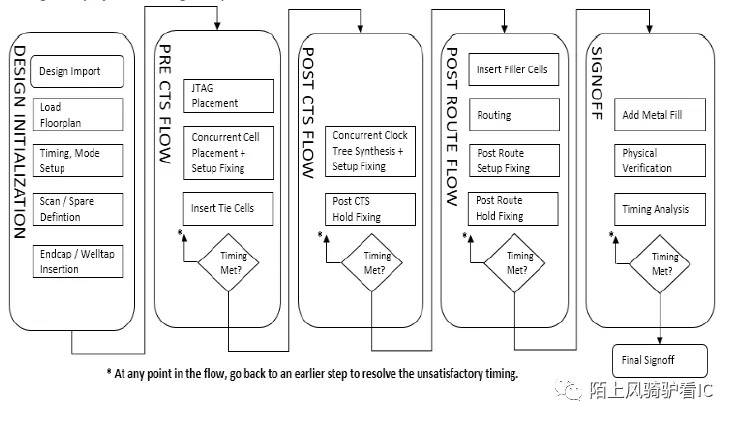

基于两个事实——工作需求,码文需求 —— 从今儿开始,老驴要系统地学习一下PR,从innovus 的user guide 开始,同时会找个不大不小的设计实操,会将学习笔记发到驴号,这部分内容太过初级,适合于小朋友跟老驴这种从头开始学习的老不懂。

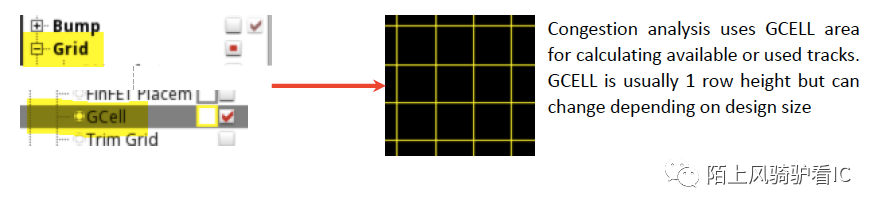

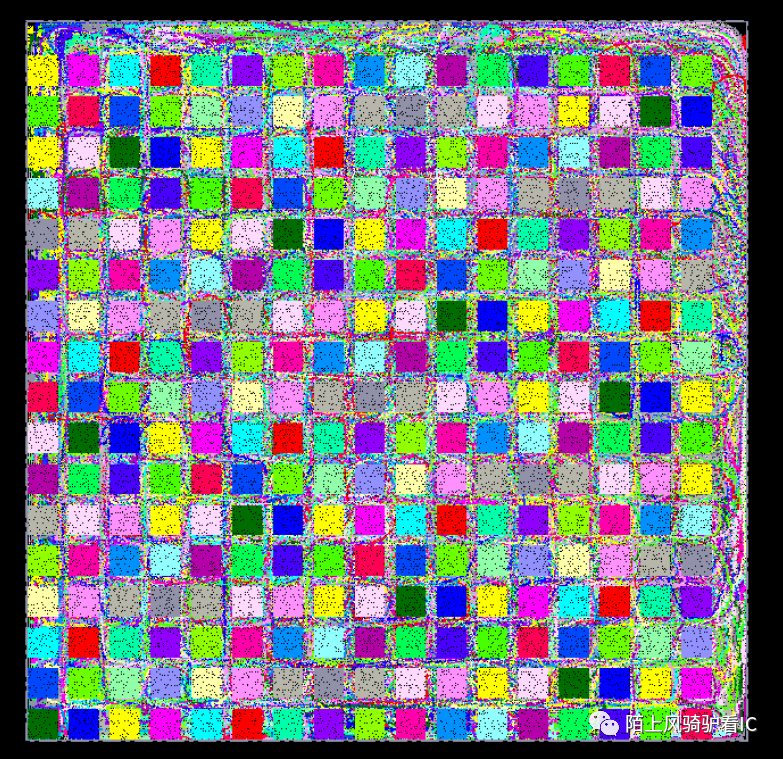

粽子节快乐,长胖了吗?热晕了吗?加班了吗?物理综合的一大目标是优化congestion, 衡量congestion 的指标有:OverflowHotspotsOverflow 跟Hotspots 是如何计算的,是用什么来表征的?Congestion 分析基于一个基本『单元』称为GCELL: Routing Grid cell. Gcell 是工具自己定义的一个单位格子,通常是一个ROW 的高度的小...

“分工”是任何群居生物的基本合作模式,最原始的分工目的无非是为了提高效率、最大化群体效益、提高群体存活几率。人类社会得益于“吃铁丝拉笊篱”的编故事能力,分工可谓五花八门,且不可避免地会受“人为因素”的影响,安陵容使尽了浑身解数,都给雍正下了迷情药也没得到“协理六宫”的职位!

过去数十年来,摩尔定律犹如法则一般引领了半导体行业的发展,半导体制程持续升级,然而,当先进制程技术已走到5nm、3nm,甚至IBM已经发布了全球首个2nm的芯片制造技术,晶体管大小正不断逼近原子的物理体积极限。

继续码综合这一趴,相关文章回顾:《综合 | 挑战与应对》《综合 | SDC 的读入与检查》《综合 | 设计读入与检查》《综合 | LEF\, QRC\, DEF》《综合 | 概述及 library 检查》。综合需要的输入,除了以上罗列的library, lef, QRC, RTL, SDC, DEF 之外,如果是多电压域设计还需要读入power intent 文件,也就是CPF/UPF, 对...

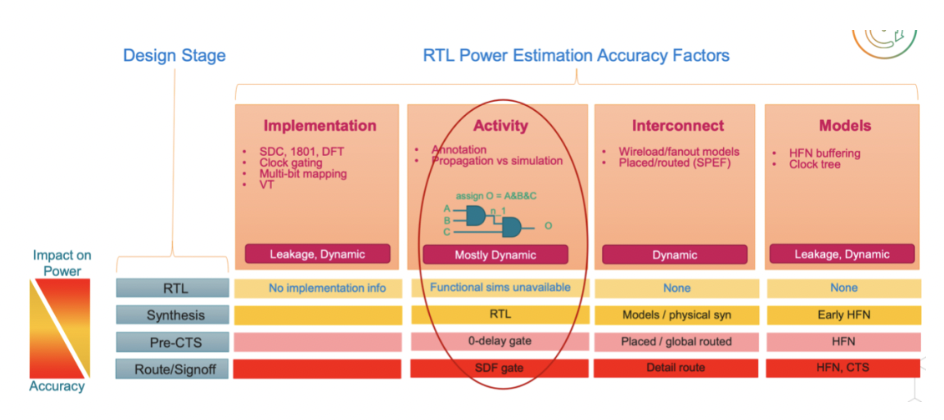

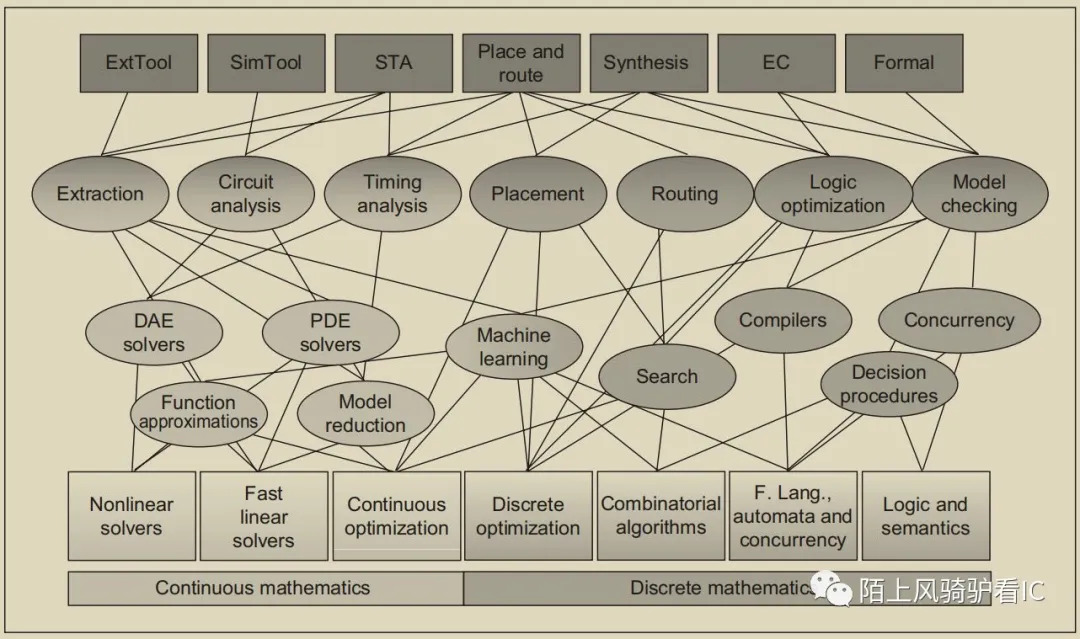

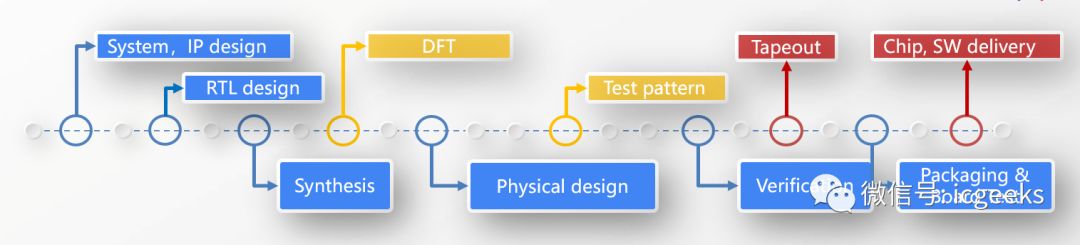

前两天,被一篇名为谷歌用AI设计芯片,强力碾压设计专家的文章刷屏,朋友圈一片“啊,要失业了”的哀嚎。如果大家真的很焦虑,我们不妨来讨论一个更加重要的话题,和我们每个人,每天的工作以及我们要去的方向都息息相关的话题,EDA的shift left。大家稍微留意一下DAC,DVCon和各种EDA的演讲和访谈,应该对shift left这个...

后端概念好繁琐,自从开始做ispatial 就被后端各种概念搞得七荤八素,挫败!挫败!挫败!在做物理综合时,除了LEF, DEF 概念搞懂之外,最常用到的就是各种 "guide" 了,在Innovus 中有以下四种.

继续综合这一趴,顺着流程往下,今天码SDC 的读入与检查,前序回顾《综合 | 概述及 library 检查》《综合 | LEF\, QRC\, DEF》《综合 | 设计读入与检查》,SDC 是数字实现的『准则』,所有的优化都以SDC 为目标。

继续码综合这一趴,可先回顾:《综合 | 概述及 library 检查》跟《综合 |LEF\,QRC\,DEF》。在读入lib, lef, qrc 之后下一步要读入的就是设计,设计可能是:Verilog, VHDL, SystemVerilog几种硬件描述语言的一种或多种的混杂。

接着《综合 | 概述及 library 检查》继续掰扯综合的输入文件,虽然DEF 要在解析完RTL 之后才读入,但因为LEF, QRC, DEF 都属于物理综合必需的文件,所以放到一起来掰扯。

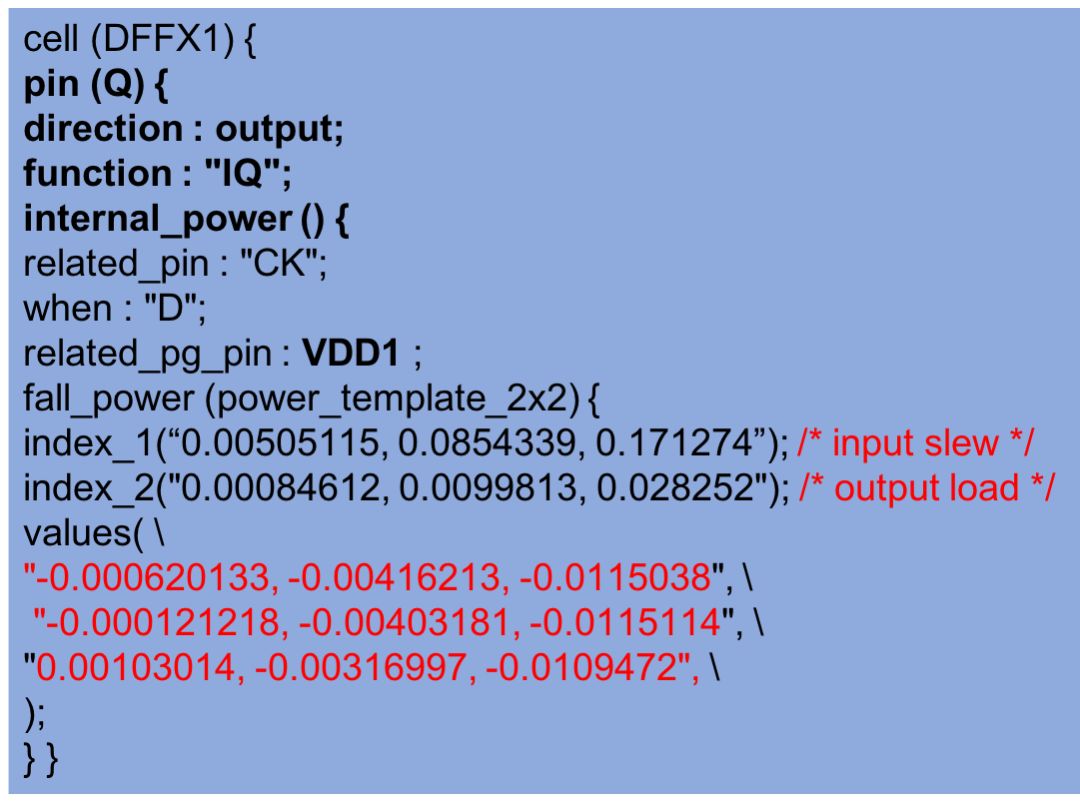

题记:大概一个月之前有人在驴群里问到,为什么internal power会是负值,驴也是第一次看到负的internal 功耗,当初有大神已答 internal power 为负的原因,在此基础上,驴研读了一些library的材料,整理于此,知其然知其所以然。

在IC 设计公司,关于度量在企业内部一直存在一个明显的矛盾。一方面,我们看到管理者们拿出名目繁多的度量方法,试图保障流片的质量和效率,量化员工的工作,把各种量化指标跟员工的KPI 绑定在一起。另一方面,员工们却抱怨不停的报告和各种清单及报表,觉得自己正常的研发工作受到了严重的打扰。但是如果我们想要追求IC...

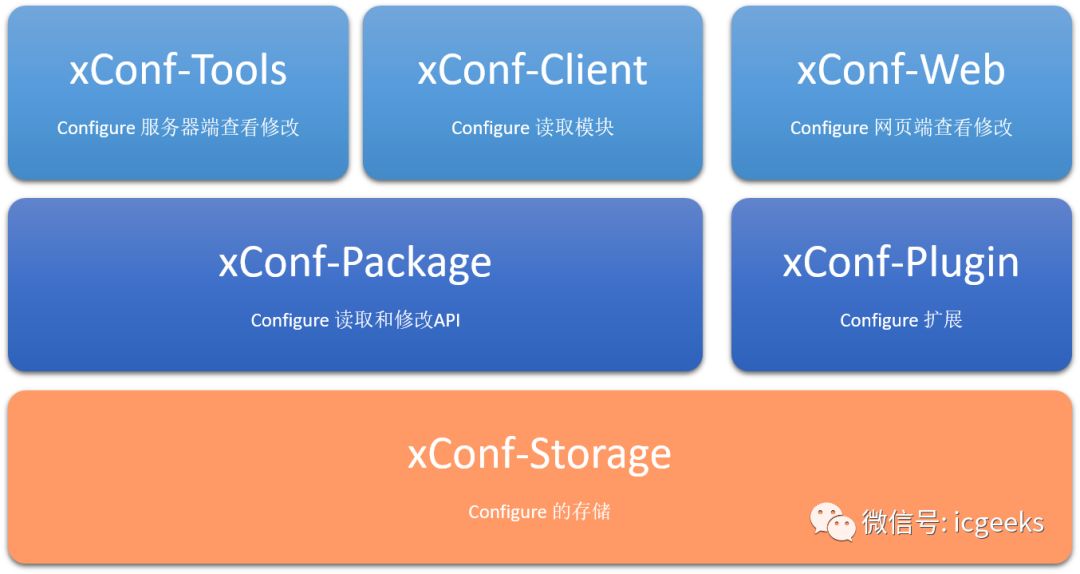

Alice 在IC 极客群里谈到了配置管理,那我也来谈一谈。配置的设计更多的是在软件的管理和使用中被提及,而IC 流程中,配置也是需要的,但是上升到配置管理很多时候并不是那么被人看好,但是配置管理可以帮助你提高效率,减少交流误差,自动化流程,内容驱动管理等等。

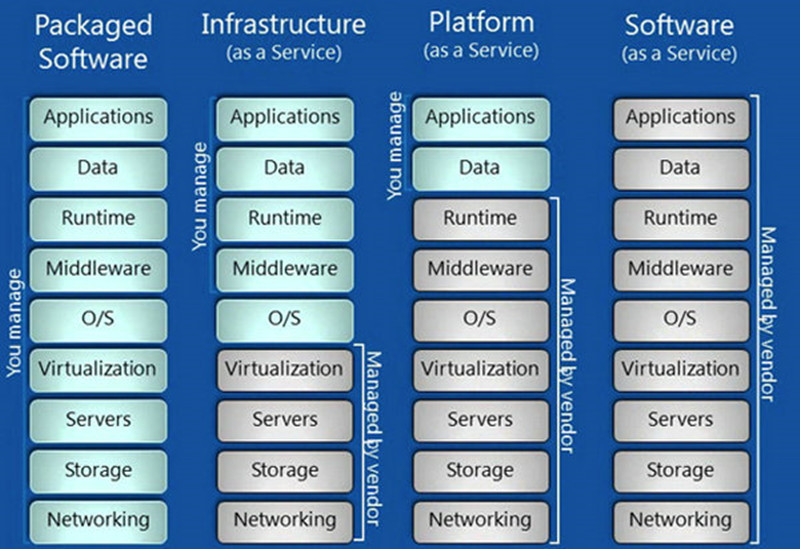

猝不及防,这两天被google 造人的文章刷爆朋友圈,AI 已来,码农们又一次陷入了人活着工作没了的焦虑,ICer 的工作会被EDA 工具替代吗?最近在IC 极客群里面关于“EDA in the Cloud”的话题经过两轮激烈的讨论,群友们贡献了很多新鲜热辣的观点,是时候需要对这个话题进行总结性的归纳了。我因为职业背景的关系,并且之前...