前文提要:前文总结lvs的提速技巧,包括如何进行多cpu并行计算,以及将layout netlist抽取与lvs check进行分离,加快debug循环,优化hcell list 等方法。本文将介绍如何将经常修改的部分与rule进行分离。这样我们可以使用多个不同的配置文件,而使用相同的rule deck。这样的好处不言而喻,一是便于管理,二就是不必搜索修改rule deck,配置文件中仅含有少量我们需要修改的部分。

基础知识

为了便于理解我们所使用的方法。这里先了解一下基础知识。

TVF and SVRF

SVRF:Standard Verification Rule Format

我们的DRC LVS rule就是用这个格式来写的。

TVF, TCL Verification Format, 可以理解为SVRF的一个tcl的扩展,便于在写rule file的时候,采用tcl的那些语法。

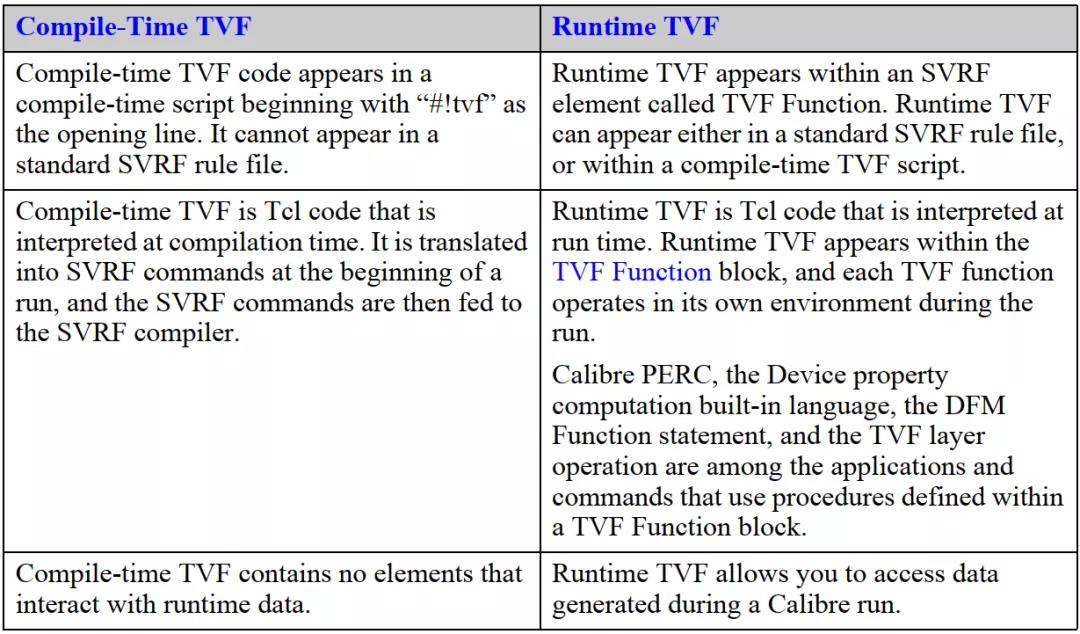

TVF又分为两种, Compile-Time TVF 和 Runtime TVF 两者的比较如下:

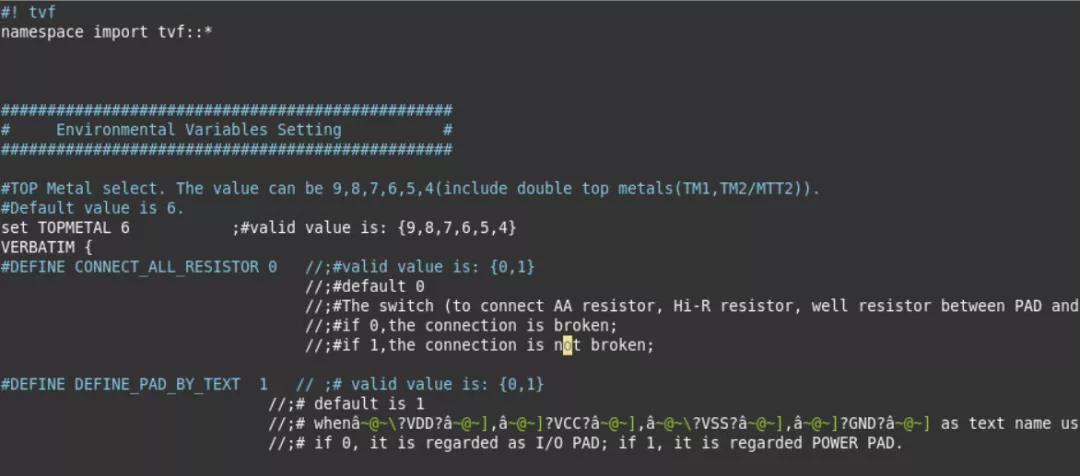

如果文件第一行是#! tvf,那么,这就是一个Compile-Time TVF.

里面的语法就是tcl。

例如:

图1

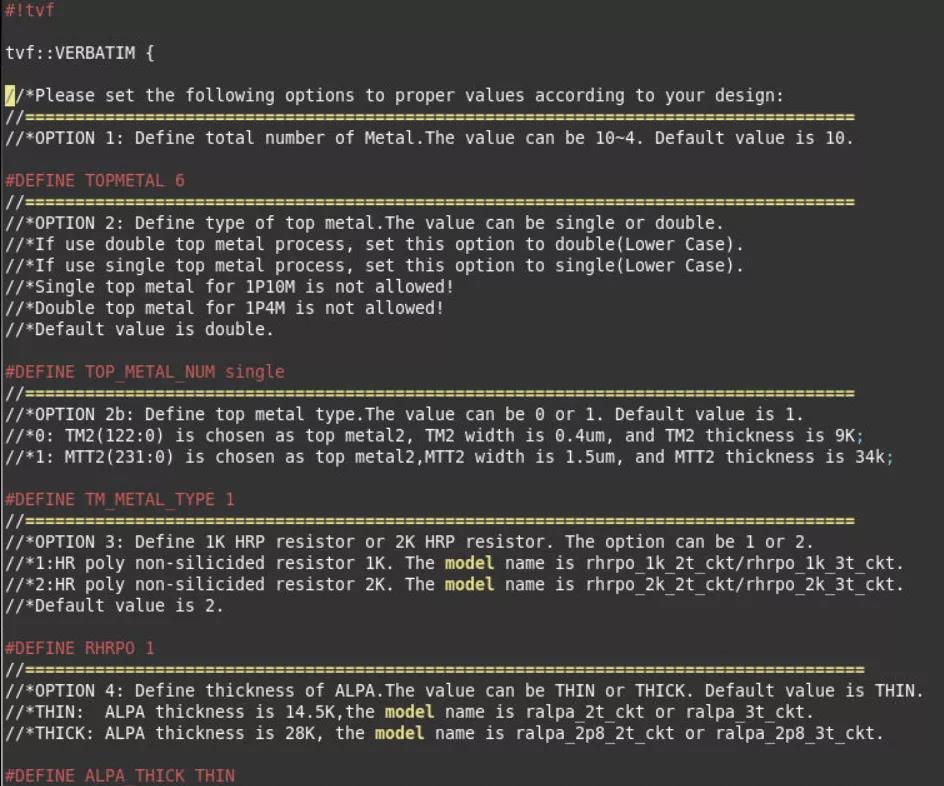

或者:

图2

稍等,上面的图2里好像不是tcl, 而是标准的SVRF文件。这里就需要说明一下下面的一个语法:

tvf::VERBATIM

tvf::VERBATIM是一个function, 在这个function里面,是可以直接使用SVRF statement的。也就是说,在图2中,其实看到的是SVRF的语法。

如何分离

以我们经常改动的gds cdl声明为例:

LAYOUT PRIMARY "" LAYOUT PATH "" LAYOUT SYSTEM GDSII

SOURCE PATH "" SOURCE PRIMARY "" SOURCE SYSTEM SPICE

我们就可以将他们(不仅限于)放到单独的文件中,作为配置文件。而源文件保持不变。

当然需要我们加上必要的tvf声明,例如

#!tvf

tvf::VERBATIM {

LAYOUT PRIMARY ""

LAYOUT PATH ""

LAYOUT SYSTEM GDSII

SOURCE PATH ""

SOURCE PRIMARY ""

SOURCE SYSTEM SPICE

}

source tvf.lvs.rule文件最后,别忘了source源文件。由于源文件是tvf,也就是tcl格式,就直接用source。

当然,对于别的一些需要修改的声明,也可以加到配置文件中。

LVS REPORT ""

VERIABLE POWER_NAME "?VDD?"

VERIABLE POWER_NAME "?GND?"

LAYOUT TEXT FILE ""应用举例

前文提到,将layout extract与lvs进行分离。那么,在layout extract时,我们就需要指定layout为gds文件,而在进行lvs比较的时候,就需要将layout指定为提取出来的spice文件。

这是我们可以写两个配置文件

file1:

#!tvf

tvf::VERBATIM{

LAYOUT PRIMARY "path/to/gds"

LAYOUT PATH ""

LAYOUT SYSTEM GDSII

//...

}}file2:

#!tvf

tvf::VERBATIM{

LAYOUT PRIMARY "path/to/spice"

LAYOUT PATH ""

LAYOUT SYSTEM SPICE

//...

}}在进行layout extraction的时候,执行:

calibre -spice layout.sp file1进行lvs的时候,则执行:

calibre -turbo -turbo_all -hier -lvs file2对了,最好提供一个优化的hcell list。

作者:白山头

来源:https://mp.weixin.qq.com/s/gr\_Hdul22qffpvV2yUoiHA

作者微信公众号

相关文章推荐

·【tcl技巧】如何更优雅的报出cell的总面积

·PR工具自带的电源网络分析功能靠谱吗?

更多IC设计技术干货请关注IC设计技术专栏。