有驴友在驴群里问ssg 跟ss corner 的区别是什么?老胡发了一本书,里面有两椭圆一页文字足以说明了该问题,老驴发扬一贯的鸡贼风格,从网上搜罗一遍相关内容,杂糅到一起,发出来。

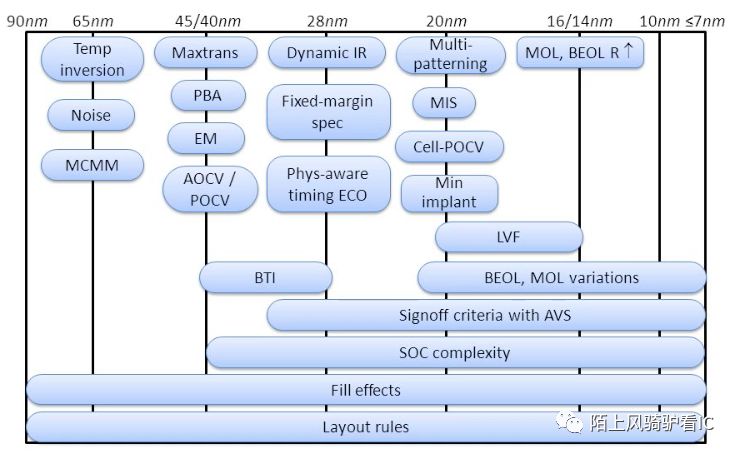

随着工艺发展,传统STA 方法学的『经典』模型疲态尽显,要想保证足够高的良率,而又不过于悲观,就得不断地对原有模型进行修正,于是有了不同的OCV 模型,也有了更多的PVT corner 跟RC corner. 下图罗列了不同工艺点引进的『修正技术』。关于PVT 可回顾《巴山夜雨涨秋池,邀君共学PVT:STA之PVT》《绿蚁新醅酒,红泥小火炉:STA之OCV》——ps: 如果时间可以倒流,一定不吟诗,要恶心死自己了!

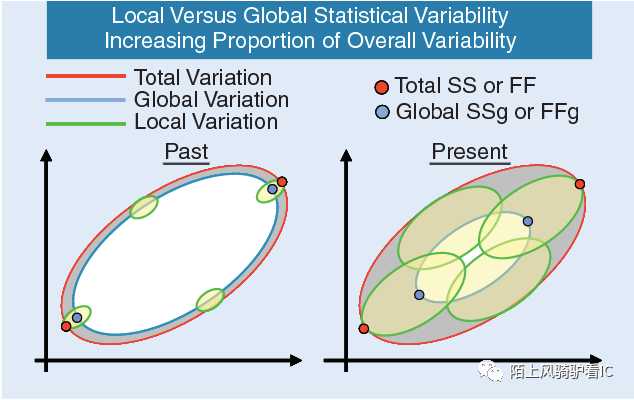

要讨论ssg corner, 需从工艺偏差的分类入手,《论STA | SOCV / POCV 之 variation》论述过工艺偏差分为systematic 跟non-systematic, 其中non-systematic 又分为global variation 跟local variation.

- Global variation: 由于工艺偏移导致的die-to-die, wafer to wafer, lot to lot 之间偏差,如:同一个chip上所有管子的沟道长度都比典型值偏大或偏小。

- Local variation (within-die or intra-die): 同一芯片上不同管子受工艺偏差影响不同< 注:on chip variation 之源>,如:同一芯片上有些管子的沟道长度偏小,而有些管子的沟道长度却偏大。显然,local variation 比 global variation 小。

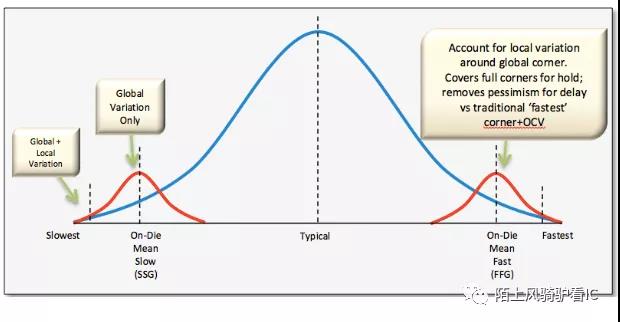

从统计结果可知,在老工艺中,由于local variation 非常小,所以在K 库时会将local variation 跟global variation 全都考虑进去,STA 分析时用worst-case 模型,对应的corner 为 SS (slow nMOS-slow pMOS ) 和 FF ( fast nMOS-fast pMOS),其中SS corner 只有early derate, FF corner 只有late derate。而在新工艺下,local variation 显著增加,如果再用worst-case 模型会过于悲观,所以采用了新的统计学模型,在K 库时只包含global variation,local variation 用“统计学OCV——SOCV / POCV ” 进行补偿,对应的corner 就是ssg, ffg.

为了不再引入谬误,抓两段英文原文过来。

The problem is on-die variation. We can’t assume that if one transistor is faster than typical that the transistor it is driving is also faster. There are a number of reasons for this but one big one is that optical proximity correction (OPC) means that identical transistors do not end up identical on the mask since that depends on what is around them. In response, foundries have broken out on-die variation as a separate component in their SPICE models. They created global corners for slow, typical and fast. These global corners, called SSG (slow global), TTG (typical global) and FFG (fast global), only include between wafer variance. On-die variance is separated out as a set of local parameters as part of the SPICE model that work with Monte-Carlo (MC) SPICE around the global corners.

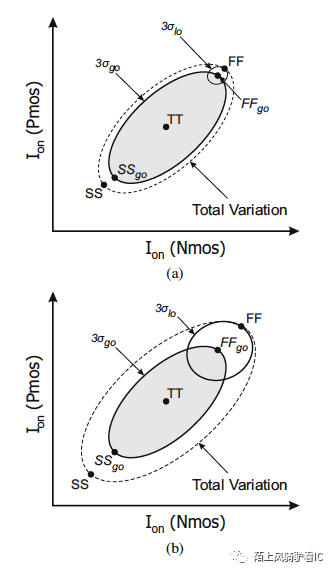

Figure 1.12 shows the relative impact of global (σgo) and local (σlo) variations in older and newer technologies. Global variations, also known as inter-die variations, present a radial dependence through the wafer and were successfully considered in the past using worst-case analysis . This was because the impact of local variations was significantly less severe than inter-die variations in older technologies. This is illustrated in Fig. 1.12a where the spread of the saturation current of nMOS and pMOS transistors due to local variations (3σlo) is much smaller than for global variations (3σgo). The final corners (FF and SS) are close to the corners without local variations (FFgo and SSgo). In older technologies, corner- based analysis could guarantee a good yield of a circuit after fabrication. However, local variations due to the nature of their statistical behavior are pessimistically modeled by worst-case analysis. This fact aggravates in newer technologies, which present significant local variations. Figure 1.12b shows that the relative impact of intra-die variations (3σlo) with respect to global variations (3σgo) increases significantly in newer technologies. Now, there is a significant difference between the final corners (FF and SS) and the corners without local variations (FFgo and SSgo). As a consequence, the cost incurred by corner-based design becomes even higher in newer technologies and shows the necessity of using statistical analysis in the design of current and future semiconductor technologies.

此外,顺道澄清三个被反复问到的问题:

- AOCV 或LVF 为什么要考虑spatial derate? 老驴以为亦是为了模型修正,spatial derate 用于模拟Spatially correlated variations: 相较于距离相距较远的管子,相邻管子有像似特征。这也是AOCV 跟 SOCV / POCV 要考虑 spatial / distance 的原因。

- PVT, 除了P 的variation 之外,V 跟T 的variation 怎么设置?在较新工艺的sign-off requirment 中,会有V/T 的variation table, 其中V 的index 是静态IR-drop 的百分比,至于具体如何设,怎么设,按照要求来!不逾矩!

- AOCV 或LVF 中只有cell 的variation, 是否需要设置net 的variation? 这里通常会提到:front end of line (FEOL) 跟 back end of line (BEOL), 驴号之前论述过net 对应的RC corner, 可回顾《抽刀断水水更流,RC Corner不再愁:STA之RC Corner》《一曲新词酒一杯,RC Corner继续飞: STA之RC Corner拾遗》《且将新火试新茶,深究趁年华:STA之RC Corner再论》,先进工艺net 跟Via 在制造过程中也会有工艺偏差,对于这部分工艺偏差,sign-off requirment 中同样会有张表,通常是7%。

作者:陌上风骑驴

来源:https://mp.weixin.qq.com/s/qw8EMWNXkjtJGdRbevxdug

作者微信公众号

相关文章推荐

• OTP们:PROM,eFuse,Antifuse

• IC圆桌派IoT,RTL及低功耗复盘篇

• RTL 加密

更多IC设计技术干货请关注IC设计技术专栏。