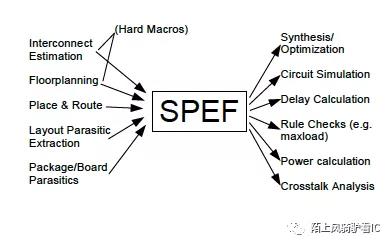

SPEF 全称 Standard Parasitic Exchange Format 是IEEE 标准,最新的标准号是:IEEE Std 1481– 2009. 用于描述芯片中的『连线特性』,即:电阻,电容,电感。SPEF 在数字实现流程中用于『连线特性』在不同工具之间的传递。

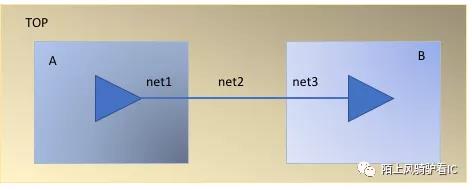

虽然用了多年SPEF 但一直没有扒拉开去看里面的格式,最近遇到一个问题,为了搞清楚去扒拉了一遍,问题是:对于如下设计,在netlist 中的A/net1, net2, B/net3 在逻辑上三段,在物理上是一条线,在SPEF 中这条net 是如何表示的?

SPEF 的格式比较简单,SPEF 中的关键字以"*" 开头,如*R\_UNIT, *NAME\_MAP, *D\_NET, 注释以"//" 开头,在IEEE Std 1481– 2009 协议里定义了如下几段:

- Header definition

- Name map definition

- Power and ground net definition

- External definition

- Hierarchical SPEF (entities) definition

- Process and temperature variation definition

- Internal definition

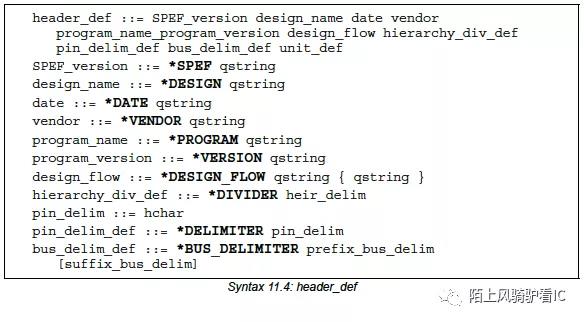

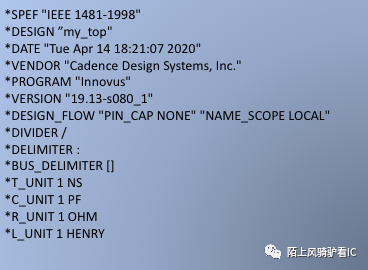

Header definition

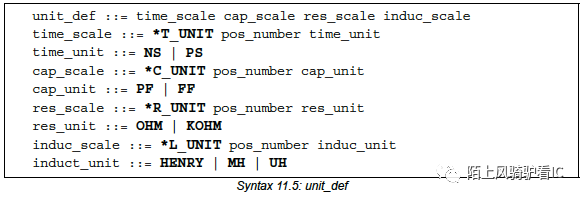

定义了SPEF 版本、设计名字、产生时间、厂商、工具、工具版本、分割符、时间电容电阻电感的单位。

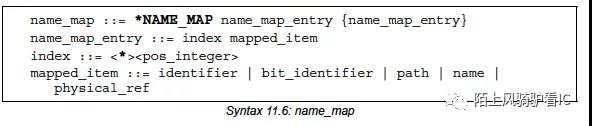

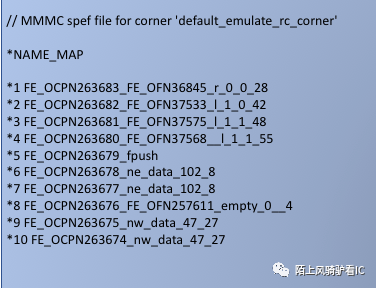

Name map definition

为了减小文件的大小,把设计里object 的名字映射成数字,后面引用时直接上数字。

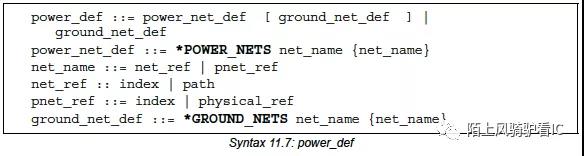

Power and ground net definition

定义电源跟地的信息。

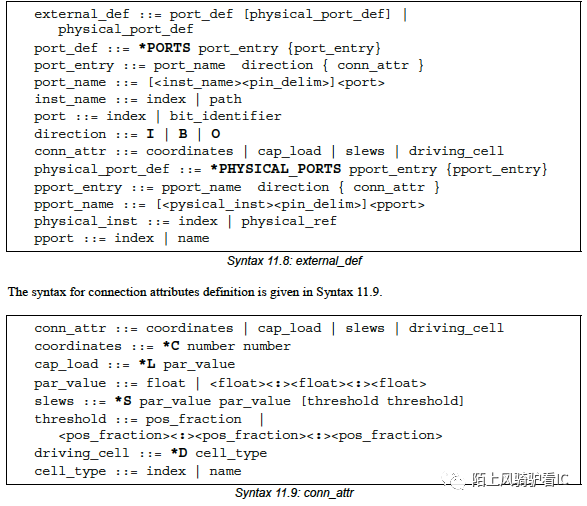

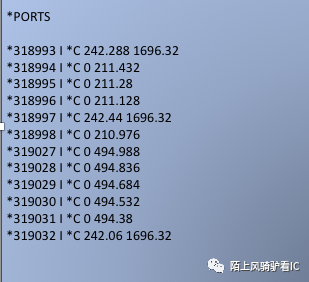

External definition

定义port 的信息,如方向:I 表示input port, B 表示inout port, O 表示Output port; 坐标:*C; 负载电容:*L; 驱动:*D 等。

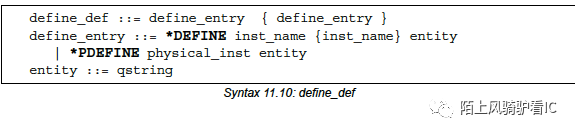

Hierarchical SPEF (entities) definition

定义当前设计中instance 信息,用于多个SPEF 合并。

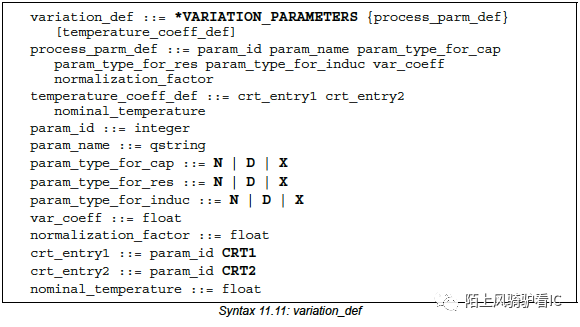

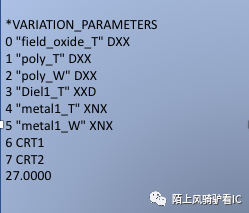

Process and temperature variation definition

这部分是IEEE Std 1481– 2009 新增加的内容,定义影响互连线电容、电感和电阻的工艺参数,电阻的一阶和二阶系数(CRT1、CRT2)以及抽取时的标称温度,有个复杂的计算公式。

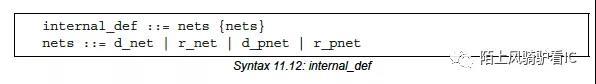

Internal definition

SPEF 的主要内容,定义了每一条net 的连接关系,电容电阻电感值:

*D\_NET

*CONN section

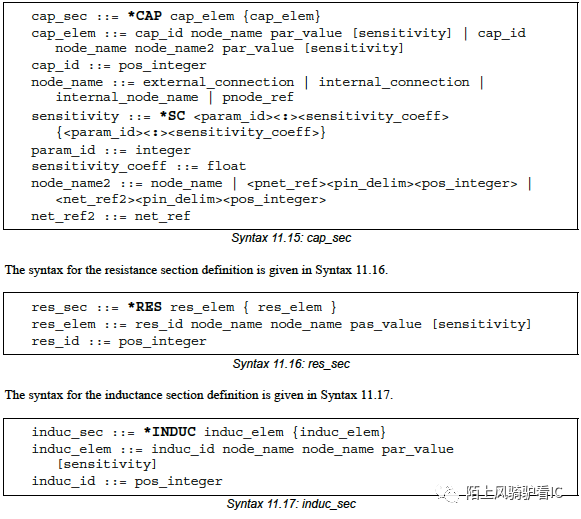

*CAP section

*RES section (single pin will not have)

*INDUC section

*END

举个例子:

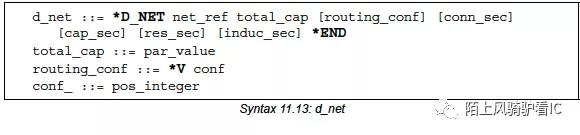

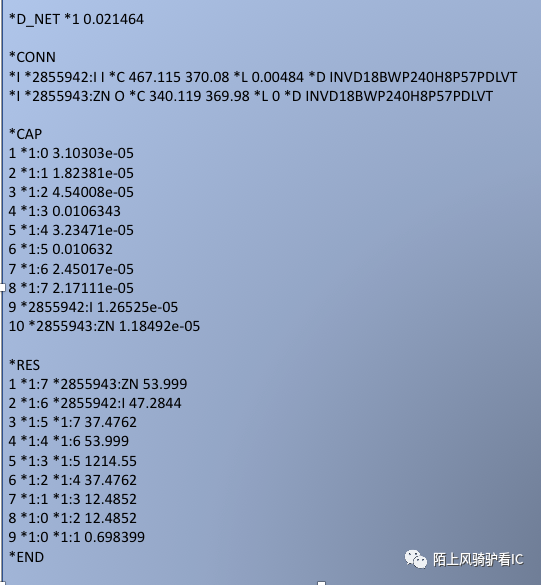

- *D\_NET 行,表示对应net 总电容,容值是*CAP section 电容的总和,*1 表示"name map" 中第一条net, 当前电容是0.021pf.

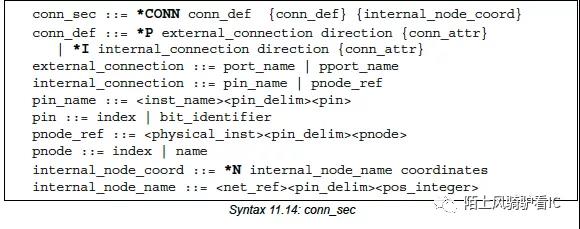

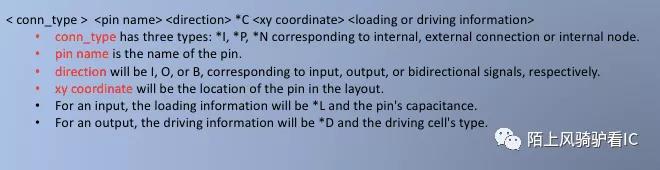

- *CONN, 部分指定了该net 的连接信息,其格式是:

- *CAP 部分定义了电容的详细信息,电容包括『对地电容』跟『耦合电容』两部分,如果net-A 跟net-B 之间有耦合电容,则该耦合电容,在net-A 跟net-B 的*CAP 部分各列一次。

- *RES 部分定义了该net 的电阻值。

回到开头的问题,对于如下设计,在SPEF 中只有一条*D\_NET.

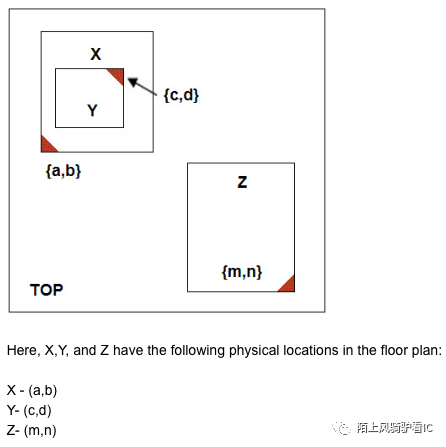

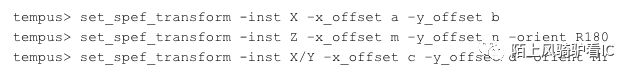

如果是hierarchical flow 且读入spatial AOCV/SOCV 则需要在top 将sub-block 的坐标对齐,如下例:

在Tempus 里用命令set\_spef\_transform 来对齐。

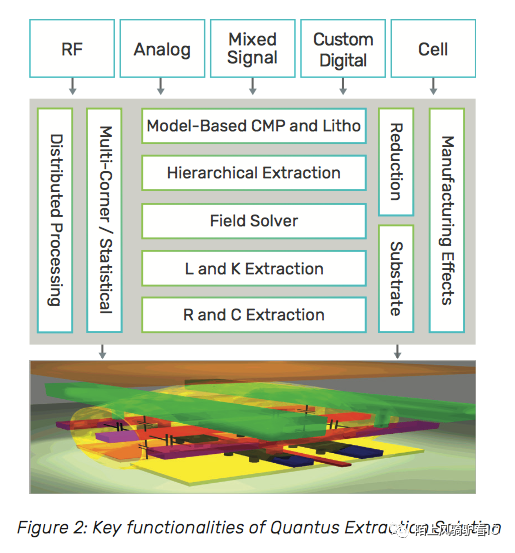

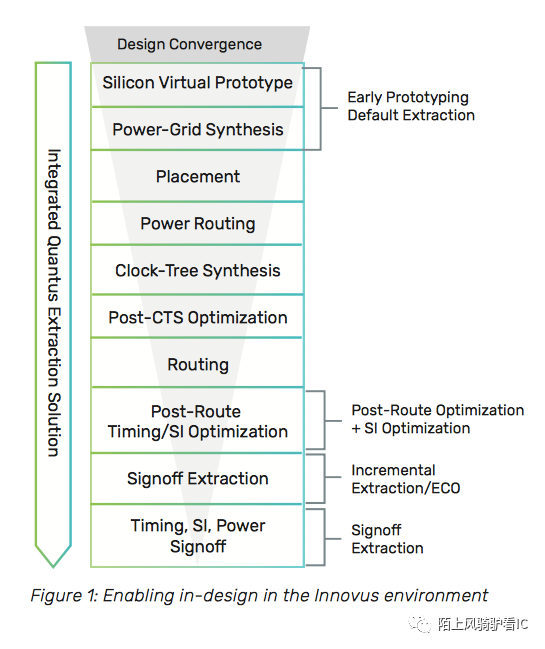

Quantus 可以用于RF, Analog, Mixed Signal, Customer Digital 等各色设计的RCL 抽取。

作者:陌上风骑驴

来源:https://mp.weixin.qq.com/s/8RgqTCH6hVDIYE3Ejm\_1CQ

作者微信公众号

相关文章推荐

•论P&R|Pin Density 跟 Congestion

•论功耗|测不准的功耗之反思

更多IC设计技术干货请关注IC设计技术专栏。