为了寻到一个相对有说服性的答案,老驴试图查了T 跟A 的文档,在说到功耗计算时,都只简略得一带而过:在typical corner 看功耗,没有实验数据没有理论依据。又在谷歌上搜索了一番,找到了一些数据,同时请教了一些前辈,也得到了一些十分有用的信息。将这些信息揉和到一起,来探讨一下功耗应该在哪个corner 看?

在《一问 | 为什么power 只需要在typical corner 做sign off?》发出之后,收到了一些朋友的回复,贴到此处:

- SLC:power sign off 确实和产品有关,power 要用到三个地方:1)产品功耗评估,功耗计算的corner 和产品工作环境有关;2)给封装提供设计依据,做封装设计,一般看typical corner; 3)做IR/EM 分析,最差的IR/EM corner 跟工艺有关。

- XMN:我以前也有过这个质疑,为啥要typical corner? 然后把所有典型corner 的波形都输出,让后端分析,报告显示typical corner 功耗较大,就接受:不同corner 下, typical corner 的功耗最大,一直沿用。

- XX:首先大家在吹牛的时候需要有统一的criteria, 而typ25c 的power 数据比较漂亮。

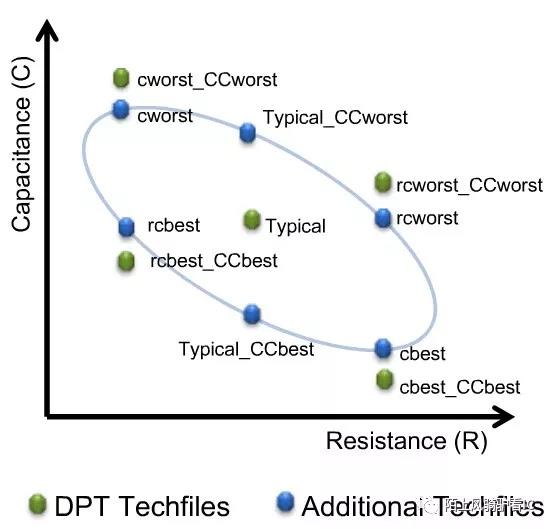

跟前辈的探讨也贴到此处,这里的论述比较详细,会涉及到RC corner 的一些基本常识,可回顾《抽刀断水水更流,RC Corner不再愁:STA之RC Corner》。

- 这是个伪命题,我的理解是:power 通常没有sign off 之说,都是做power estimation. 之所以用typical corner 是因为,芯片毕竟是接近typical 的,所以会以这个为标准。有个很重要的点,IR 分析的Power 和Power estimation 的power 是两回事儿。

- 但是实际从sign off 角度看,power 主要影响IR/EM,而这个不会只看typical corner. 芯片回来实测功耗,虽然有process 的variation 但整个variation 是可预期的,Idsat 和Ioff 都是有『预期值』的,比如偏一个sigma, Idsat 差6% 左右,那么动态功耗也就是I2 的关系,大概在这个范围;但是Ioff 的差别就会非常大,在同一个corner 也是,所以不能只看typical.

- 再者是温度,温度影响最大的是leakage, 对Idsat 几乎没影响,IR/EM 都是找『最有可能引起问题的corner』, 也就是问题最悲观的corner, 比如高温高压+ Cworst 来估计power, 而用Typical 或者RCworst, Cbest 等corner 来抽取电源网络的电阻,因为后两个R 最悲观。当然用typical 的也有。

- IR 分析的输入:lib + SPEF (Signal cap) + 电源网络R + switching activity. lib 一般会需要高温高压,SPEF 会选Cworst, 电源网络的电阻会选RCworst/ cbest/ typical corner, 不同公司选择不同。至于switching activity 是根据实际用例而来。

- Signal RC 由extraction 工具抽取,电源网络的RC 由IR 工具抽取再计算出点到点的RC, 点到点的RC 对抽取工具而言是难点,是需要计算得到的。

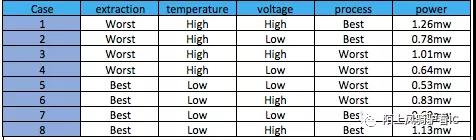

在谷歌搜到有人就此做的实验,同一个设计,未说工艺结点,在不同的RC 跟PVT 条件下,得到一组功耗值,可以看出高压+ 高温 + Cworst 的功耗最大,反而工艺偏差在该工艺结点对功耗的影响并不大。

从CMOS 管功耗构成来看,关于leakage power 的计算可回顾《四月清和雨乍晴,静态功耗乱伊心》,关于动态功耗的计算可回顾《2018世界杯第一日,撸一遍动态功耗计算》。

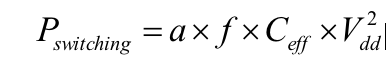

- Switching power: 逻辑翻转对有效负载电容进行充放电所消耗的功耗。公式如下,其中,a是switching activity,f是clock frequency,Ceff是有效负载电容,Vdd是芯片电源电压。根据该公式可以得出: 在频率跟翻转率一定的情况下,高压 + Cworst 会得到最大的动态功耗。

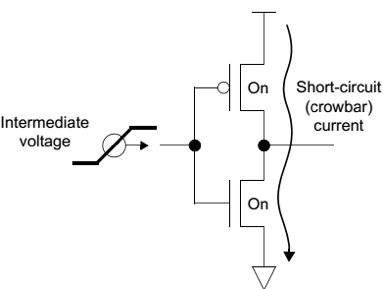

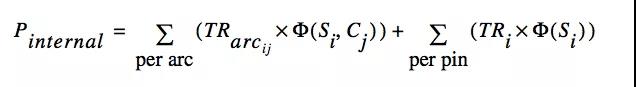

- Internal power是由于晶体管翻转的某一瞬间,PMOS和NMOS会同时导通的短路电流消耗的功耗。由如下公式可知,internal power 跟输入pin 的transition time, 输出pin 的load 相关,实际上还跟阈值电压相关,在频率跟翻转率一定的情况下,高温 + Cworst 会得到最大的内部功耗。

- 静态功耗,Leakage power主要由以下几个方面组成,跟电源电压,阈值电压和晶体管的宽长比相关,高温 + 高压 可得到最大的静态功耗。

I1 reverse-bias p-njunction diode leakage

I2 subthresholdleakage

I3 Gate-induced drain leakage

I4 gate leakage.

总结:

- 在Typical corner 看功耗,并没有什么理论依据跟实验数据支撑,更多的是一种约定俗成。NXP 在2014 年DAC 上有文章称,只看typical corner 的功耗是不够的,应该同时看更worst corner 的功耗。

- IR 分析的Power 和Power estimation 的power 是两回事儿,IR/EM 分析找『最有可能引起问题的corner』, 也就是问题最悲观的corner, lib 一般会需要高温高压,SPEF 会选Cworst, 电源网络的电阻会选RCworst/ cbest 这些R 最大的corner 抽取计算。

作者:陌上风骑驴

来源:https://mp.weixin.qq.com/s/4D\_Y8b40XPNqsiqNp9j6\_g

作者微信公众号

相关文章推荐

•ETM抽取,应该知道的一些细节

•人物访谈:我的前任老大移芯CTO斌哥

更多IC设计技术干货请关注IC设计技术专栏。