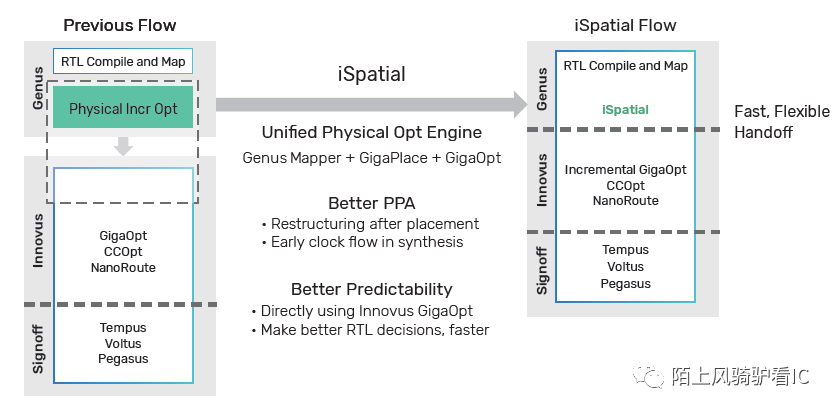

Genus Ispatial flow 自2019 年推出以来,广受客户青睐,AE 们接客接到腰酸腿软颈椎弯。Ispatial flow 除了跟Innovus 更好的correlation 之外还有两大特点,其一是CRR: Critical region restructure, 也就是逻辑重构;其二就是Early clock flow, 为了知其然老驴研读了几天Early clock flow, 今天以一篇appNote 为参考,做个学习小结。

Early Clock Flow 是个啥?

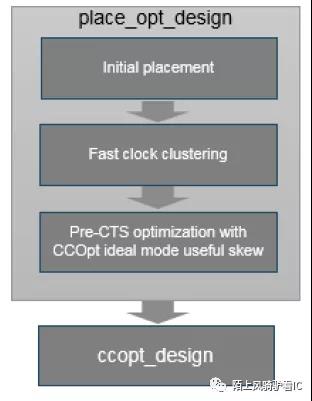

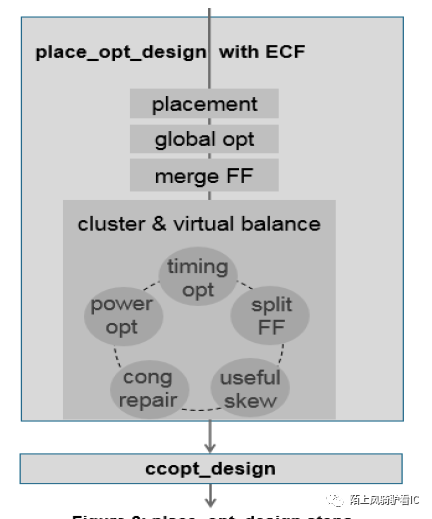

Early Clock flow 是前几年Innovus 中的一项技术革新,其呈现是在Placement 的时候做clock tree; 其思路同样是『早发现早治疗』;其做法是在place\_opt\_design 时调用CCOpt 的fast clock tree clustering 来build clock tree; 其好处大致有二:其一是可以及早看到CTS cell 对congestion 的影响, 其二是可以及早精确看到ICG 相关的timing. Early Clock flow 自面世以来已经过上千个设计的检验,虽然Early Clock flow 跟设计强相关,但是对大部分设计都大有裨益,尤其是时钟简单的高性能核。此外Early Clock flow 跟CCOpt 的useful skew 相结合可以进一步改善PPA.

Early Clock Flow 怎么用?

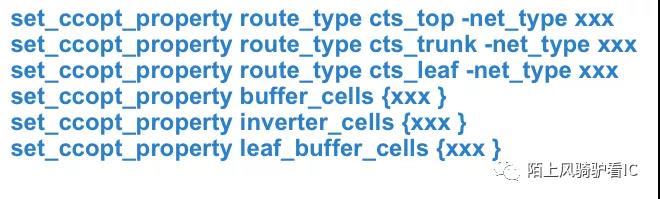

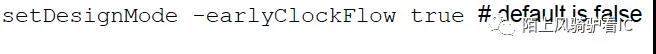

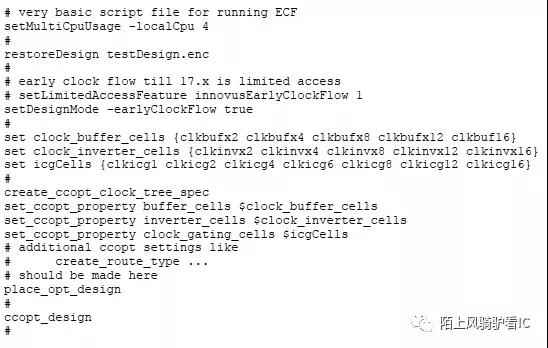

因为Early Clock Flow 是在place\_opt\_design 中调用fast CCOpt CTS clustering, 所以必须在place\_opt\_design 之前将CTS 的设置设上,如:

然后在place\_opt\_design 中将Early Clock Enable:

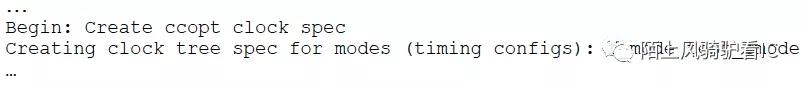

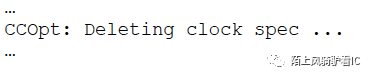

在Innovus 里做CTS 需要clock tree spec, 可以读入一个已有的spec 或用命令create\_ccopt\_clock\_tree\_spec 创建一个spec. 如果没有读入也没有创建spec, Innovus 在place\_opt\_design 的时候会自己创建一个spec 并且在place\_opt\_design 结束时将其删除。在log 中可以找到如下信息:

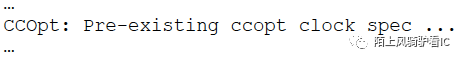

如果db 中已有了spec 则会在log 中找到如下信息:

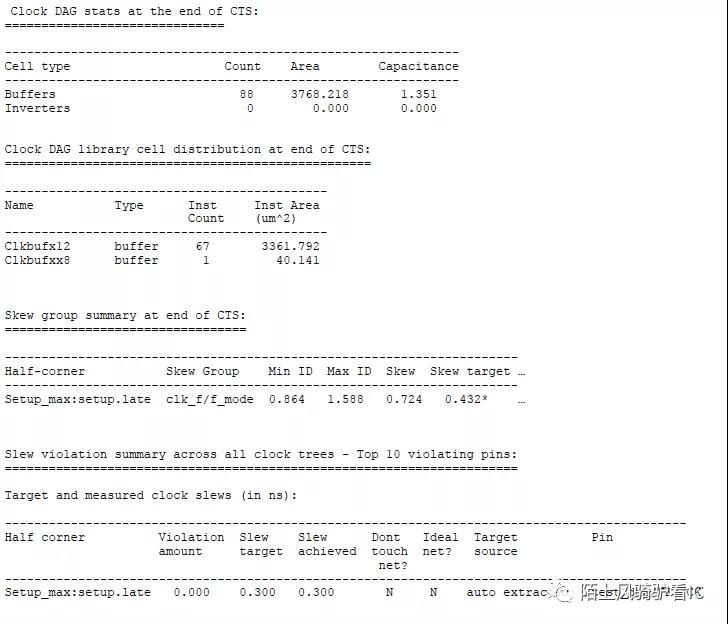

place\_opt\_design 创建了CTS spec 之后,先会做一次global placement, 然后build clock tree. 在log 中找DAG (Directed Acyclic Graph) 可得到:

- Number and type of buffers and inverters used for the clock tree

- Clock tree wire lengths for top

- trunk and leaf nets

- clock net violations

- skew group summary together with its minimal, maximal insertion delay, skew, skew targets

Clock Tree build 好之后,工具会在如下步骤间多次迭代:

- incremental placement

- timing optimization

- useful skewing

- congestion repair

- power optimization

在log 中会看到如下信息:

Early Clock Flow 结果呈现

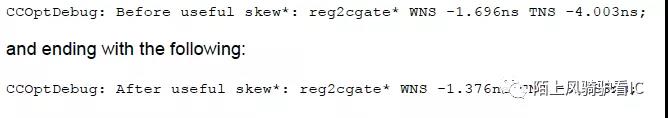

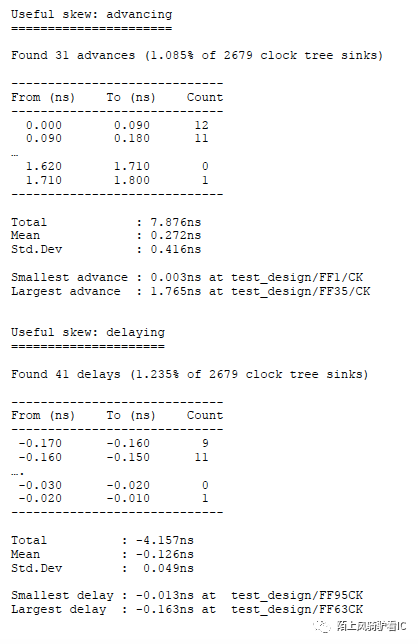

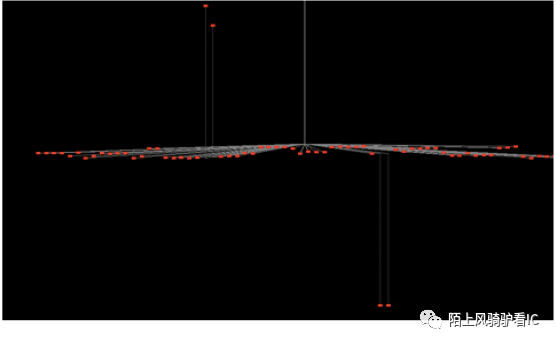

如果enable 了Early Clock Flow 在place\_opt\_design 的log 中会找到许多跟CCOpt 相关的信息,在place\_opt\_design 结束时会将useful skew advancing 和Delaying 的信息写到log 中,也可以用report\_ccopt\_pin\_insertion\_delays 报出相应信息。

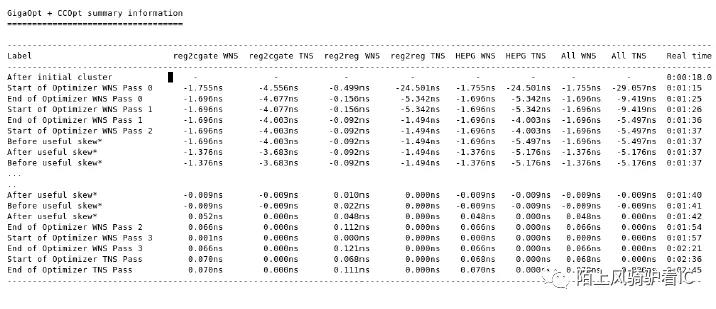

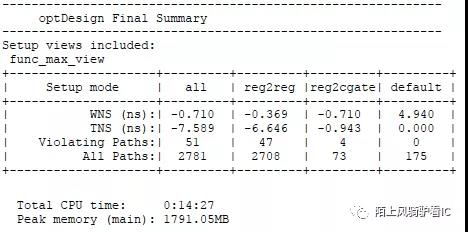

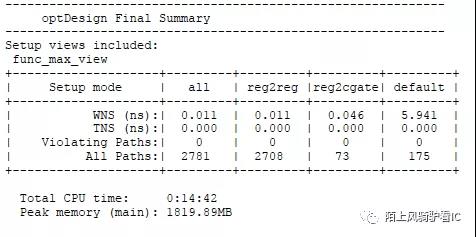

如果同时enable 了Early Clock Flow 和Useful Skew, place\_opt\_design 结束时会生成一张如下的summary table:

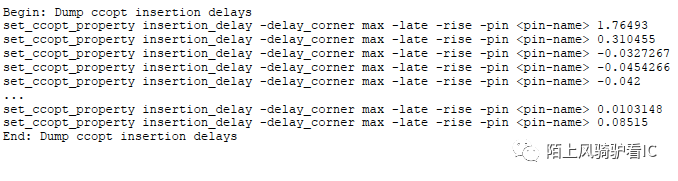

同样可以在log 中找到insertion Delay 的信息:

如果enable了 Early Clock Flow, place\_opt\_design 之后report timing 展开clock path 会看到在clock path 上已经有了真正的clock tree cell. 但是由于clock network 是ideal 的所以在timing report 中看到的clock cell delay 都是0. insertion delay 会用命令set\_clock\_latency 以latency 的形式写到下面文件中:

\<DB>/mmmc/views/\<view>/latency.sdc

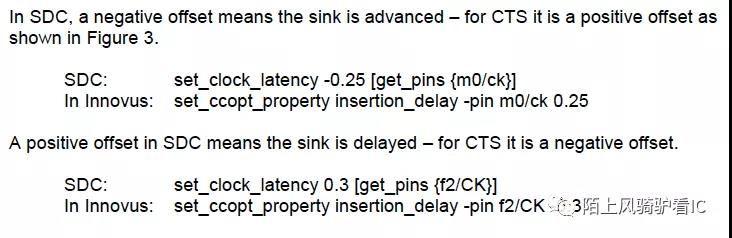

如果enable 了Early Clock Flow, 在ccopt\_design 之前不要做reset\_cts\_config 或reset\_ccopt\_config, 否则前面的insertion delay 值会被删掉。Innovus 读入latency.sdc 后,会将set\_clock\_latency 转化成命令set\_ccopt\_property insertion\_delay. 但是需要注意的是,在set\_clock\_latency 命令中,负值表示往前推clock, 正值表示往后推clock; set\_ccopt\_property insertion\_delay 正好相反,负值表示往后推clock,正值表示往前推clock, 其对应关系是:

ccopt\_design 会将place\_opt\_design Early Clock Flow 中插入的clock tree cell 都删掉,并重新build tree. 如果在run ispatial flow 时enable 了Early clock flow, 在Innovus 中不论是netlist handoff 的full place\_opt\_design 还是db handoff 的incremental place\_opt\_design 都不会删掉前面build 的clock tree cell, 数据交互同样是用set\_clock\_latency.

举个栗子

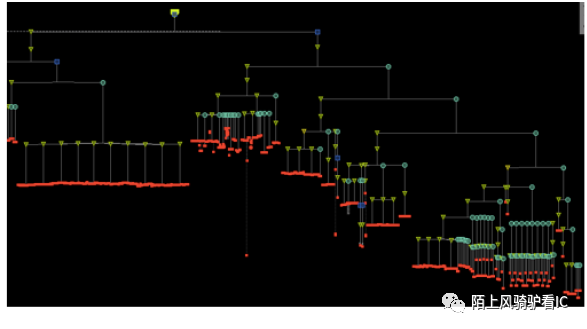

这是一个简单的设计,这个设计没有congestion 问题,但是有ICG timing 的问题。

- run1 without Early Clock Flow

- run2 with Early Clock flow

place\_opt\_design 之后可以用clock tree debugger (CTD) 来显示clock tree 及insertion delay.

最后一点

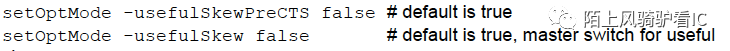

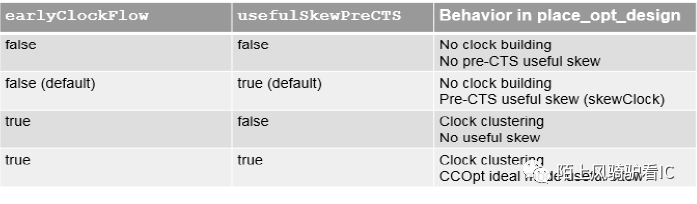

在Ispatial flow 里除了Early Clock Flow 也有useful skew 的控制,useful Skew 在place\_opt\_design 中默认是开启的,可用如下变量控制:

Early Clock Flow 跟useful skew 是相对独立的。

作者:陌上风骑驴

来源:https://mp.weixin.qq.com/s/dlOVs1he0Ao2SaHaK5nZ2g

作者微信公众号

相关文章推荐

•大牛访谈:DFT一哥老K

•STA | Logical DRC

更多IC设计技术干货请关注IC设计技术专栏。