Clock gating 应该算得上IC界十大高频词汇,也是Icer 入行之初最早接触的重要概念之一,但是它并不简单。在数字电路整个设计流程中,它都要被特殊对待,如Coding 时需要考虑什么样的代码风格会使gating 的效率更高;综合时需要特别设置要插入的gating 类型,每个gating 的fanout 范围,是否可以跨层次,是否需要做physical aware 的gating;DFT 时需要确定clock gating 的TE pin 如何连接以保证在DFT 模式clock 可控;P&R 时需要考虑gating 的位置是否合理,是否由于物理上相互拉扯做gating 复制,是否需要人工约束某些关键gating 的位置,CTS 是否需要对gating 做特殊处理;形式验证时需要对gating 做特殊建模;STA时需要明白工具在什么情况下会映射出clock gating 的check, 哪些是真实的clock gating 哪些又是假的clock gating。

目前,网上不乏对clock gating 的描述跟讨论,但驴仍觉得有必要以自己的理解写几篇短文对其做一陈诉。从ICG cell 在library 中的定义说起。

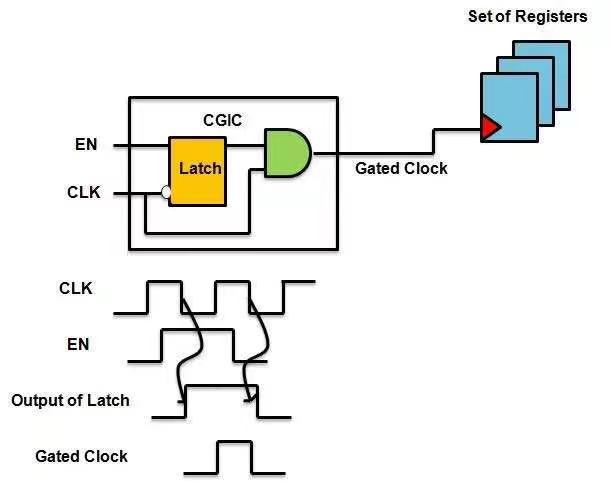

到目前为止,Clock Gating 仍是减小动态功耗最有效的办法;在数字电路中clock 是翻转最频繁的信号,而且每个clock 的fanout 巨大,但是并不是每个寄存器在每个周期都需要更新状态,实际情况是大部分寄存器在大部分时候都只要保留当前状态即可,在寄存器不需要更新状态时的时钟翻转就是八十岁婆婆拜堂,白费一对蜡。于是聪明的Icer 发明了Gating 这一技能,在不需要时钟翻转的时候就把时钟关掉,据统计这一技术可以减少20%的动态功耗。Clock gating 并不是一日长成今日这般模样,经过各种摸索尝试之后,时至今日使用最广泛的clock gating cell 就是glitch free 的Integrated clock-gating cell (ICG). 目前主流工艺Foundry 提供的库中都有ICG cell.

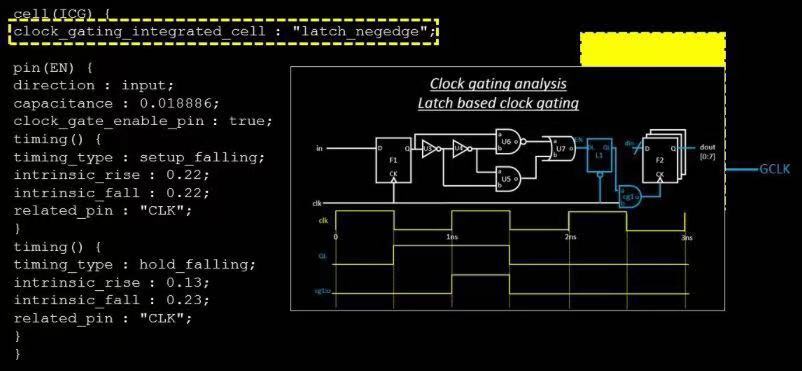

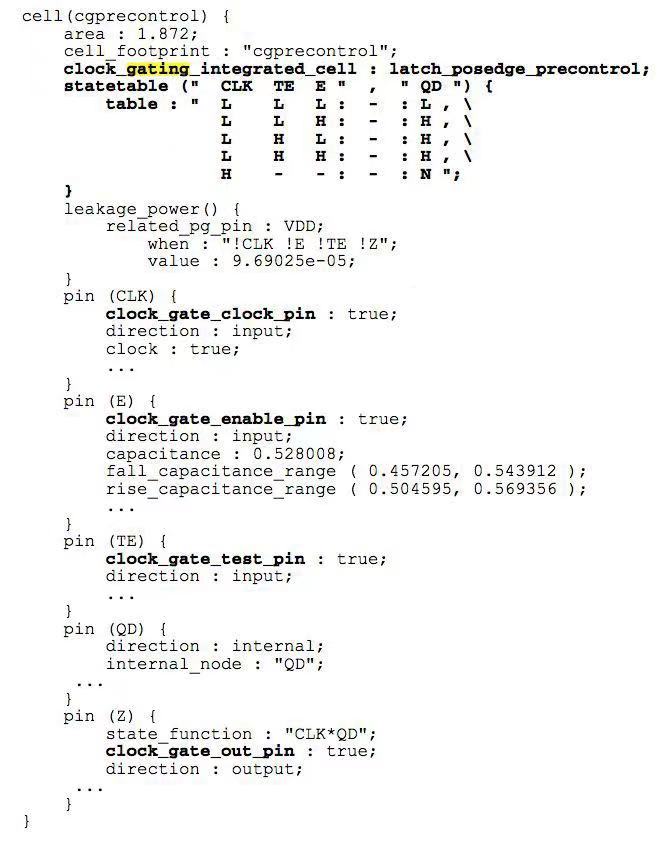

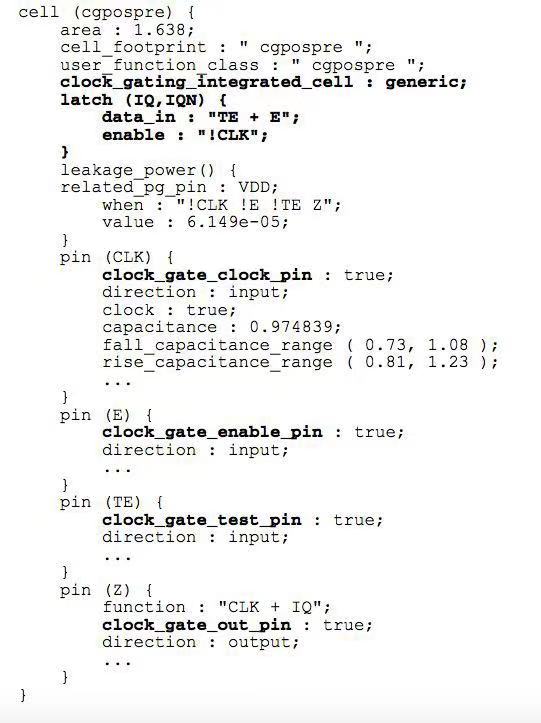

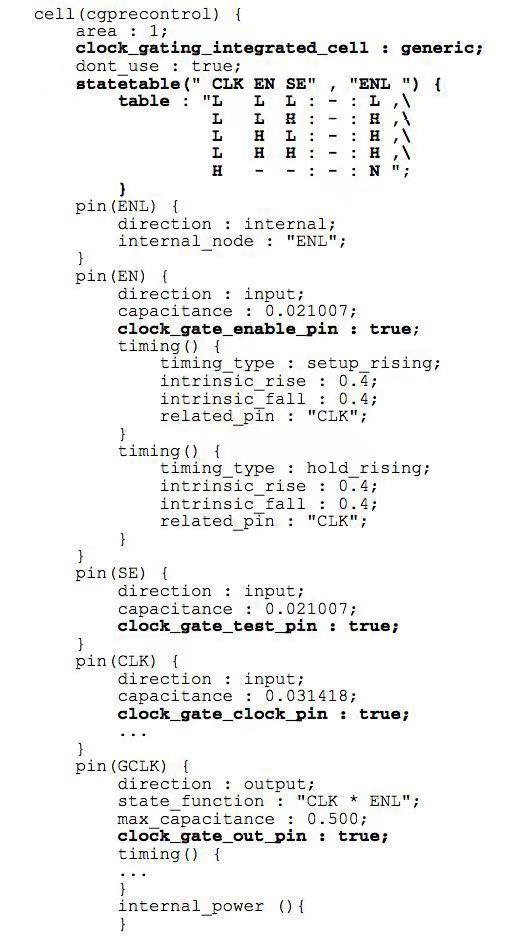

以上是一个典型的ICG cell 在库中的定义,相较于其他cell 关键的attribute 有两部分:

- clock\_gating\_intergrated\_cell

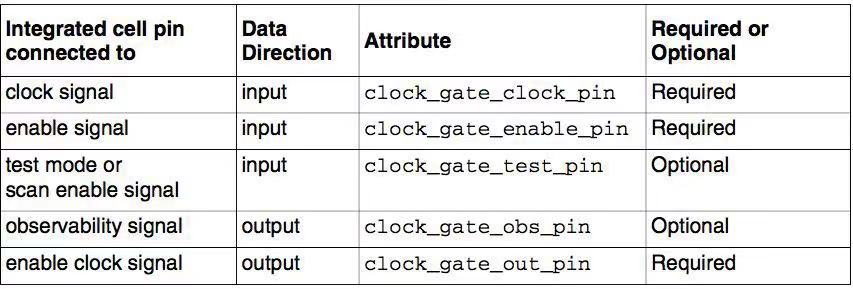

- clock gating pin attributes

Clock gating pin attributes 通常有以下几种,在library 中各个pin 定义时予以指定。

clock\_gating\_intergrated\_cell 是library 中cell 的属性,它可以取两个值:

clock\_gating\_integrated\_cell \_: {string | generic} \_

String:

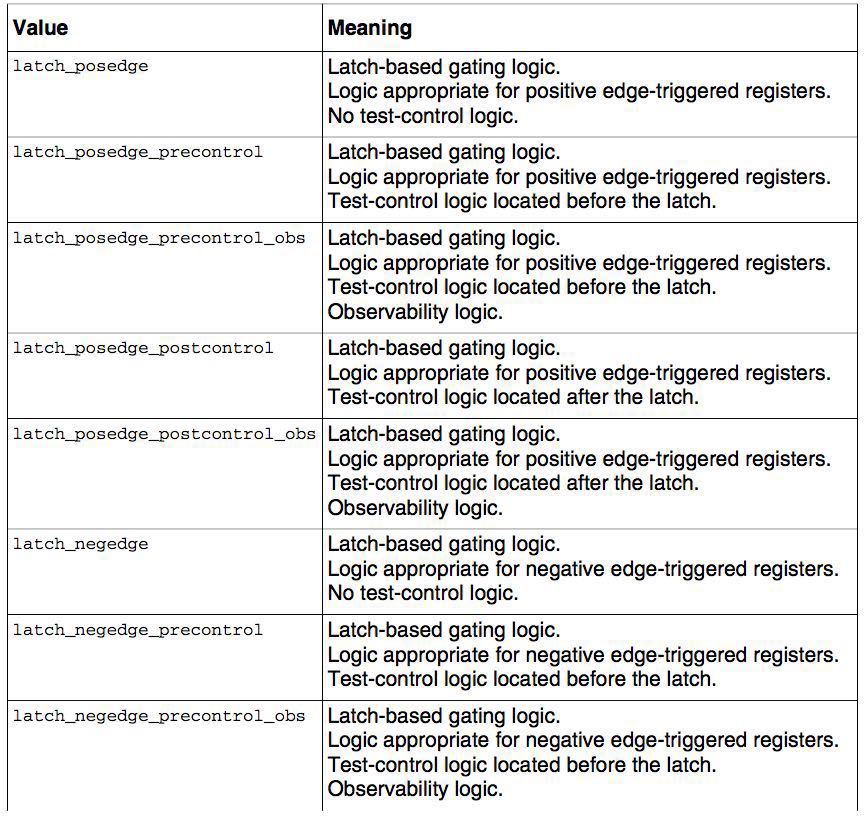

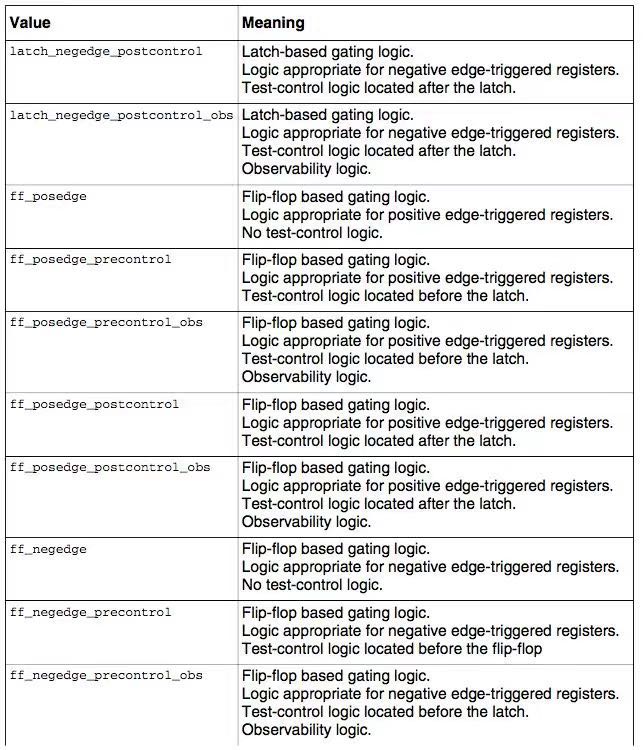

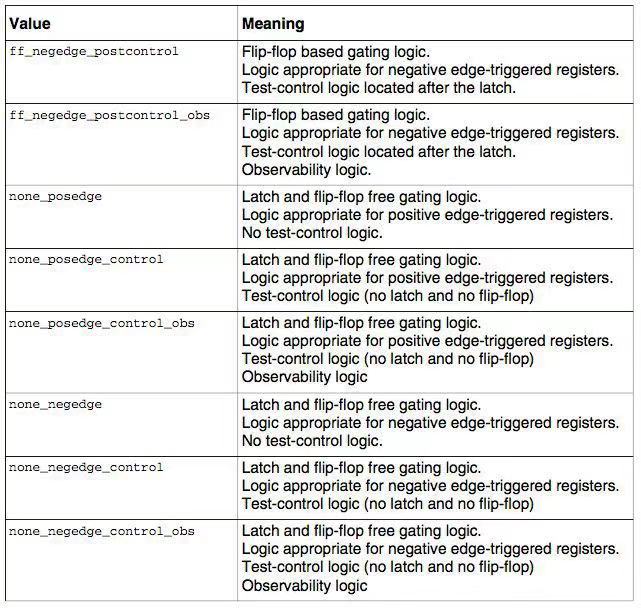

是一个由2\~4个关键词组成的值,如:latch\_negedge\_precontrol\_obs,String 所有可能取值参见文末的表格。

- string 的第一个关键词表示sequential cell 的类型,有效值是:latch, flip-flop, none;

- string 的第二个关键词表示要控制的寄存器是上沿触发还是下沿触发,有效值是:posedge, negedge.

- string 的第三个关键词可选,表示测试控制信号是在sequential cell 之前、之后还是没有;对于latch 或flip-flop 有效值是:precontrol, postcontrol, no. 如果ICG cell中没有sequential cell 有效值是:control, no.

- string 的第四个关键词可选,只有设置了第三个关键词才需要设置这个关键词,表示是否要观测内部逻辑,有效值是:obs, no.

如果clock\_gating\_intergrated\_cell 取值是string,那么该ICG cell 在library 中必须有state table 跟 state function 的定义。

——题外话,之前没有深入研究过ICG cell 在库中的定义,前段时间还在驴群里问过,为什么ICG cell 的function 是"state\_function : "CLK*QD";" 为什么用一个internal pin QD 来定义?这个QD 就是ICG 内部sequential cell 的输出,它的值由输入CLK, TE, E 决定,在library 中由state table 定义。

Generic:

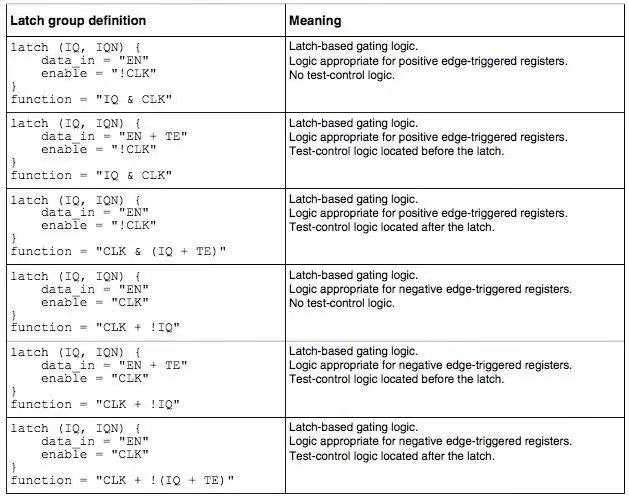

如果clock\_gating\_intergrated\_cell 取值是generic,那么在library 中该ICG cell 的function 既可由state table 定义,也可由latch group 定义。各类型latch group 的意思请参考文末表格。

- 如果function 由latch group 定义的,该ICG cell 内部只能由latch 来实现。

- 如果function 由state table 来定义,该ICG cell 内部既能由latch 来实现也能由flip-flop 来实现。

有些库中会使用"AND", "OR" 等组合逻辑做clock gating cell,在库中用attribute:

is\_clock\_gating\_cell 来标示。同时cell 的每个pin 的attribute 也必须要予以明确定义。

附表一:String 所能取的值

附表二:latch group 所有形式及意义

作者:陌上风骑驴

来源:https://mp.weixin.qq.com/s/n8w9BB7V20z4mP75RTGS-Q

作者微信公众号

相关文章推荐

• 论功耗 | 如何计算toggle rate

•论形式验证 | KeyPoint

更多IC设计技术干货请关注IC设计技术专栏。