Power-Plan或者说PG如何打,这是一个仁者见仁智者见智的问题,没有一个标准的答案,因为有各种各样的影响因素。本文将列举一些可能的影响因素:

和design相关

- 如果design的utilization很低,那就能打多密就打多密。utilization很高,打PG的时候就得考虑会不会让信号线走线变得困难,即产生congestion或者DRC。

- 对于同样的utilization,同样的PG结构,交换机模块的congestion肯定比其他模块的congestion大。所以对于这种特殊的模块,就得仔细调整PG的结构。

- 对于功耗要求不同的design,如手机芯片和电脑芯片,因对功耗的要求大不一样,所以PG结构也大不一样。

和sign-off标准相关

- sign-off标准包括static-IR-drop和dynamic-IR-drop,不同的design对这个标准要求不一样,基于不同的标准,对PG结构的要求也不同。

- sign-off的时候需要根据某个工作场景的activity 文件,进行功耗跟IR分析,常用的activity文件格式有:VCD (Value Change Dump file) , FSDB, SAIF(Switching Activity Interchange Format)。即使同一个design,不同工作场景的activity文件产生的IR-Drop也大不一样。

先入经验

- 一般PG结构的选择是基于先前的项目经验。但随着工艺不断进步,之前的经验并不一定是最优化的也不一定适用于当前工艺。

- 40nm工艺以上一般只用M1做rail,但是在先进工艺下,M1的电阻率比较高,由M1造成的IR-drop比较大,而且占主要的因素。所以可能就需要M2也作为rail,所以先入经验要随着工艺的改进做调整。

和选择的工艺和金属层数有关

- 不同的工艺,pitch和width大不一样,采用LVT或者HVT等造成的功耗也大不一样,不能直接像工艺尺寸一样简单的shrink。

- 即使同一种工艺,也可以选择不同数目的金属层。少一层金属就省一层mask,就省一笔钱。比如40nm工艺,如果选用8层金属,流片一次可能需要100W,如果选用7层,流片一次则需要95W。单看可能差别不是很大,但是如果量很大很大,节省的成倍就十分可观了。

- 选择不同的金属层,PG结构自然不同。

对PG进行微调

PG怎么打,这是每个公司的机密,作者也不能讲很多,一般是先初略的打一版看,然后在signoff工具中看看结果,再基于该结果和congestion的情况再进行调节。下面讲讲对给定的PG结构,在保证同样的IR-drop的情况下,如何通过微调,来省出更多的绕线资源,减小congestion或者基于同样congestion的情况下,可以额外的增强PG结构,降低IR-drop。

微调的原理是什么?

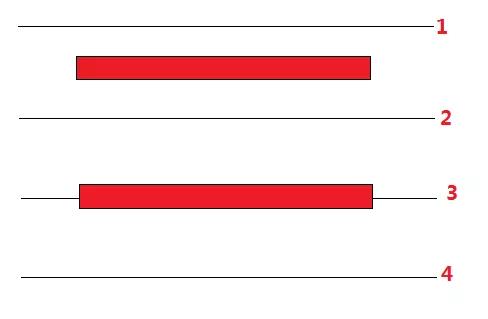

在新工艺下signal-routing都是在track上走线的,不会发生在半track上走线的情况。例如下面画了4个track,2条走线。在老的工艺下,完全没问题,想咋走咋走,只要满足min-spacing就好了。但是在新的工艺下,就得规规矩矩的,每条走线都必须在track上(这里只是说signal-routing必须在track)。

必须在Track上有几个方面的原因吧:

- spacing是一个离散的值。在老的工艺下,无限长且平行的两条走线,只要spacing是大于某个值的就没问题,可以是任意的浮点数。但是在新的工艺下,大于某个值不准确,spacing是一个离散的值。例如spacing的表格是0.1,0.2,0.3,如果spacing小于0.3,那么只能选0.1和0.2两个值,如果spacing大于0.3,则可以是任意浮点数。

- width也同理,也是一个离散的值。

- 很多DRC规则都是基于这种离散的值的,不仅仅是这种简单的spacing/width,所以p不仅仅是违反了这一条,后面还有更多的DRC等着你。

- 新的工艺都采用了double-pattern,走线不在Track上,后面在分不同mask的时候会有问题。

上面说到走线必须都在track上,更准确的说法是为了减少各种可能的DRC,工具走signal-routing的时候都在track上,因为PR工具看不到所有sign-off的DRC-rule,所以不能也不敢乱走。我们自己打PG的时候还是可以随便打,只要没有DRC违规就可以了。

这些因素虽然不会影响IR-drop,但是却可以通过调节这些因素,能够减小congestion或者基于同样congestion的情况下,可以额外的增强PG结构。

下面就举一个例子,例子中的数据都是作者随便取的,不具有代表性。

原始结构

假设原始的PG如下图所示,中间宽的是PG,两边的是信号走线。

我们来分析分析这个图:

- PG在Track上,没问题

- 取的宽度占用了3个track,没问题

但是,由于各种DRC,额外的2个Track其实也不能用,其实PG占用了5个track。浪费!

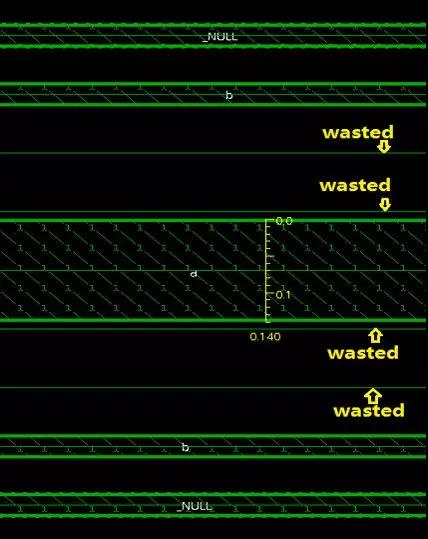

优化方案一

我们就来进行一下优化:既然要占5个Track,干脆PG再宽点不更好吗?

而且PG可以不需要非得在track上,可以在track中间。例如下图所示,不仅加宽了PG,而且居然还能省一个Track!

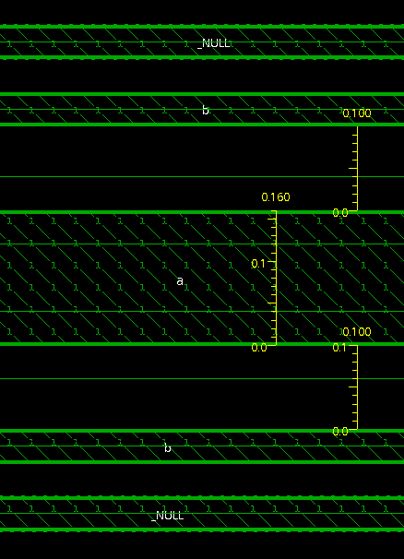

优化方案二

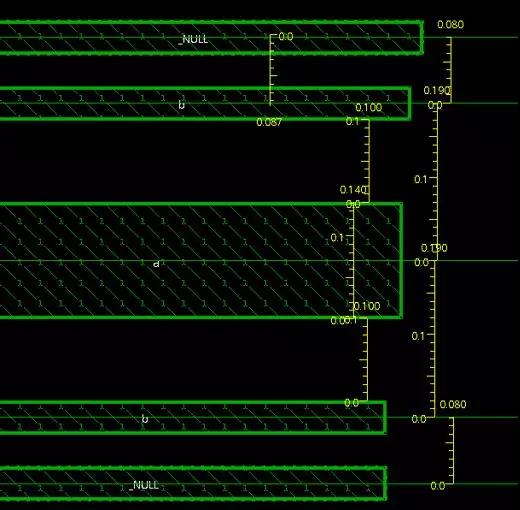

如下图所示,干脆就不要用uniform-track,直接创建non-uniform-track。仍然是用同样的PG宽度,但是却省下了不少的绕线资源。

作者:陌上风骑驴

来源:https://mp.weixin.qq.com/s/kdcA9PkvCPbDCzOHouhyiw

作者微信公众号

相关文章推荐

更多IC设计技术干货请关注IC设计技术专栏。