作者:唐僧 huangliang

来源:企业存储技术

在看到这几份资料之前,如果有人问我“_企业级__SSD__有使用SLC Cache__技术的吗?_”我会比较确信地回答“否”。

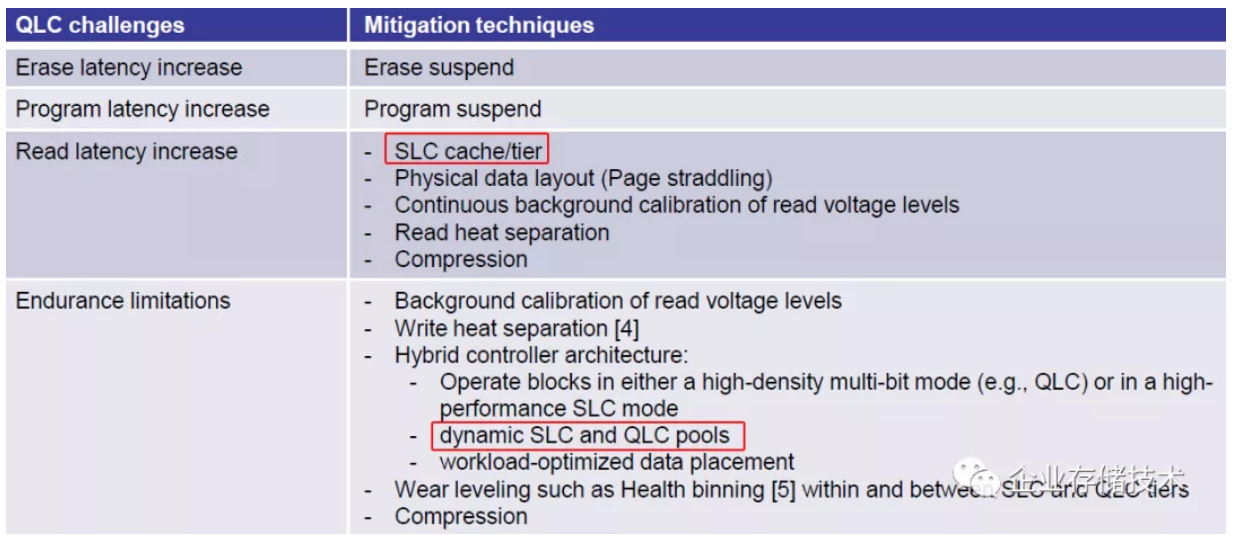

尽管在TLC等多级NAND闪存上模拟出部分“SLC”容量用于写性能加速,在消费级SSD已经相当普遍,其价值和限制我在《PCIe 4.0 SSD__测试:接口、散热和CPU__对性能的影响》一文中也写的很清楚了。但企业级数据中心应用负载毕竟不同,无论随机还是顺序写入时间一长,SLC缓存区域写爆之后其优势就不再了,“二次写入”有时对性能和寿命甚至有负面影响。

QLC NAND 闪存的局限

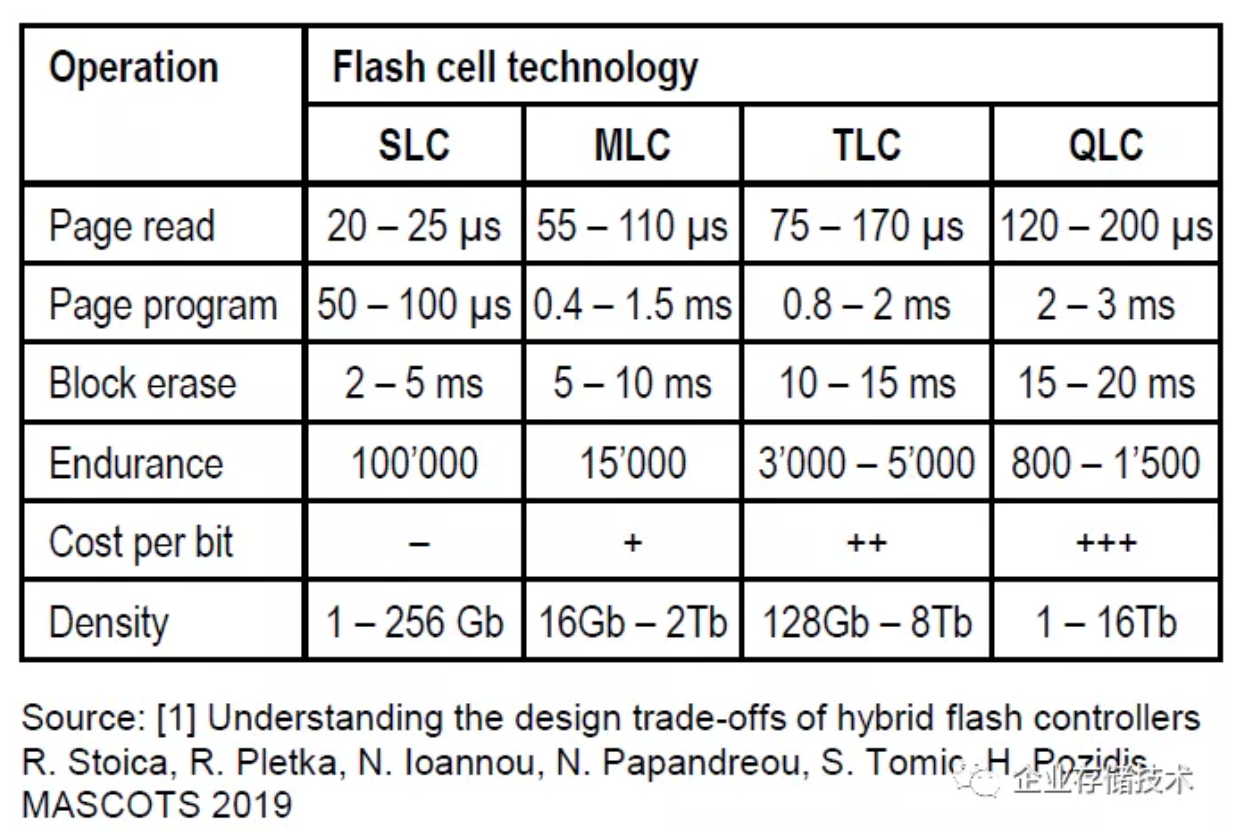

注:这里Page program__时间的增大还有一个因素,就是闪存的页面大小也在不断扩大。

上面表格只是一个粗略的对比。我们看到从SLC、MLC、TLC一直到QLC,在闪存页面读(延时)、页面编程(写)、块擦除时间、耐久度(P/E Cycle)方面都是越来越差的。QLC 800-1,500次的擦写周期大约只有TLC的1/3。

我在上一篇《3D NAND__制造技术对比:YMTC__国产闪存何时追赶上?》中提到:“QLC预计在2025年将占到NAND整体出货容量的50%”,原因是成本方面的优势和颗粒密度。

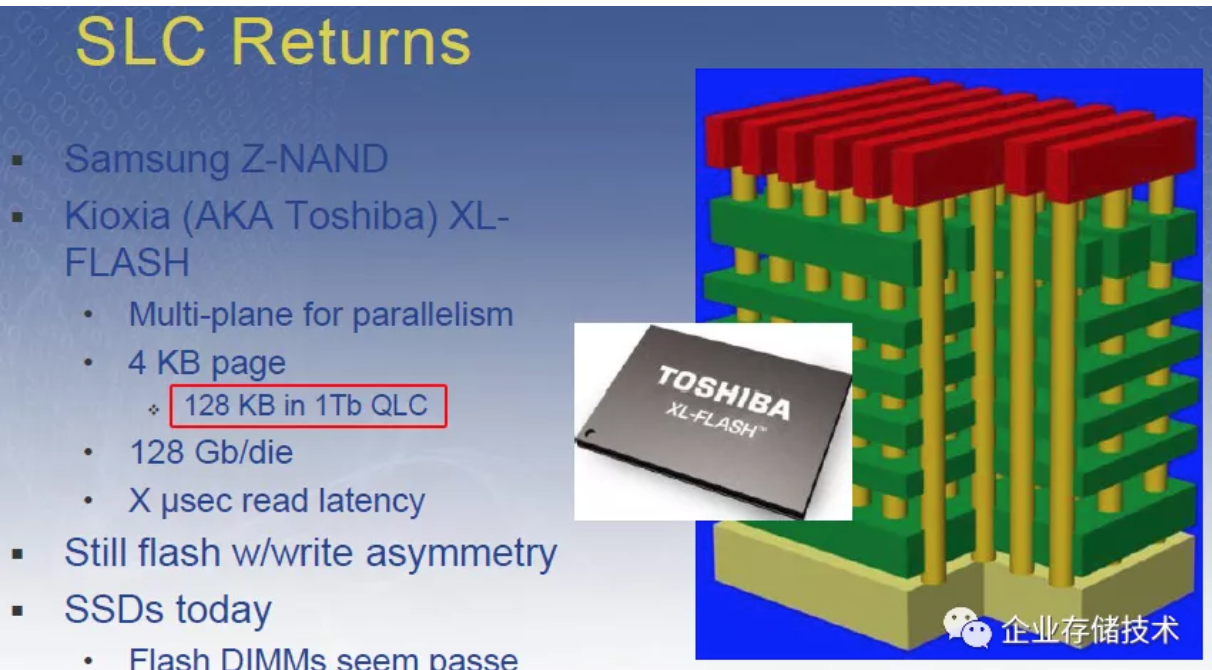

上图本来是介绍三星Z-NAND和Kioxia XL-Flash这些高性能低延时“SLC”闪存,其中XL-Flash的页面大小恢复到NAND早期的4KB。如今主流MLC/TLC闪存已经普遍增大到8KB-16KB page,而1Tb QLC的页面甚至加大到了128KB。

我们知道page是闪存最小的写入单位。当然这并不意味着在QLC SSD上写入4KB数据,到底层闪存上都会放大到128 KB这么多,因为在SSD上还有写缓存和FTL映射表可以做合并写入。

*Intel D5-P5316的64KB*重定向单元设计

**

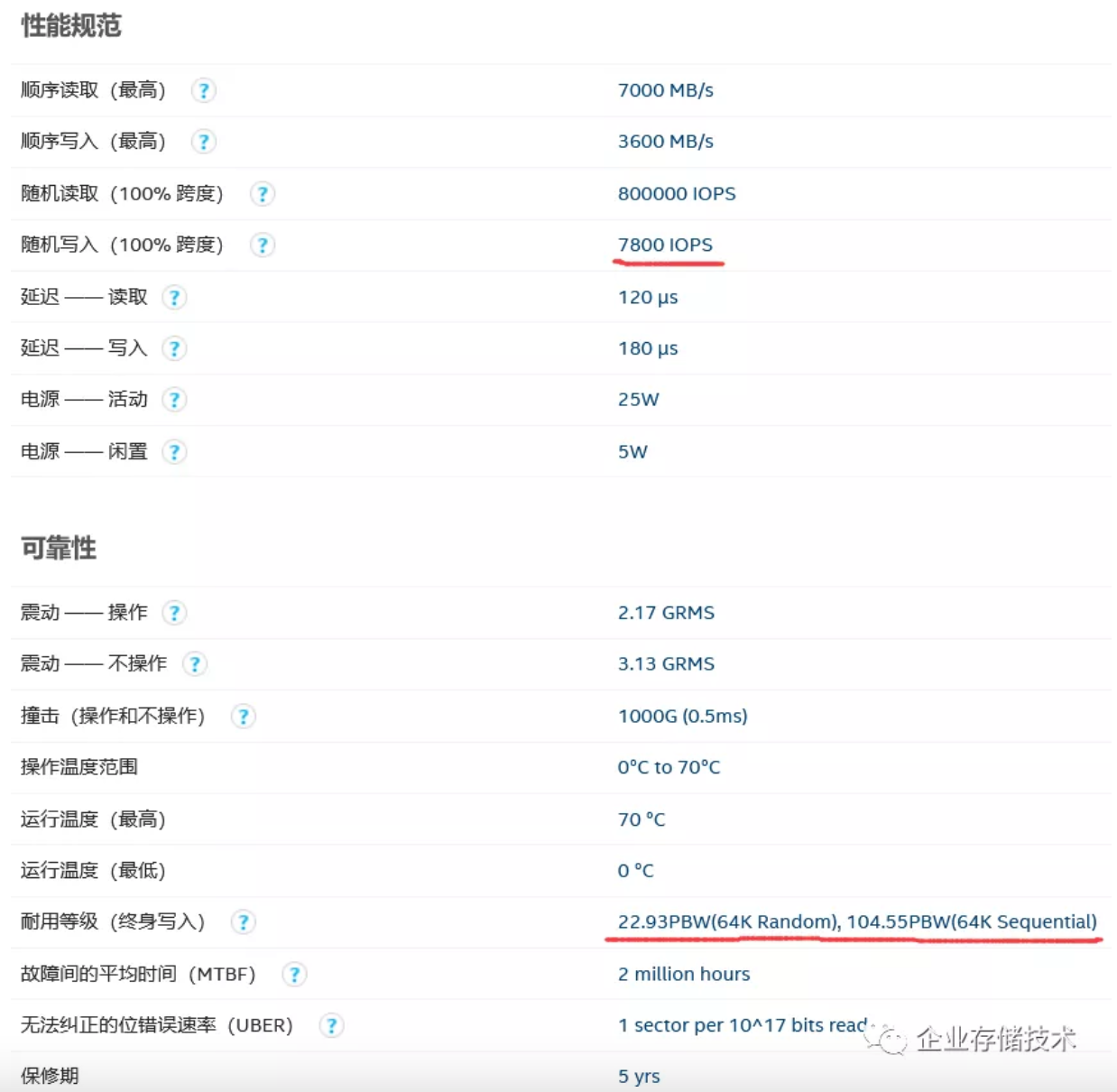

Intel SSD D5-P5316属于较早上市的企业级QLC闪存盘之一。在它的Product Brief里随机写性能只写了64KB,写寿命为0.41 DWPD。

点击图片后可放大(以下同)

进一步看网站上的规格,可以了解到P5316的全盘随机写IOPS只有7800(指的64KB,如果4KB由于“读-改-写”放大会较差)。30.72TB型号的终身写入量列出了22.93PBW(64K随机)和104.55PBW(64K顺序)2个数值,这个背后则是GC垃圾回收时产生的写放大。

通过计算不难得出,0.41 DWPD实际上对应的是64K随机写,如果换成顺序写寿命应该就是5倍的2 DWPD。

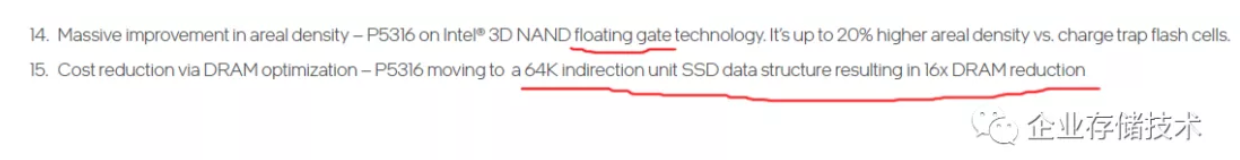

Intel__表示floating gate__浮动栅极闪存技术比CTF__单元提高了20%__密度,有朋友告诉我二者还将保持长期竞争态势。

Intel P5316定位是低成本、高密度,用于存放相对冷数据的SSD。它为了降低成本,将FTL映射表的indirection unit SSD数据结构从4KB加大到64KB,这样减少了16倍DRAM内存容量的需求。我理解小于64KB的写入也都只能占用64KB了,如果使用的场景不合适其寿命将达不到0.41 DWPD,这一点冬瓜哥之前的文章也指出过。

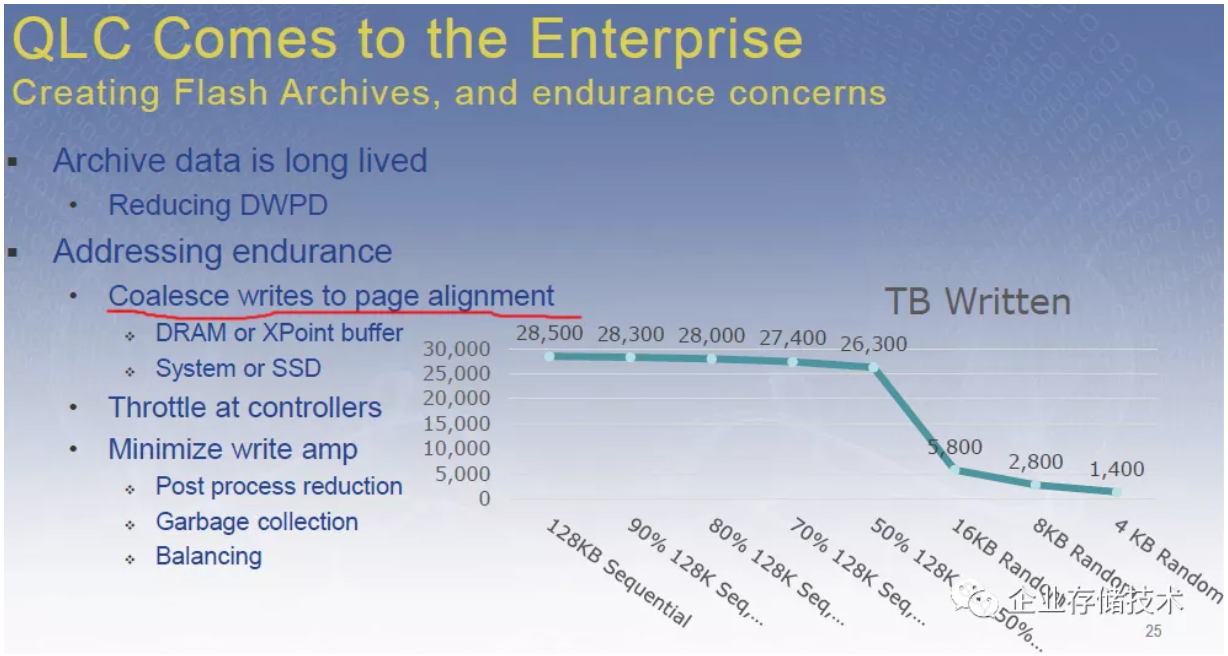

如上图曲线,当QLC的写I/O从128KB顺序减小到4KB随机,其写耐久度也可能下降20倍。改善的方法有一个就是合并写入对齐到页面,这时可以考虑用DRAM或者3D XPoint Memory充当buffer缓冲,具体实现可以在SSD内部或者是系统级(如:闪存阵列)。

要是在SSD上用DRAM或者3DXP做缓冲,容量不可能太大。那么把一部分QLC模拟成SLC,在企业级SSD上是否可行呢?

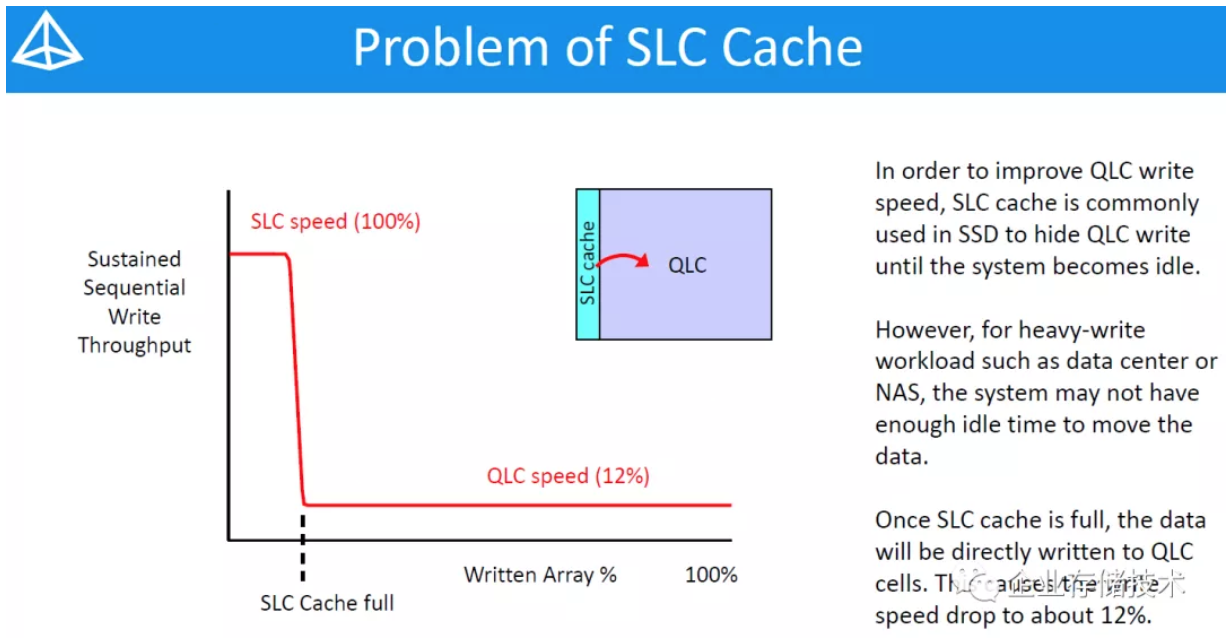

如果按照一般消费级SSD的算法,当持续的顺序写入把SLC Cache填满之后,QLC的速度可能下降到只有之前的12%。根据传统认知,这在高性能闪存阵列上是不太容易被接受的。

IBM FlashCore Module QLC的动态SLC分配技术

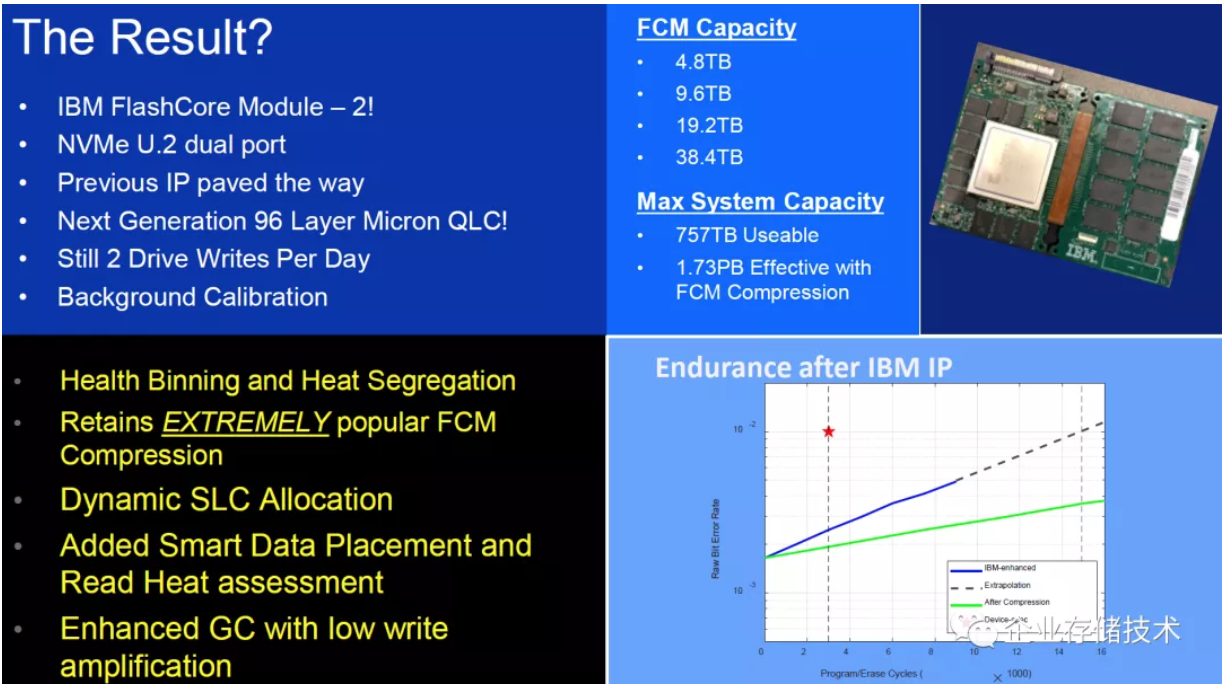

大家可能听说过IBM在FlashSystem闪存阵列上,用FPGA做主控研发过SSD。上图列出96层美光QLC闪存的,应该是NVMe U.2外形FlashCore Module的第二代。

放大后查看:右下方的蓝色线条代表IBM增强后QLC P/E Cycle寿命可达9,000,考虑压缩效果后相当于16,000,此时Raw Bit Error Rate物理位误码率保持在10 -2以下,应该在ECC/LDPC的纠错能力范围内。“保持2 DWPD”恰好与Intel P5316的64KB顺序写寿命大致相当,也就是说经过动态SLC Cache之后,数据应该都是按照QLC闪存“最舒服的方式”落盘。

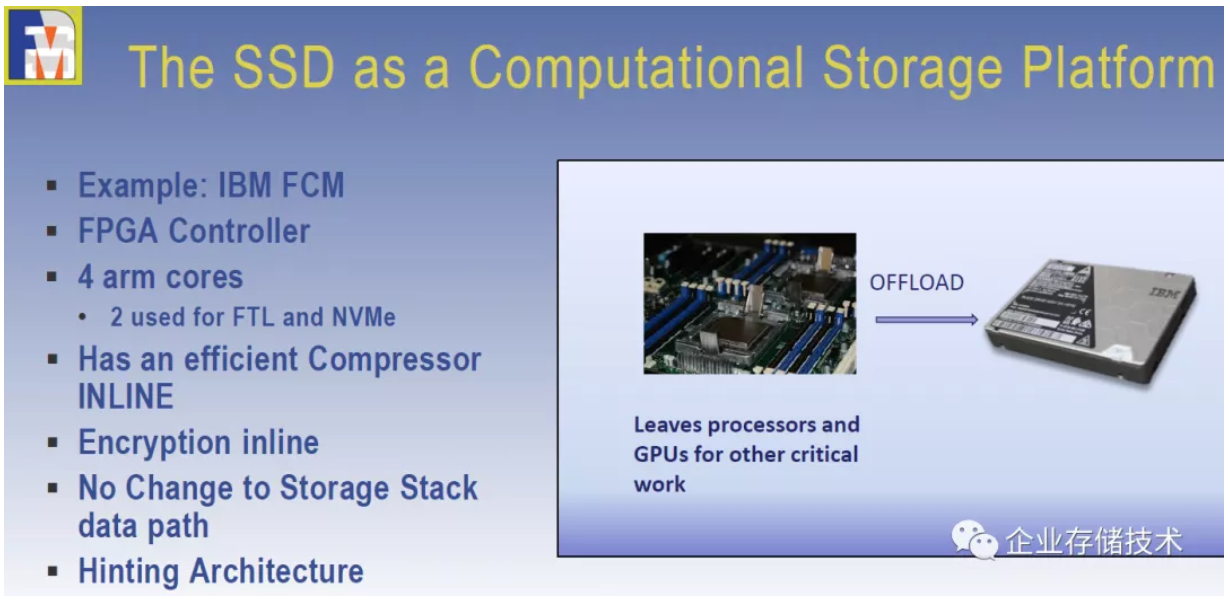

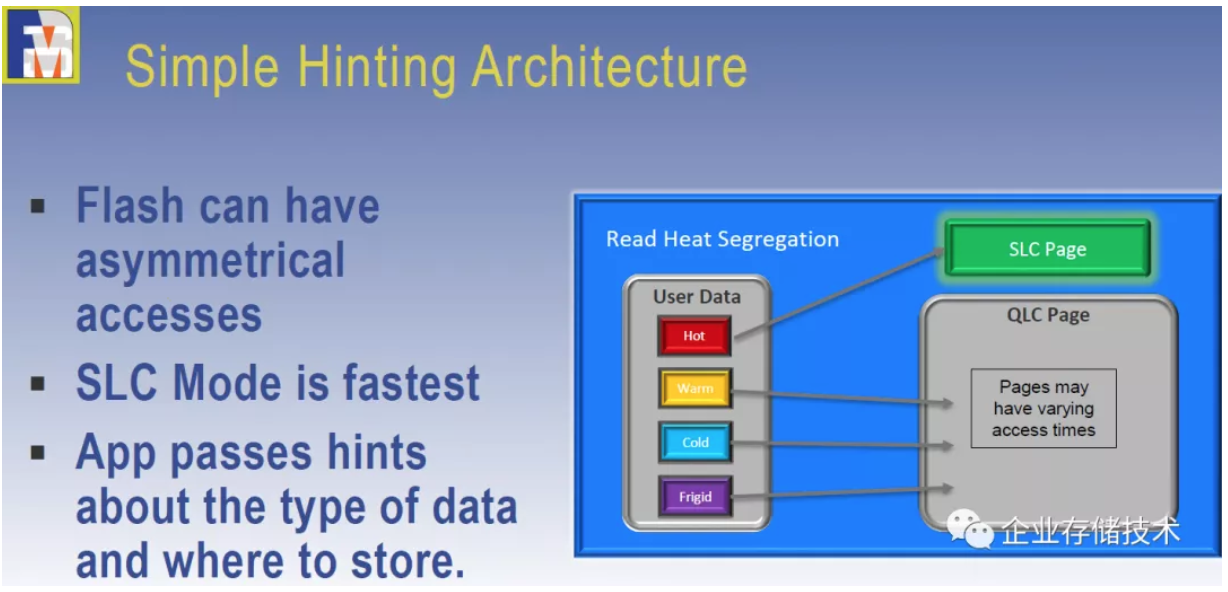

在IBM FCM的FPGA控制器中,4核ARM有2个核心用于FTL和NVMe。“Hinting”架构就是指的动态SLC模式技术。

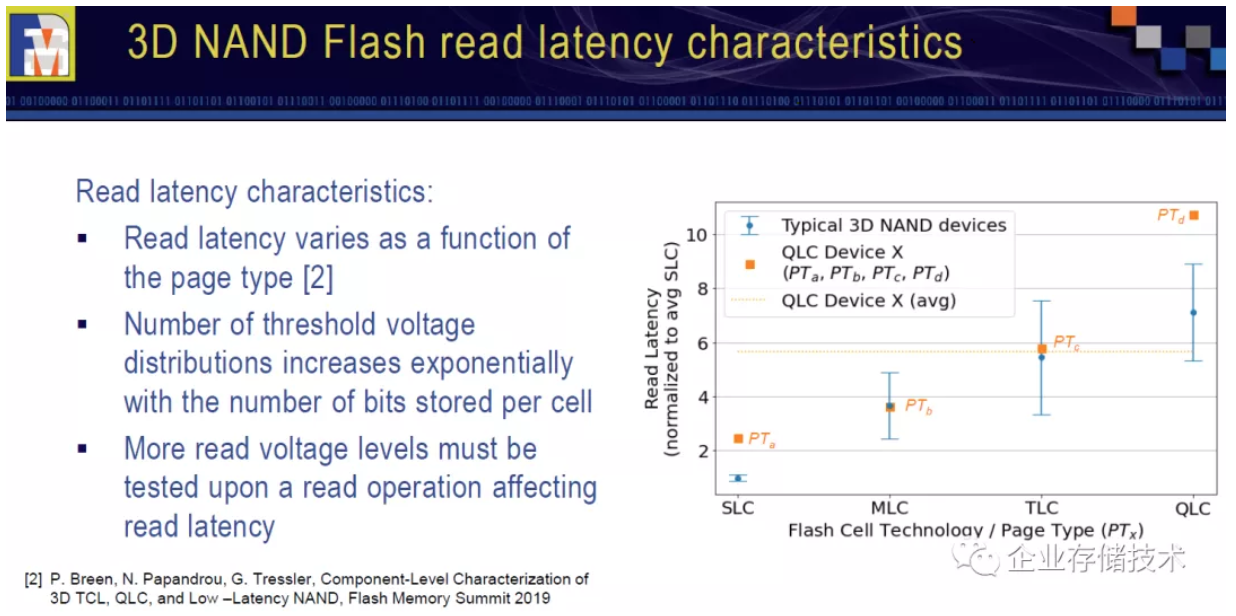

本文开头曾列出过,SLC Page和QLC Page的读性能(延时/访问时间)也是不同的。甚至QLC page内部也可以分级,下图供参考,这一点我先不展开讨论了。

3D NAND__(QLC__)闪存读延时特征

改善读延时只是SLC cache/tier的一部分作用,更多的应该是为了闪存的写寿命。

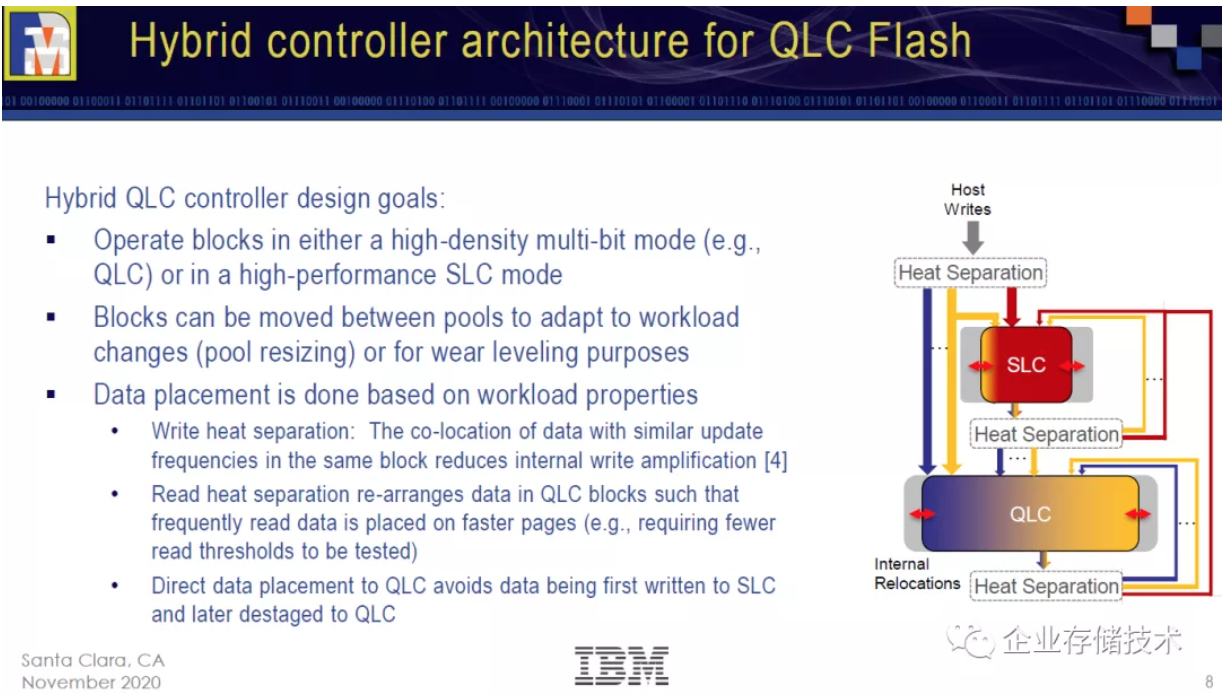

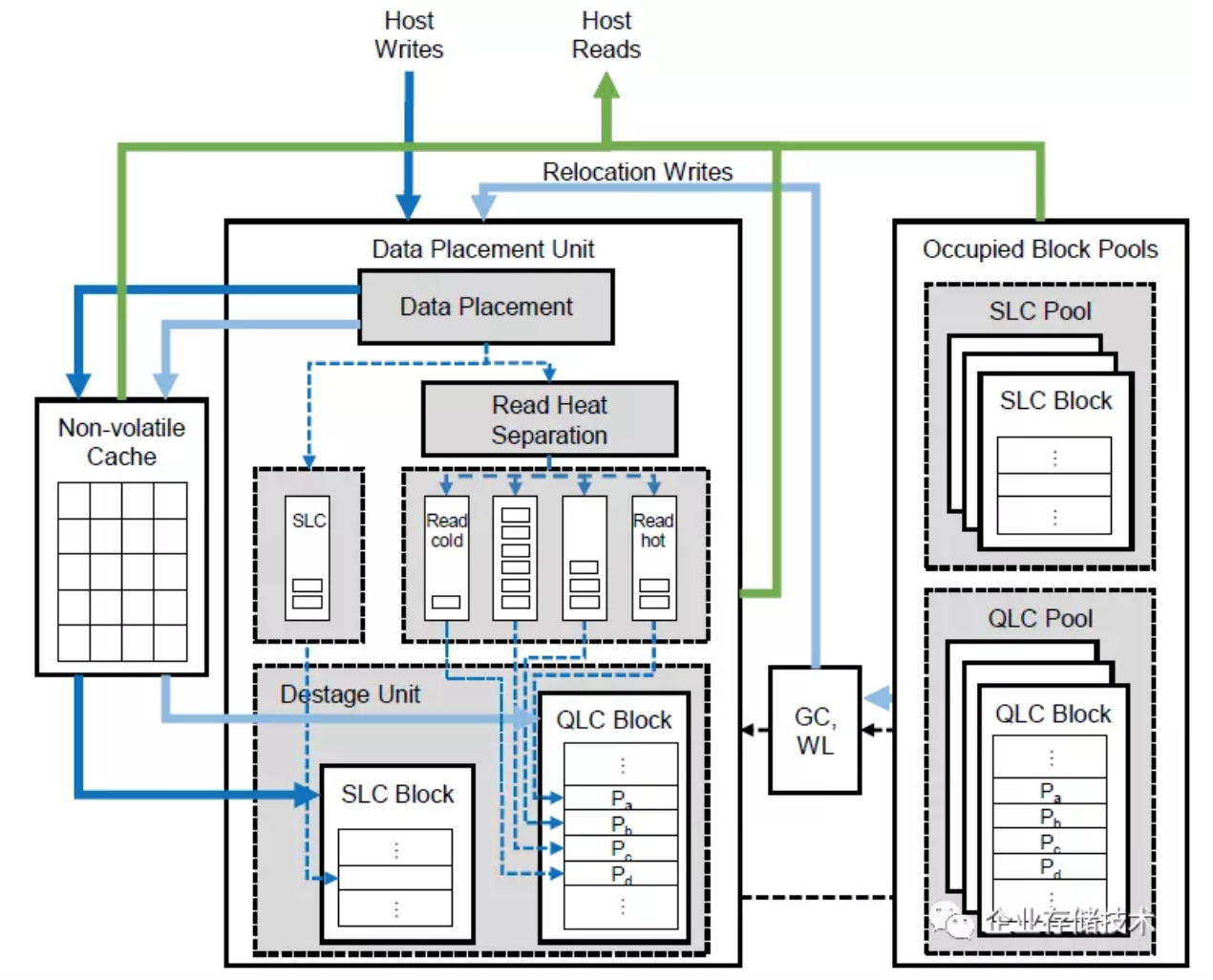

如上面原理图,主机写入数据经过“热分离”之后进入“SLC Cache”或者QLC。这里我理解IBM FCM处理64/128KB及以上的顺序写会直接到QLC闪存,而消费级SSD一般只有在SLC Cache或者整盘写满的情况下才可能直接一步写入到TLC/QLC。

其实这个判断机制倒是不复杂,比如我在若干年前介绍EMC的VFCache主机缓存软件时提到过:“_VFCache__驱动软件除了拦截不超过64KB__大小的I/O__请求(通常为随机操作)并将其缓存到PCIe__闪存卡用于加速访__问__…_”,技术上也有相似之处。

写寿命和性能改善:与SSD容量使用率密切相关

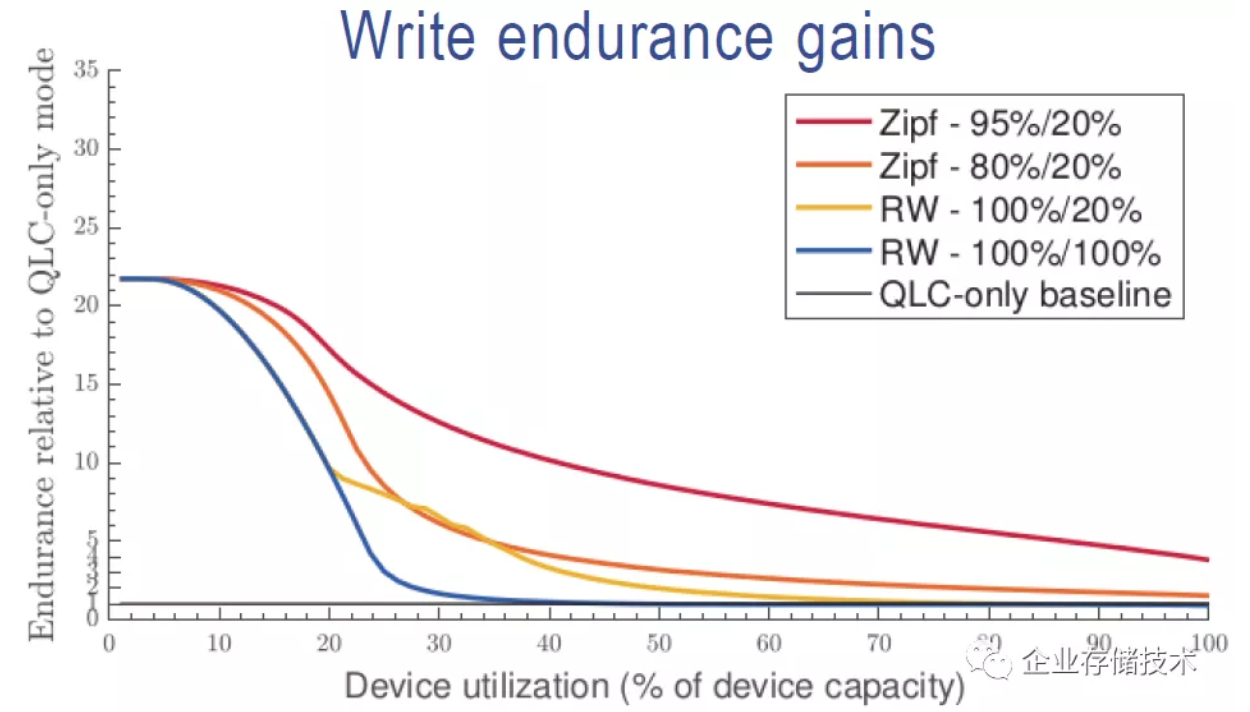

上面图表是IBM给出的写寿命提升,仅供参考。两种Zipf和RW表示不同的数据I/O分布特征。在SSD空盘的情况下效果最好(甚至改善20倍?),随着设备容量逐渐趋于写满,提升的幅度也会下降。我理解如果都是100%的随机写,容量占用到一定比例之后,这个写寿命就和QLC本身的基线一样了。

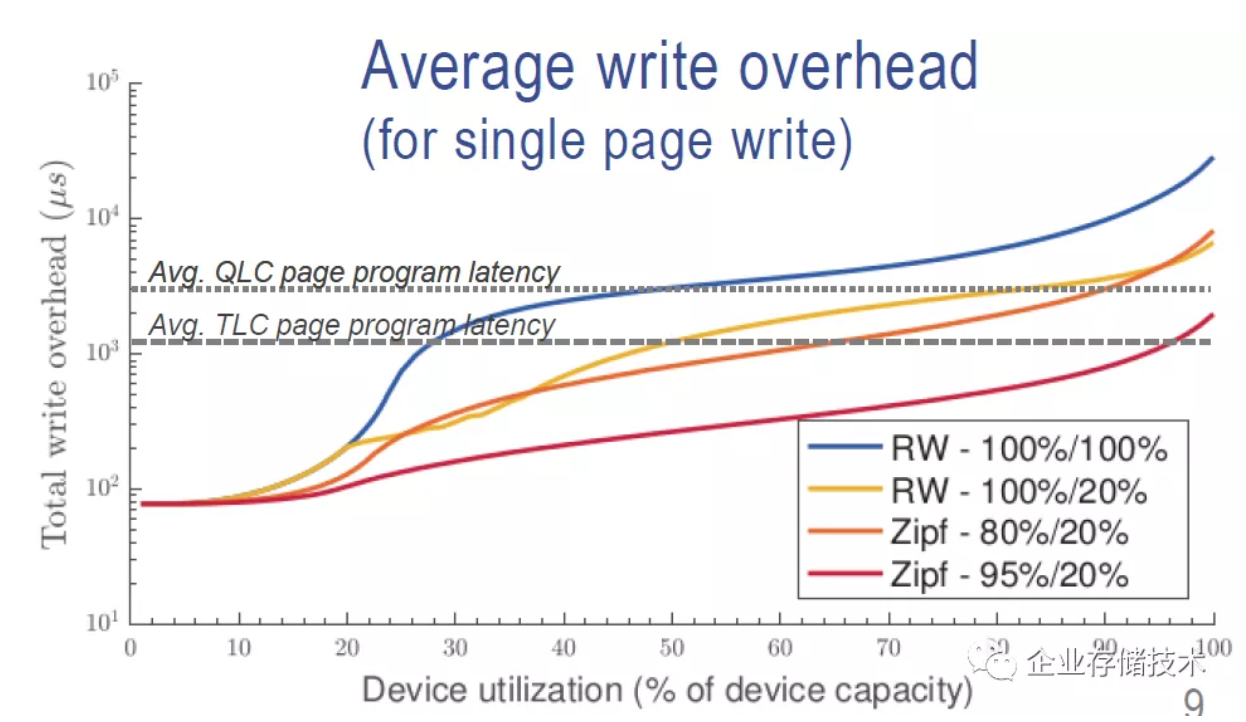

再看看平均写开销(针对单页面写)。由于SLC Cache的作用,在SSD容量比较空的情况下,写延时甚至比TLC页面编程时间低一个数量级,而到容量写满50%之后,这个延时有可能超过QLC本身。作为企业级SSD的FCM,其“SLC Cache”也不是完全没有副作用的。

最后再给大家看一下IBM FCM的控制器架构。蓝色实线代表主机写入数据的物理流向——先进入非易失Cache(MRAM),“热分离”后分别写入Destage Unit中的SLC块和QLC块。对于写入QLC的数据,“Read Heat Separation”还会根据数据冷热分为4个命令队列。

右边是已占用的SLC和QLC块池,根据需要触发GC和WL(磨损平衡)后,数据可以进入Data Placement Unit重新分配写入。

小结:在SSD还是系统层面Hybird(混合)?

对于配置SLC Cache的QLC SSD,在企业级SSD市场是否会流行起来我也说不准。个人认为从系统层面解决这个问题也不错,在存储系统中混用Optane + QLC SSD,比如像vSAN那样的缓存/分层架构已经很成熟了。

参考资料《Achieving Latency and Reliability Targets with QLC in Enterprise Controllers》

《Using Computational Storage to Handle Big Data》

_《QLC Everywhere! Even in Primary Storage!》

_

_链接:https://pan.baidu.com/s/1EvnT...

提取码:e2sx_

推荐阅读

注:本文只代表作者个人观点,与任何组织机构无关,如有错误和不足之处欢迎在留言中批评指正。 进一步交流技术可以加我的微信/QQ:490834312。

尊重知识,转载时请保留全文,并包括本行及如下二维码。感谢您的阅读和支持!《企业存储技术》微信公众号:HL_Storage,也欢迎关注企业存储技术极术专栏,定期更新。