作者注:在英特尔推出至强可扩展处理器(Skylake)及平台当天到一周之内,我先后发表了图说和架构解析的文章,又在2017年8月9日以此文对新至强产品线构成进行比较详细的介绍。

某冰冰曾经说过:我能承受多大的诋毁,就能承受多大的赞美。非黑即白的粉丝逻辑,在太多方面难以量化的娱乐圈深深扎根,让人不由得感慨,娱乐精神哪里去了?

纵然是看起来容易量化比较的IT技术和产品,对它们的评价也不至于非粉即黑,让我们努力找回一些娱乐精神罢。

从吐槽的角度,老早我曾经说过:很多时候,厂商宣传新产品的功能,(给人的感觉)更像是在“黑”之前的产品。

只举最近的例子:vSphere 6.5 U1 的新增功能中,有一项是“vCenter Server Foundation 支持 4 节点集群”,不经意间提醒了吃瓜群众——敢情以前vCenter Server Foundation只支持到3节点集群?!

这点儿小“瑕疵”,跟大英(特尔)比起来,实在是小巫见大巫:上个月轰动业界的至强可扩展处理器(Xeon Scalable Processor,XSP)发布,只一个产品名称的改变,就把前面至少四代至强都给黑了——难道,Xeon E3/E5/E7不是可扩展的吗?

可以说,还真不……能算是。

(进入正文,看不清的图都可点击放大哦)

可扩展的……是谁?

伴随Scalable Processor(可扩展处理器)一同提出的还有Scalable platform(可扩展平台),两者缩写都是SP,难免让人迷惑——可扩展的主角究竟是谁?

相比于首字母必须大写的Xeon,紧随其后的processor和platform都有小写的时候,个人感觉platform小写的时候更多——或者说,Scalable Processor写法更像一个专有名词。在Intel的官网上,还有Xeon Processor Scalable(XPS?Dell笑了)的写法。

另一个“书面”证据是:Skylake和Purley分别是处理器及其平台的代号,而刚推出的第一代至强可扩展处理器可以简称为Skylake-SP,所以SP代表可扩展处理器是没有什么疑问了。

从实际使用上来看,至强SP也确实比四代至强E5/E7更利于扩展。

没错,在讨论中排除掉了血缘关系其实与消费级的Core(酷睿)家族更近、命名规律也与E5/E7有所不同的E3家族。

在E5/E7的时代,可扩展性局限于各自家族内部,即:

- E7可以从双路扩展到四路和八路;

- E5可以从单路扩展到双路(2600)和四路(4600);

但是,E5和E7彼此不兼容。

注:E5-2400(1个QPI)和E5-1400面向嵌入式市场,采用不同的封装(LGA 1356)

处理器的扩展性显然会影响到平台(主板)的相容性,这个冲突在四路平台暴露出来:E5-4600和E7-4800/8800是不能互换主板的,这意味着服务器厂商要推出(至少两个)不同系列的四路服务器平台——譬如Dell的PowerEdge R830(E5-4600系列)和R930(E7-4800/8800)。当然,服务器厂商也可以选择只出(或侧重)其中一个,放弃另外一类市场。

虽然E5-4600系列比E7家族的产品少了1组QPI,CPU之间互连带宽和效率受到影响,而且E5 v4还被人为“阉割”掉2个内核,但在性价比上仍具有明显的优势。英特尔经常给人刻意回避E5-4600存在的感觉,可这种相对廉价的四路平台依然卖得不错,根源还是存在足量的用户需求。

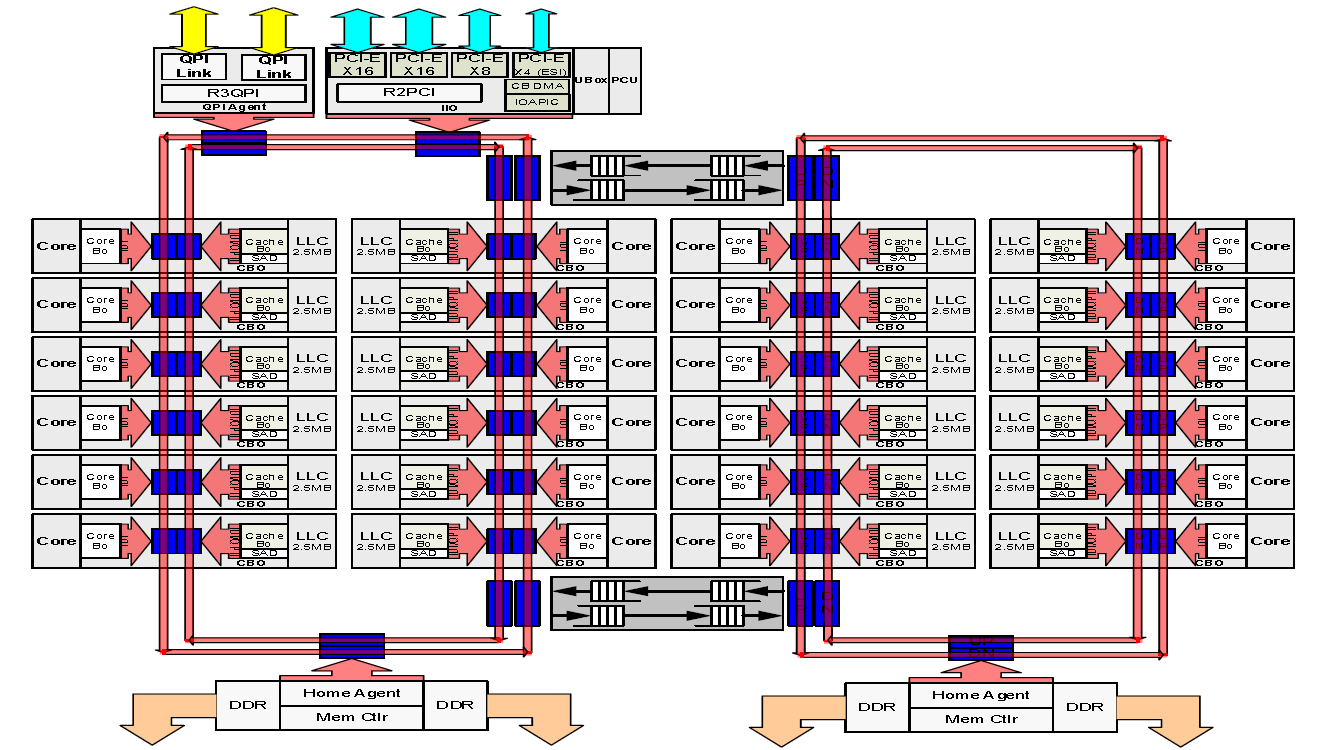

E5 v4(上)与E7 v4(下)的内核组织架构基本一致,都可以支持到24个内核,可见两个家族间的血缘关系。区别主要在于E7 v4在第二个环上多出1组QPI,而E5 v4最多只有22个内核

至强可扩展处理器终于消除了这个人为的壁垒,把选择权交还给服务器OEM或最终客户,最典型的例子当属Dell PowerEdge R940:用户可以自由选择3组UPI的至强Platinum 8100或Gold 6100系列(类似3组QPI的至强E7-8800/4800系列),或2组UPI的至强Gold 5100系列(类似2组QPI的至强E5-4600系列),Dell也不必再同时维护两个“异构”四路服务器平台(可以理解为R830与R930合并升级为R940)。

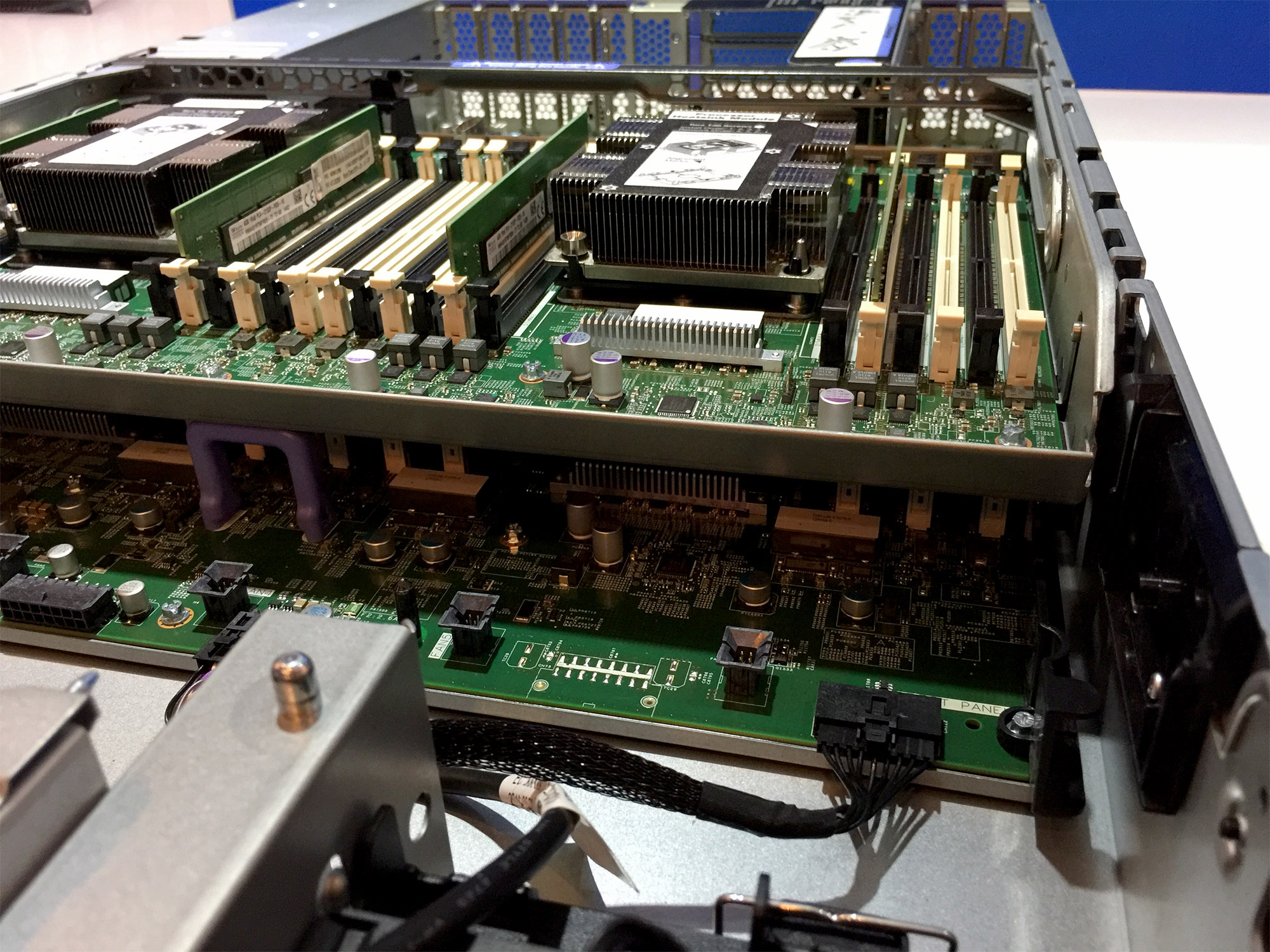

随着至强可扩展处理器的推出,多家服务器厂商设计了双层主板、每层双路的2U或3U机架式服务器,可以方便的在双路和四路之间免工具切换

甚至,在双路配置下,用户还可以选择具有3组UPI的型号(至强Platinum 8100或Gold 6100系列,类似从v3起消失的E7-2800系列),以获得更高的(CPU间)互连带宽。

(注:关于至强SP与E5 v4的对位升级关系,请参见公众号“小麦杂记”的《E5 v4到Xeon SP的升级路线解读》一文)

这就是《8张图速览新至强:Skylake架构、外貌与型号》一文中,“E7两路重出江湖,E5四路确认名分。”那句话的含义:至强E5和E7,两个分割已久的山头,终于打通了。

再进一步,单路主板也可以支持多达28个内核、56线程的顶级CPU至强Platinum 8180,如Supermicro的X11SP系列。而从至强E7 v3开始,连双路E7都不被鼓励了,更不会有厂商为了配满24核这种小众需求去推出单路E7主板啦。

小结:总体而言,可扩展处理器称得上名副其实,平台随之得以简化,也变得易于扩展了。更名的主要槽点,不在这里。

金属家族?画蛇添足!

由于E5和E7之间的“插座隔离”被打破,型号的命名规则随之更改也是情理中事,关键看怎么改。

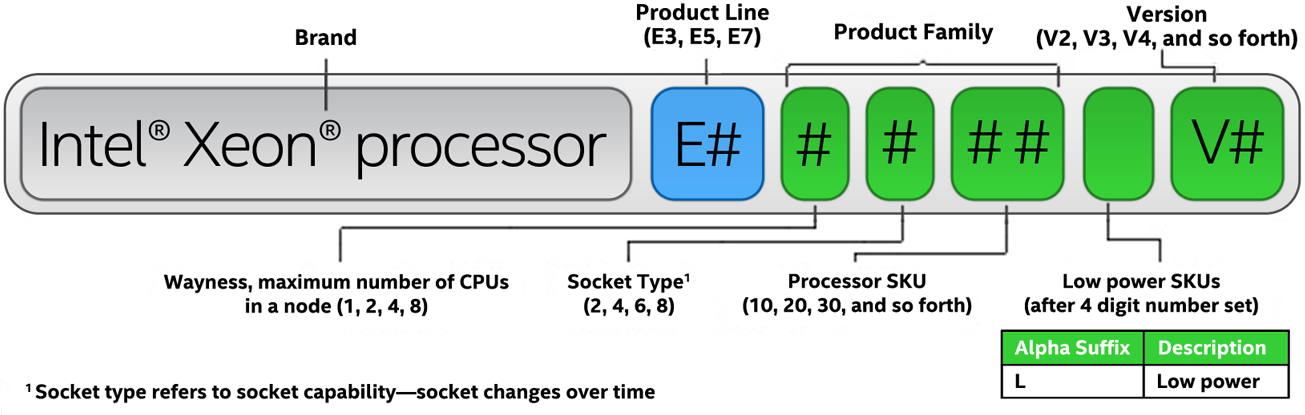

至强E3/E5/E7的型号命名规则

简单回顾一下至强E5/E7的型号格式:

Ea-bc## v*

a/b/c、## 和 都是数字,## 代表具体SKU, 为2~4,第一代后面不加 v……

b 代表处理器直接连接可以达到的最大互连规模,也就是能到几“路”(Socket),为2的0到3次方,即1/2/4/8共4个数字;

c 代表插座类型,从2/4/6/8中取值,可以视为对b的补充说明:8是一家(E7),都有3个QPI;6和4属于另一家(E5),46 和 26 都有2个QPI;24 和 14 的针脚数量和封装尺寸都与其他系列不同,面向嵌入式市场,v3之后终止。

a只有两个选项:5,或者7,除了分别代表主流和高端,还有比较明确而具体的含义——

- E7:3组QPI,四路和八路(及以上)市场;

- E5:2组QPI,双路和(廉价型)四路市场(不考虑定位特殊的24/16/14系列)。

没有E7或E5作为前缀,纯数字的型号也不会出现重合,但E7和E5直观的划分出两个不能互换使用的产品家族,并非多余。

既然至强可扩展处理器全家族都打通了,E5和E7原有的含义不复存在,如果要继续使用,必须更改其代表的含义,反而会引发更大的混乱。所以,命名规则必须更改;可惜,新的“金属+4位数字”组合,槽点满满。

重申一下E5/E7命名规则的精华:后缀标示“代”数(从无到v4),头2位数字简明描述主要特性,前缀(E5或E7)划分家族。

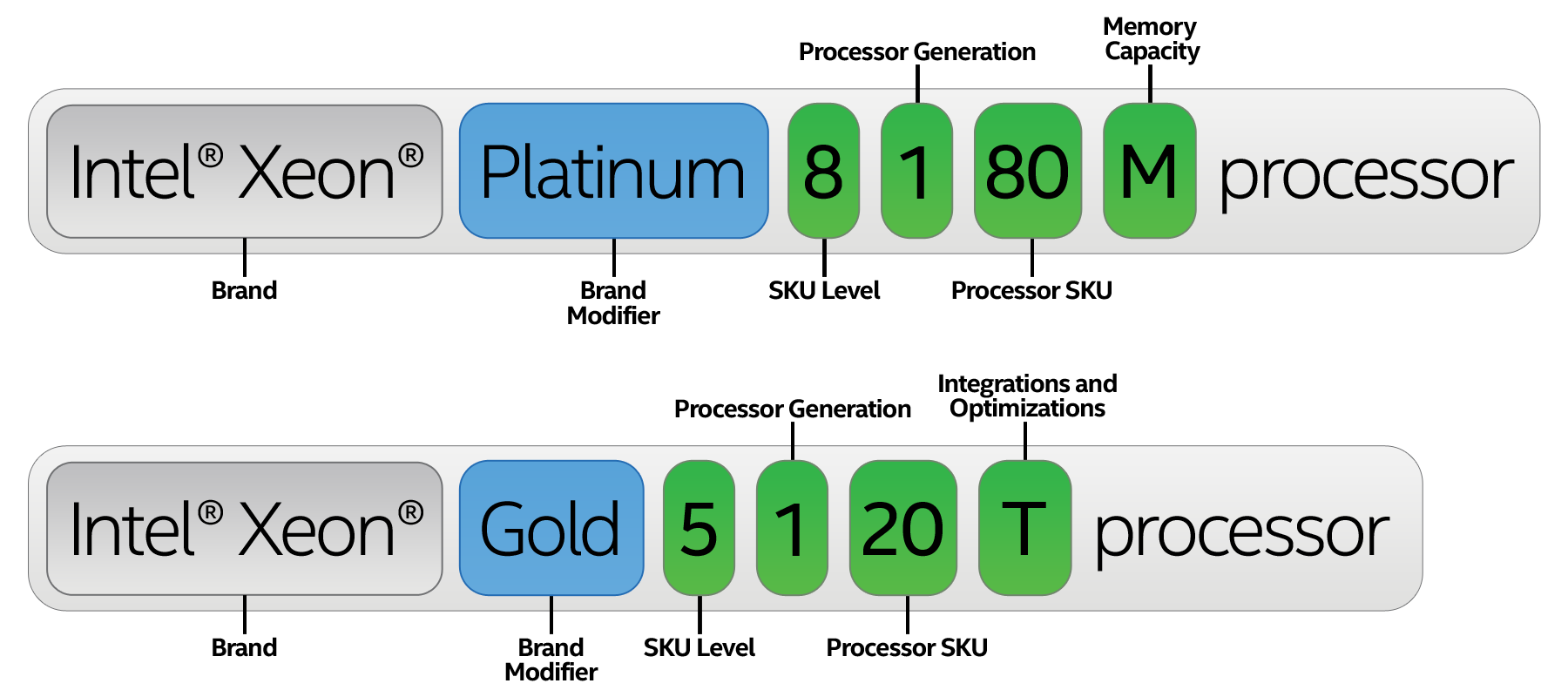

再看至强SP的命名规则,携带的有效信息就少得多了:

至强可扩展处理器的型号命名规则,注意两位数的“Processor SKU”跨铂金/金牌/银牌/铜牌及“SKU Level”递减,字母后缀的选项也有较大丰富

第2位数字标示“代”数,Skylake-SP是第一代,所以这批产品型号中的第2位数字统一为“1”,也就是说在同一代产品中起不到区分作用。剩下只有第1位数字,要对应的关联信息太多(支持几路、多少UPI、多少内核、内存频率),除非你比较熟悉整个家族的产品特性,它只能体现从高到低的定位,甚至还不如之前的(E)7或5来得简明有效。

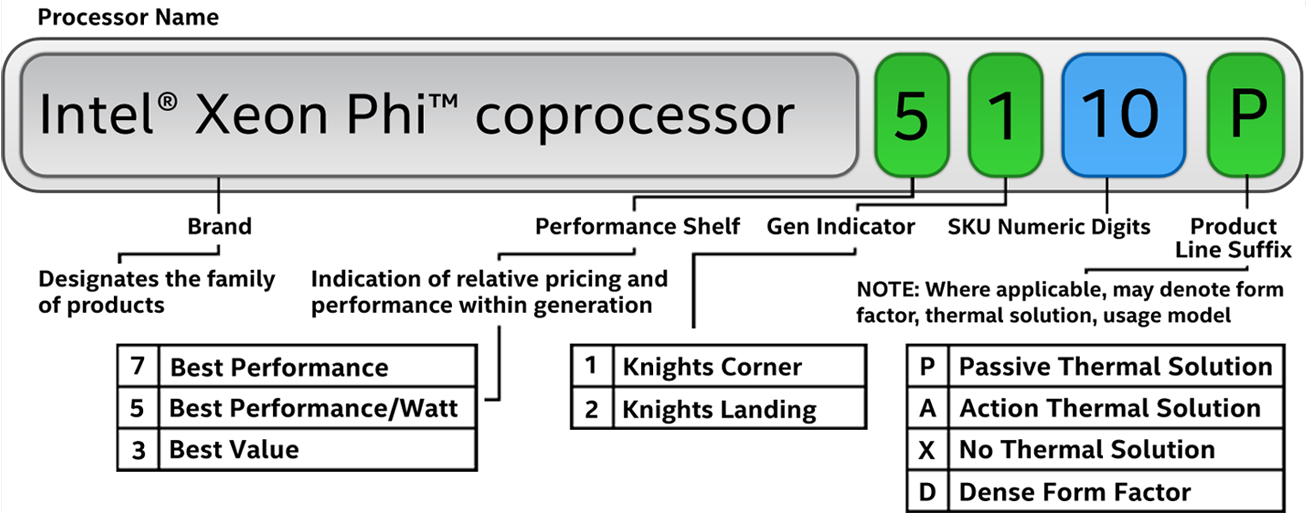

7开头的处理器到哪儿去了?早已被率先采用LGA 3647封装的第二代Xeon Phi处理器(Knights Landing,KNL)所占,所以是“72”(前一代的Knights Corner先占了“71”)在前

更糟的是,作为前缀的金属名称也几乎不能提供更多信息:Platinum对应8,Silver对应4,Bronze对应3,只有Gold略显例外——告诉我们6和5是一个大家族,但至少从表面看起来,它俩之间的共性,未必比5和4之间更多。

不知大英是否受了80 PLUS电源(Power Supplies)认证体系的启发?或许,随着至强可扩展处理器TDP的进一步上升,未来会出现类似 Titanium 92xx 这样的产品吧……

至于铂金、金、银、铜背后体现的品味,见仁见智,这里就不点评了——反正型号数字前面有没有它们,也没什么区别——基本属于冗余信息,颇有画蛇添足之感。在有些主板的说明书里,干脆就直接在Xeon后面跟81xx/61xx/51xx/41xx/31xx了,又没损失什么有效信息,关键是省地儿。

当然,字母后缀,还是很有用的,下面会有重点讨论。

你要买的这些内核,是怎么来的?

说完了CPU之间的扩展方式,来看看至强SP的内核如何组织——具体原理在上一篇《新至强Mesh架构解析》中已经有详细阐述,这里主要说一说具体产品家族的内核数量问题。

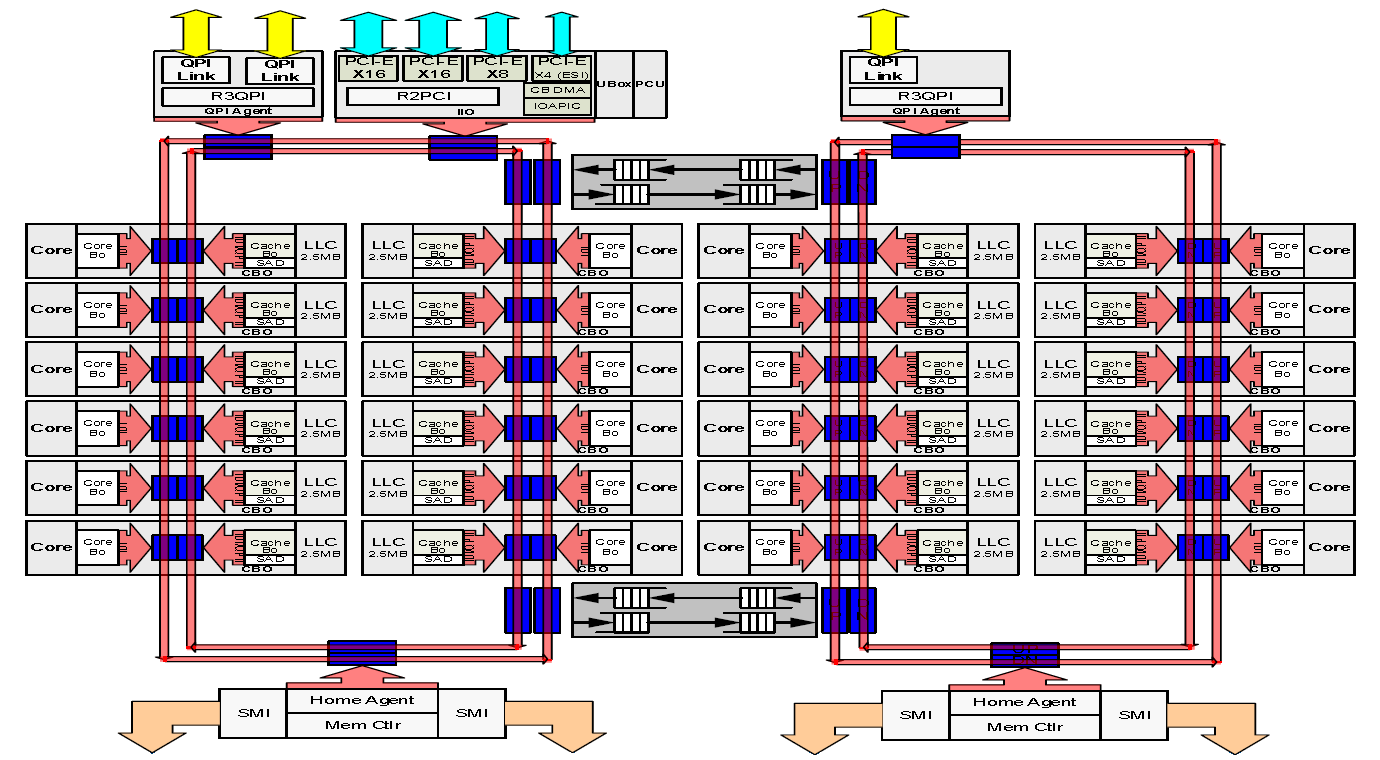

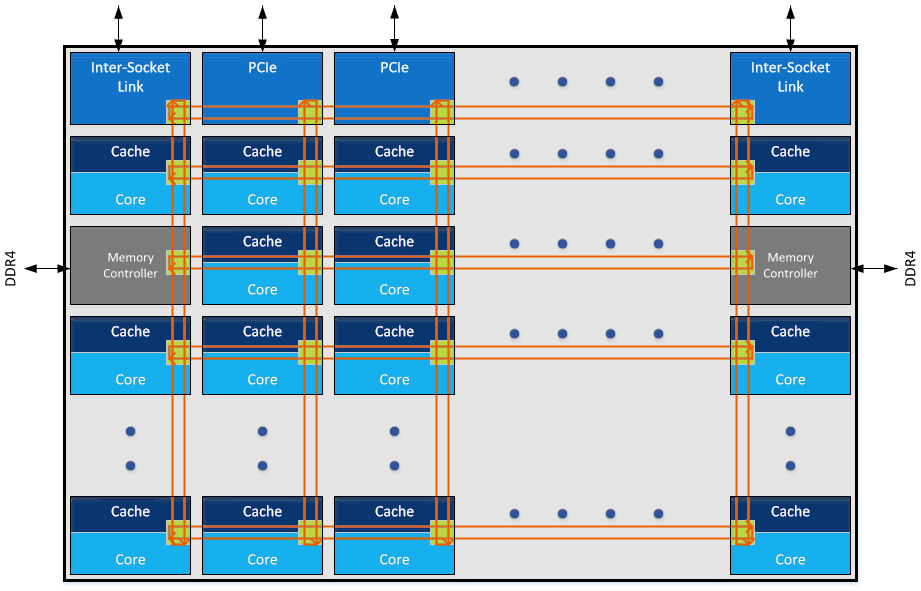

6月15日,AMD EPYC发布前夕,Intel Skylake-SP CPU架构师Akhilesh Kumar发表了一篇介绍“全新网格架构”(Mesh)的博客。由于至强SP还没有正式发布,文中只放了一个模糊了Mesh矩阵规模的“网格结构概念示意图”——当然,现在已经换成基本符合实际情况的6×6矩阵图了。

如果较真些,把每个圆点也当成一个节点,那这就是个8×7的2D-Mesh

内核数量越多,规模的增长率就越不易保持。以至强E5 v4的架构为例,用两对双向环形总线连接最多24个内核,达到初代E5(双向环形总线连接最多8个内核)的三倍。回过头来看至强SP,现在是6×6矩阵(36个节点)提供最多28个内核:

- 如果扩展到8×8矩阵(64个节点),提供的内核数量恐怕增加不了一倍(如果I/O部分仍然占去一整排);

- 进一步扩展到10×10矩阵(100个节点),提供的内核数量也不过略超三倍而已……

初代至强可扩展处理器(Skylake-SP)采用6×6的Mesh,I/O占去一整排共6个节点,内存控制器又用掉2个节点,所以最多只能提供28个内核(= 36 - 6 - 2)

怎么加内核是Intel的事儿,咱们现在要关心的是,内核数量低于28个的那些型号,是怎么来的。

在E5 v4这一代,根据内核数量需求的不同,Intel微调了环形总线的布局,分出了高内核数(High Core Count,HCC)、中等内核数(Medium CC,MCC)和低内核数(Low CC,LCC)三类,支持的最多内核数量分别为24 (22)个、15个和10个。

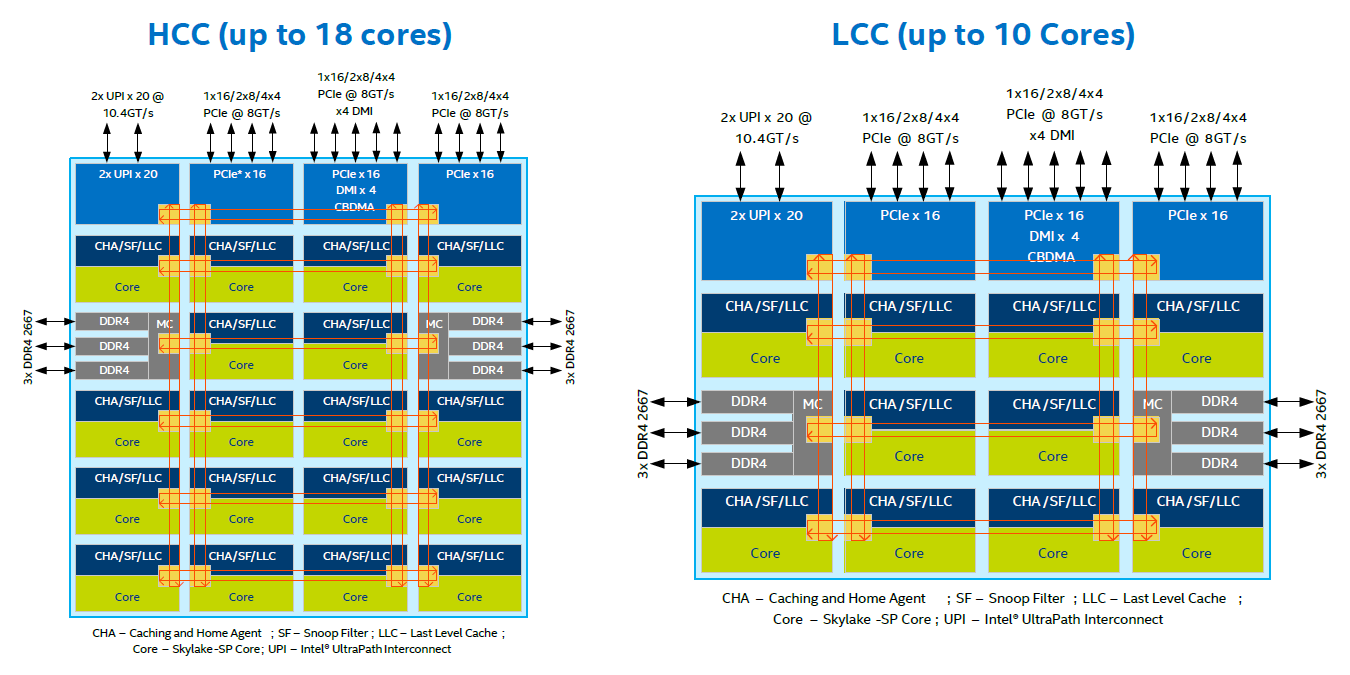

由于至强SP的内核数量又有所增加,Intel将原来的HCC升格为XCC(eXtreme CC,最多核or极多核),可支持到28个内核;MCC递补为HCC,可支持到18个内核;LCC依然最low,可支持到10个内核——与E5 v4保持一致。

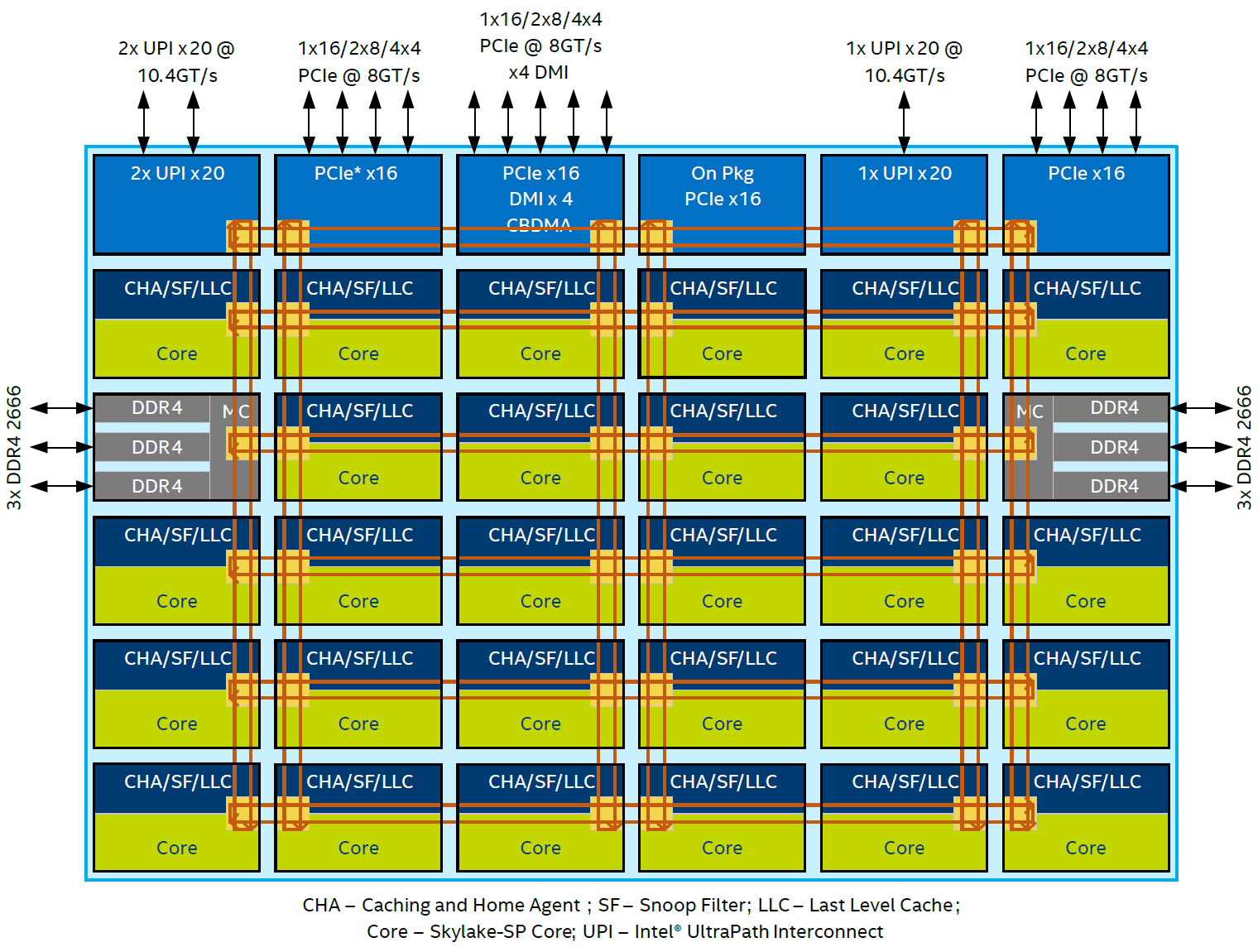

Skylake-SP的HCC和LCC都采取将XCC的6×6矩阵削掉2列的做法,这意味着I/O节点从6个减至4个。区别在于:

- HCC还是6行(4×6),所以能支持18个内核(= 24 - 4 - 2);

- LCC行数也减为4(4×4),所以只能支持10个内核(= 16 - 4 - 2)。

I/O部分包括CPU之间互连的UPI(Ultra Path Interconnect),和用于连接外设的PCIe,牺牲谁好呢?E5-2600/4600每处理器支持40个PCIe 3.0,E7从v2开始每处理器支持32个PCIe 3.0,两个家族之间有差异,但家族内部的所有产品PCIe信道数量保持一致。

在大数据和AI的时代,I/O能力越来越重要,而且越是内核数量少的处理器,越有可能靠PCIe过活(存储、网络、GPU/FPGA等应用)。如前所述,至强SP不再分E7和E5,每处理器都支持48个PCIe 3.0,所以只能砍掉1组UPI了(On Pkg的PCIe x16下节再说)。

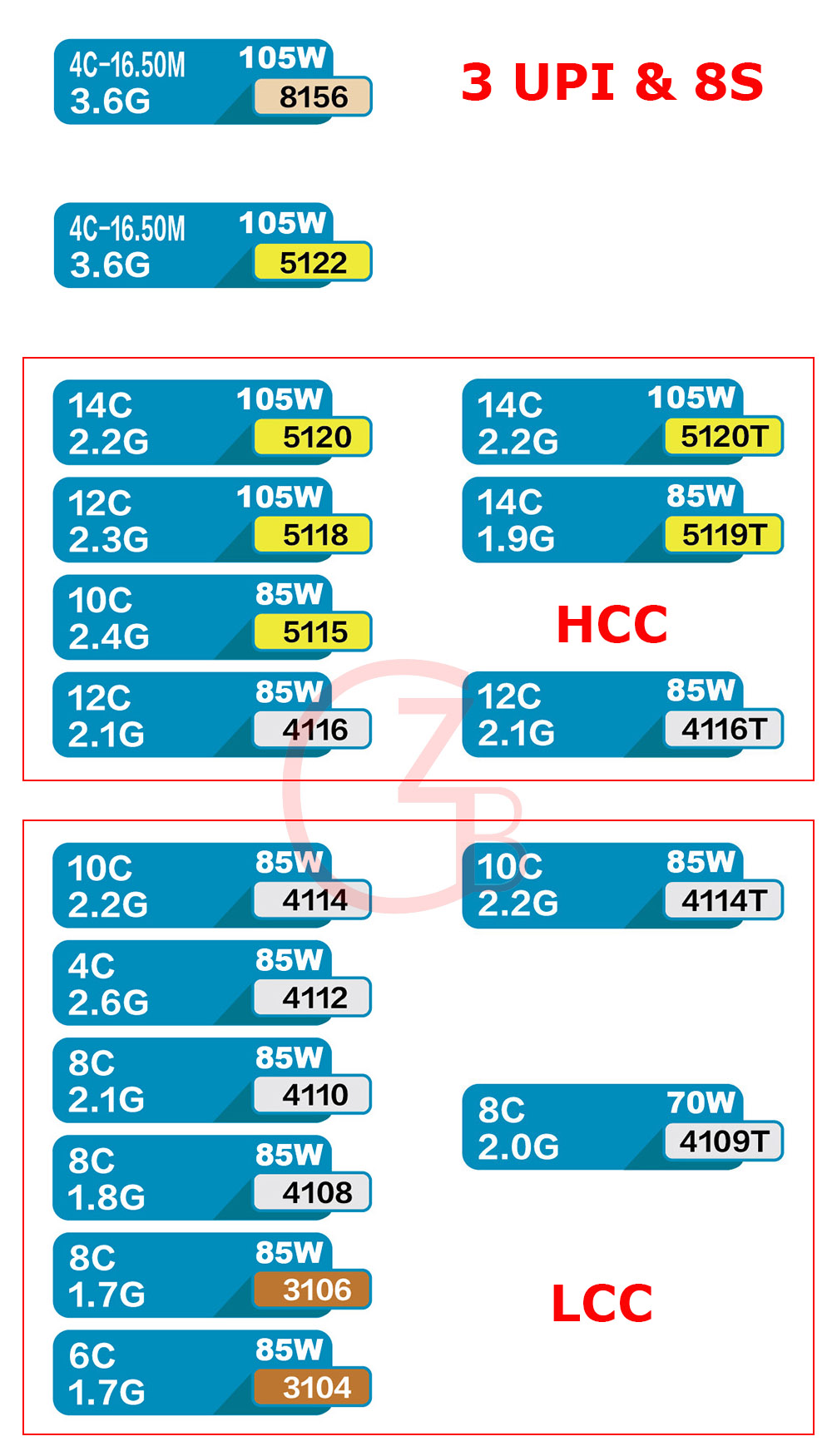

这样一来,有3组UPI的Xeon Platinum 81xx和Gold 61xx都来自XCC无疑了?是的,铂金和金牌家族全部来自XCC,包括后缀为 F 或 P 的型号,总体数量明显占优。

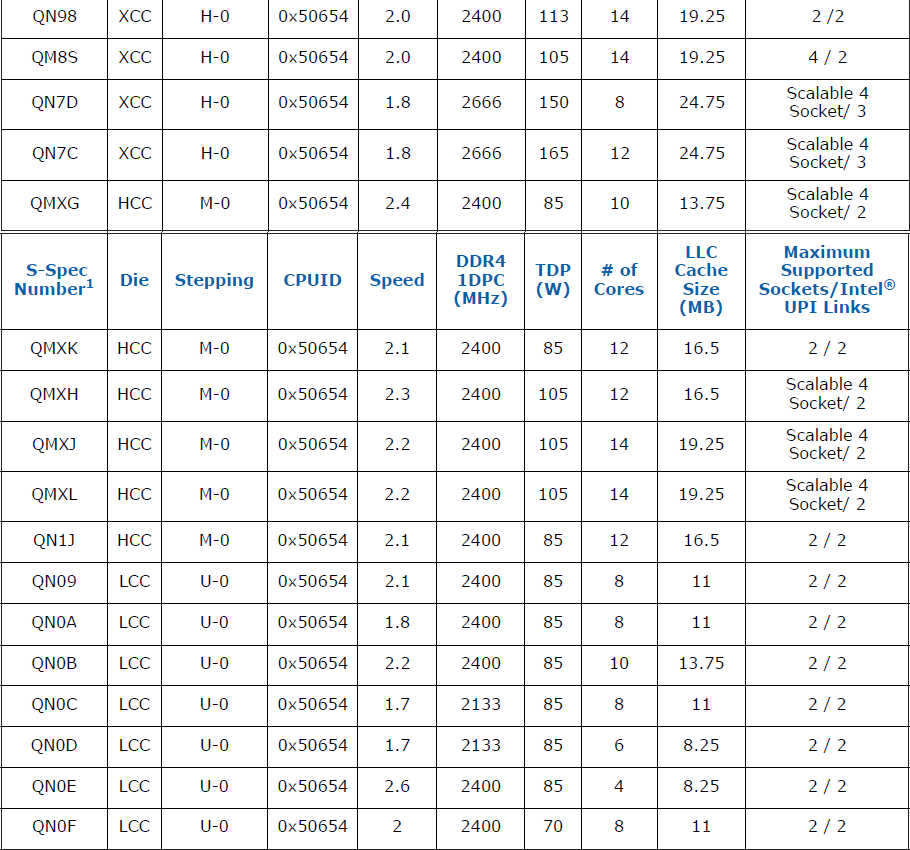

目前已知的HCC和LCC型号全表,来自XCC的S-Spec编号占绝大多数,比HCC+LCC的4倍还多。另外,3组UPI可以被限制在四路,2组UPI也有只能到双路的型号,这种做法与至强E7/E5时代没什么两样

仅有2组UPI的Xeon Gold 51xx都来自HCC,Xeon Silver 41xx和Bronze 31xx都来自LCC?也不全对。

- 首先,LCC最多只到10核,但Xeon Silver 4116(T)多达12核,属于HCC,其他Silver 41xx产品和Bronze 31xx家族(仅限已公开版本)均属于LCC;

- 其次,HCC区间里的产品则还没达到理论最高的18核,包括了两款“升级的”Silver(4116及其T版),以及除Gold 5122之外的所有公开版本Xeon Gold 51xx……

Xeon Gold 51xx/Silver 41xx/Bronze 31xx与HCC/LCC的对应关系

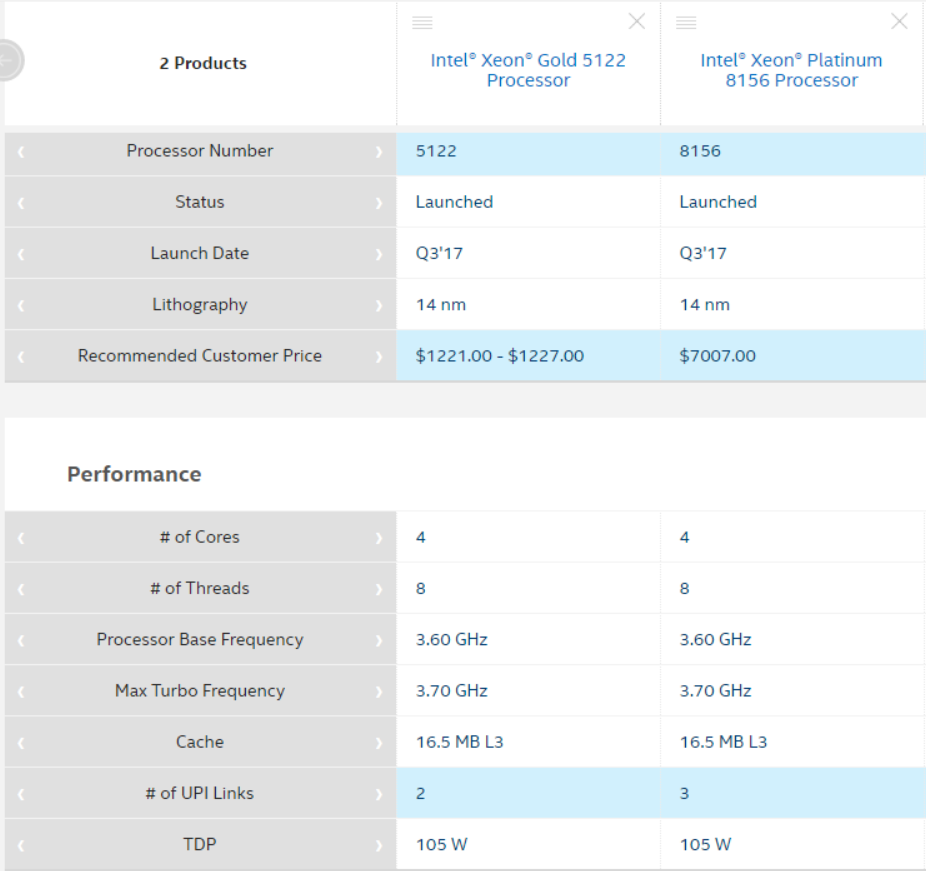

至于Xeon Gold 5122,其内核数量、TDP指标、LLC容量乃至频率特性都与Xeon Platinum 8156一致,看起来只是UPI少了1组,却皆属于XCC——虽说这内核数量,加上2个内存控制器,刚好凑满一行,但LLC容量可是12个内核的水平(16.50MiB),so,你懂的……另外,二者的频率也是初代至强SP中最高的。

如此犬牙交错的配置,岂是含义重合的“铂金+8”、“金牌+6/5”、“银牌+4”、“铜牌+3”能够梳理好的?

能配四路和能配八路,差价咋那么大nia?

那么,位列Xeon Platinum 81xx和Gold 61xx,却只提供2组UPI的型号,又是为何?下面马上揭开这个最大的谜题!

相爱相杀的 FPGA 与 Fabric

比起至强E5/E7时代,至强SP型号中的后缀可谓极大丰富。譬如,“M”代表单CPU可支持两倍的内存容量(1.5TiB ÷ 768GiB),即能够使用单条128GiB的内存(此等LR-DIMM很贵的说);“T”的官方解释是“High Tcase/exTended Reliability”(高 Tcase/扩展可靠性),但我更喜欢小麦兄的“Telecom”(电信),没到十足严谨,但足够反映其主要用途,最关键是——易于理解和记忆!况且,命名完成之后,如何解释,往往就由不得命名者啦……

对“M”和“T”的解读,强烈建议大家移步小麦杂记之《关于Xeon SP的其他几个问题》一文,但关于“F”的阐述,我有不同看法。或者说,我认为自己找到了更好的解释。

Intel Xeon Phi x200 处理器率先采用 LGA3647 插槽,可见 F 版凸出的“鸭嘴”结构及主板上留给出线的通道

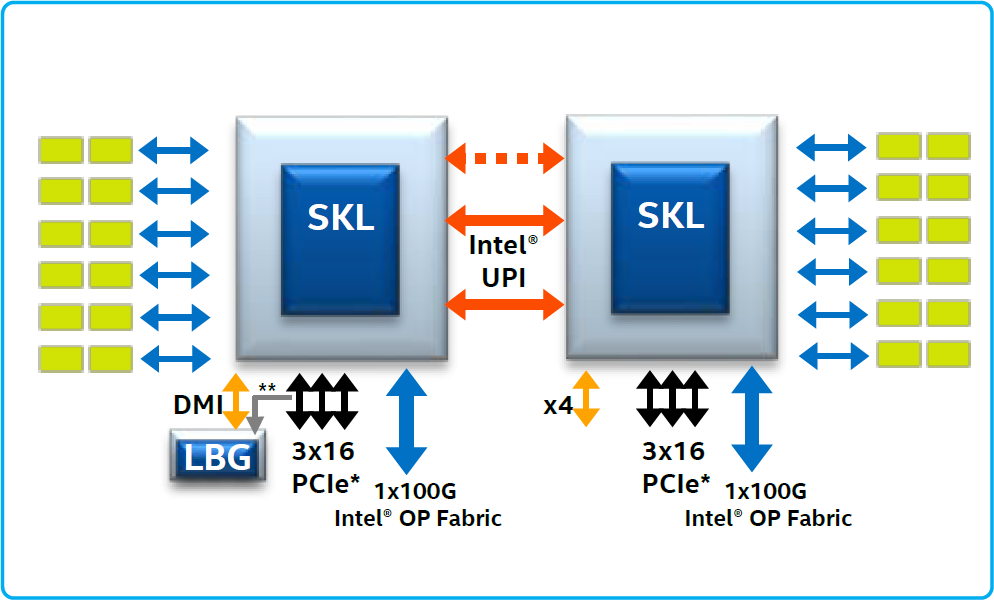

“F”代表Fabric,即集成了Intel Omni-Path Architecture (OPA) Fabric的型号。我们知道,预计在半年后,Intel将推出片上封装了Altera FPGA的同代至强SP产品,但是“F”早在第二代至强融核(Xeon Phi)处理器——也即Knights Landing(Intel AVX-512就是它先搞的)——推出时便已划拨给了集成OPA Fabric的型号(Intel Xeon Phi Processor 72x0F),留给FPGA版本的就只有“P”啦。

以太网卡较少有PCIe 3.0 x16规格,但100GbE产品必须用,因为PCIe 3.0 x8的带宽跑不起来

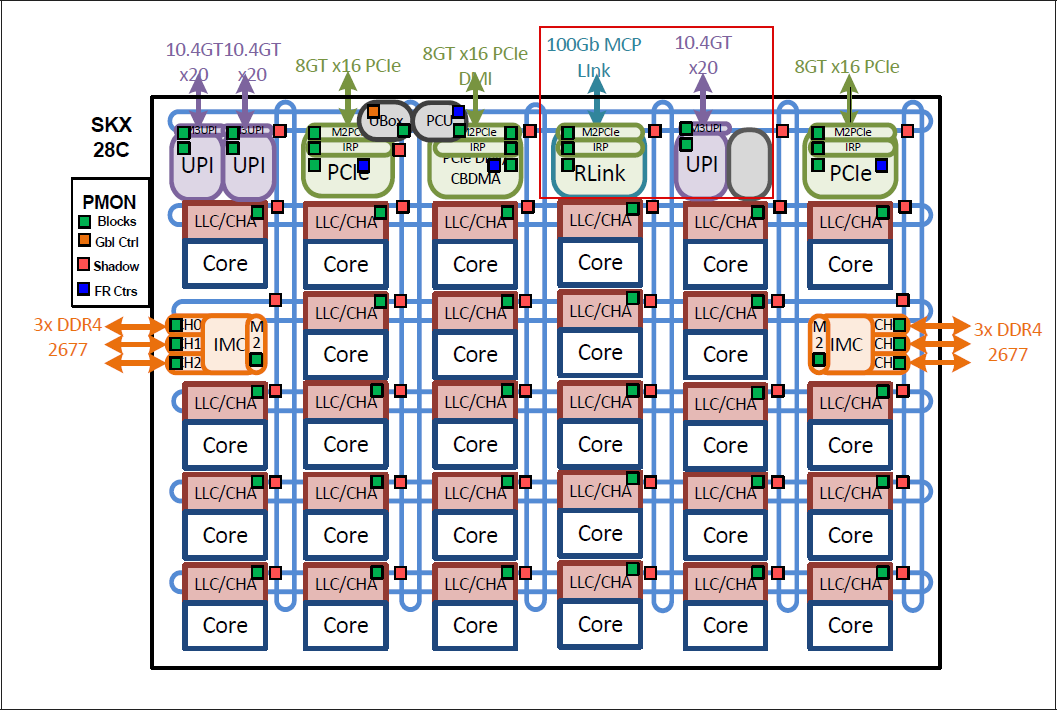

目前Intel Omni-Path Host Fabric Interface (OP HFI)的带宽是100Gbps,意味着集成OPA的CPU必须为其准备一个PCIe 3.0 x16的连接。我们知道,XCC架构的6×6矩阵,上面一行6个I/O节点中,专门留有1个用于片上(On Package)连接的PCIe 3.0 x16,正好用于100Gb的OPA Fabric,从而不会减少CPU能支持的PCIe 3.0信道数量(48个)。

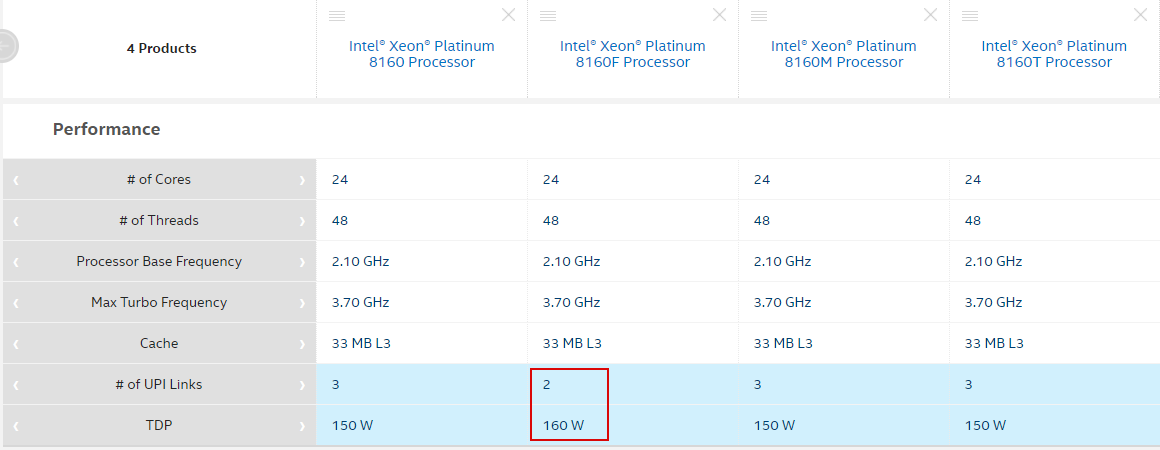

“F”版本TDP上升,UPI减少

所以,不难理解为什么“F”版本都出自Xeon Platinum 81xx和Gold 61xx了。但是,与被迫放弃On Pkg PCIe 3.0 x16及相邻1组UPI的HCC/LCC架构不同,“F”版本只是占用了On Pkg的PCIe 3.0 x16而已,为何连那1组UPI也不见了?

没有获得官方答案,我倾向于认为,Skylake的6×6 Mesh架构,最上面一排的6个I/O节点,右半边的3个有着不同的关联。

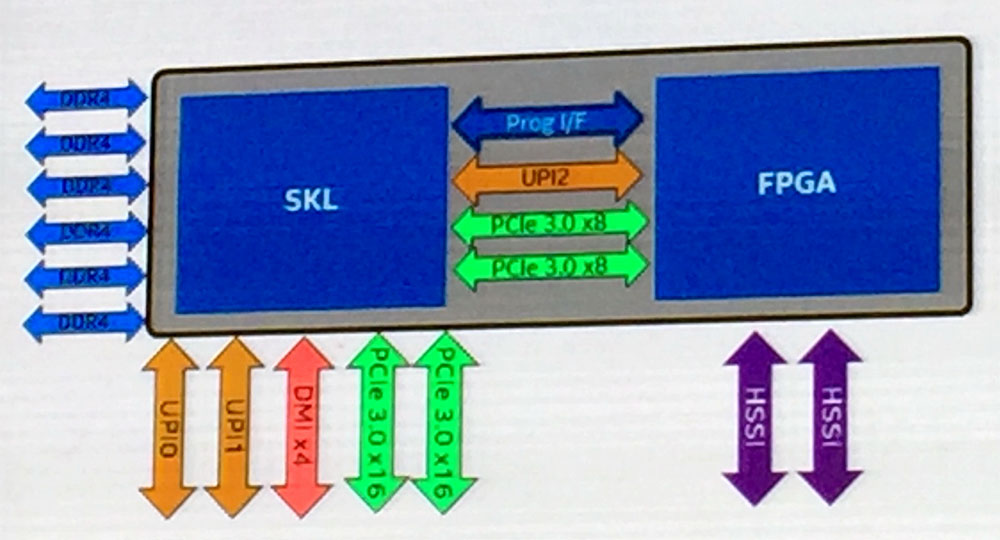

Skylake的Mesh架构,最上面一排的6个I/O节点,右半边的3个有着不同的关联:①处的100Gb MCP Link其实就是 On Pkg 的PCIe 3.0 x16,用于Fabric(“F”)版本;②处的1组UPI和③处的PCIe x16可以用于片上连接FPGA,即“P”版本

MCP即多芯片封装(Multi-Chip Package),或者说On Package(片上封装)也好,有集成Fabric(“F”版本)和集成FPGA(“P”版本)两种情况,正好把右半边的3个I/O节点——单独的1组UPI(而不是2个在一起的UPI)及其两侧的各1组PCIe x16给用上。

在具体的分配上,集成Fabric会用上靠中间的On Pkg PCIe x16;集成FPGA则会用上落单的第3组UPI(编号为UPI2)和靠边的另1组PCIe 3.0 x16——在不考虑On Pkg PCIe x16的情况下,也是落单的第3组。

注意CPU下方少了1组PCIe 3.0 x16,化身为2个PCIe 3.0 x8,与1组UPI(UPI2,起点为0)用于CPU与FPGA之间的互连

如图所示,这1组UPI用于CPU与FPGA的片上连接——如同CPU之间的UPI连接,作为低延迟一致性互连,区别在于速率只到9.6GT/s(而非Platinum和Gold可以达到的10.4GT/s);配合其使用的PCIe 3.0 x16,是为了让该FPGA可以对外提供HSSI(High Speed Serial Interface,高速串行接口)以连接其他设备。2个HSSI可以是PCIe 3.0 x8,也可以是直接的以太网连接,如2×40GbE……总的说来,集成FPGA的版本,对外的(等效)PCIe连接数量,并没有减少。

从结果来看,第3组UPI与On Pkg PCIe 3.0 x16这对“邻居”有种奇妙的耦合关系——在MCP的场景下,只能使用其中一个:FPGA版本,后者歇菜;Fabric版本,前者消失。

无论具体原因为何,铂金81xx和金牌61xx出身的Fabric和FPGA版本,对外都只有2个UPI。按理说这样还是可以支持四路配置的,但“F”和“P”版本均只支持双路配置:Fabric版本主要用于高性能计算(HPC),很少需要双路以上的胖节点;FPGA版本也基本不需要放在四路或八路的系统中。简而言之,从应用需求的角度,双路就够啦。

“P”版本(FPGA)与“F”版本的另一个相似之处就是,配合的CPU也是最高28核、165W的TDP,即从Platinum 8176往下。不同之处在于,TDP的增加可就不是8W到10W这个级别了,配套的FPGA以Altera中端定位的Arria 10 GX 1150计算,TDP可达70W,意即总的TDP会高达235W——Titanium 9xxx 在前方等着我们嘛?