第一作者 | Yangyang Xia

共同作者 | Hong Yin\, Miao Liu\, Qianyi Zhang

上海楷登电子科技有限公司

201204 上海市浦东新区芳甸路1155号5楼

目的

伴随着超大规模集成电路进入纳米级别,电压降(IR-Drop)成为制约高性能和高可靠性电路的重要因素。因为金属互连线的寄生电阻电容的存在和电源供应不平均,芯片内将会存在电压降,该压降会引起电路时序的延缓,从而导致延时违例和信号完整性问题。因此,在电路设计中需要进行电压降分析,并且修复电压降违例。

通过一些客户的反馈,在先进工艺下,尤其是7nm/12nm的良率分析,因为电压降违例导致的良率问题非常严重。Cadence作为业内唯一一家有着业内领先的实现工具(Innovus),时序收敛验收工具(Tempus)和功耗收敛验收工具(Voltus)的EDA供应商,急客户所急,推出本套成熟的基于时序的电压降ECO流程。

电压降分析主要用来验证整颗芯片的供电是否正常。一般情况下,电压降分析有两种方式,静态电压降分析和动态电压降分析。静态电压降分析基于功耗分析把器件模拟成一个恒流源并提取电源地网络的电阻进行分析。静态电压降分析主要跟电源网络的结构以及电源线的连接相关。对于动态电压降,主要是由于电路正常工作时电流波动或者当大量晶体管和组合逻辑电路同时跳变时,芯片会产生很大的瞬时电流,这个电流会引发大的电压降。

为了提升芯片的性能和可靠性,设计工程师很有必要在设计过程中进行电压降的分析。本手册将会提供一种基于时序的电压降ECO的流程,用以辅助设计工程师进行电压降违例的分析与修复,并且最大限度保证setup时序不受影响,和引入最小限度的DRC修复。

应用人员

该手册为数字电路设计工程师尤其是先进工艺数字工程师必备,辅助设计工程师在Innovus/Tempus/Voltus中进行电压降的分析与违例修复。

综述

该手册介绍了一种基于静态电压降分析的电压降ECO的流程,主要在postroute阶段使用Tempus进行ECO。电压降分析和ECO的引擎已经集成到Tempus当中。设计工程师可以通过该流程获得符合电路设计标准的电压降分析和违例修复,并且不增加芯片的时序违例。相应的Innovus和Tempus的命令也包括在该手册当中。

本流程用到的工具包含有Innovus, Tempus 和 Voltus。

手册主要使用Legacy格式的命令。

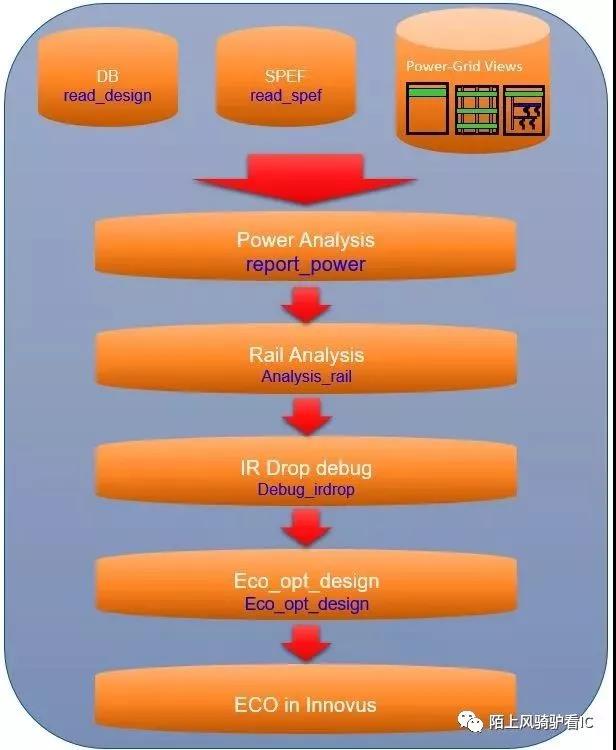

基于时序的电压降分析流程

基于时序的电压降分析流程主要是使用了Tempus中集成的Voltus功耗分析和电压降分析引擎。静态电压降主要是基于平均功耗进行分析的。因此,在进行静态电压降分析之前需要完成平均功耗分析。下面的图主要介绍了该静态电压降分析和违例ECO流程。

下面的步骤详细描述了基于时序的电压降ECO的流程:

- 导入设计:将Innovus的postroute DB直接导入Tempus。

- 导入SPEF:将SPEF文件读入Tempus。

- 产生电源网格视图(PGV,power grid view ):PGV的产生需要包括标准单元,电源开关器件,Macro/IP,filler和decap单元等。PGV是器件或者电路模块的电学和物理上一种对应表达方式,主要是根据电网络分布,提取电源网格的电学参数,包括电源网络分析的RC,电流,电容负载和物理位置等。

- 功耗分析:功耗分析主要是为静态电压降分析提供相应的电流数据。

- 电压降分析:电压降分析主要基于是PGV和功耗分析进行电压降的分析。

- 电压降debug:电压降debug用来发现芯片中存在的电压降违例。

- ECO-opt-design:电压降debug用来发现电压降违例的实例。ECO-opt-design主要是对这些电压降违例的实例进行修复。该修复过程会考虑到时序,最小限度的影响设计的时序。

- Innovus ECO:电压降违例修复结束后,Tempus会产生命名为eco\_innovus.tcl 的tcl脚本。设计工程师需要在Innovus中执行该tcl脚本,工具会在tcl脚本的引导下对相应的违例器件进行替换。替换结束后,需要进行ECO绕线,用来修复在实例替换过程触及的绕线。

1. 开启Tempus

\# 以timing signoff solution ECO的模式开启Tempus

tempus -tso

\# 开启tpsECOFeatureIRDropFix功能用来修复电压降违例

setBetaFeature tpsECOFeatureIRDropFix 1

2. 导入设计文件

\# 直接导入Innovus postroute DB 进入Tempus

read\_design -physical\_data xxx.enc.dat xxx

3. 导入SPEF文件

\# 导入SPEF 文件进入Tempus

read\_spef -rc\_corner xxx xxx.spef

4. 产生PGV

PGV是器件或者电路模块的电学和物理上一种对应的表达方式,根据电源网络分布提取电源网格的电学参数,包含了电压降分析和功耗分析所需要的信息。

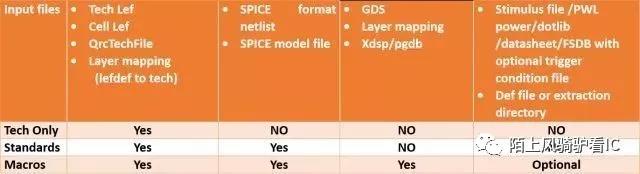

PGV包括三种形式:Techonly,IR,EM。Techonly仅用于早期电压降分析,IR和EM可用于整个设计阶段和签核。在电压降分析中,要对标准单元和Macro/IP/IO进行PGV的建模,具体所需输入文件如下面的表格所示。

以Tech only类型的抽取作为实例来描述PGV的产生。

\# 在产生PGV之前,设计工程师需要定义产生view的模式。首先需要定义产生cell的类型,包括Tech only\, Standards cells\, 和Macros and I/Os,然后定义芯片的供电电源端和接地端。同时,设计工程师需要列出设计中用到的decap器件和filler器件。如果设计中存在电源开关器件,设计工程师还需要定义电源开关器件的相对应参数,例如电源开关器件的名称,供电的电源端(supply),可开启关断的电源端(switched)以ohms为单位的开启电阻(Ron),以毫安为单位的饱和电流(Idst)和泄漏电流(Ileak)。

set\_pg\_libaray\_mode -celltype techonly

-power\_pins {VDD voltage}

-groud\_pins {VSS}

-decap\_cells *CAP*

-filler\_cells FILL*

-powergate\_parameters

{{ cell supply switched RonIdstIleak}}

-extraction\_tech\_file ***/QrcTechFile

\# 设定好相应抽取PGV的模式之后,设计工程师可以通过下面的命令产生PGV。工具将会生成dir.PGlib\_techonly.cl 的文件夹。

generate\_pg\_library -output ./ -libray\_prefix dir.PGlib

注意: PGV只需要在第一次跑这个流程的时候产生一次。如果设计使用的器件单元类型没有发生改变,工程师在之后的流程中可以直接使用第一次产生的PGV。

如果设计工程师需要产生其他类型的PGV,例如IR/EM ,那么就需要准备更多的输入文件。下面是Standards cells的产生IR/EM PGV的命令。

set\_pg\_libaray\_mode -celltype stdcells

-power\_pins {VDD voltage}

-groud\_pins {VSS}

-decap\_cells *CAP*

-filler\_cells FILL*

-powergate\_parameters

{{ cell supply switched Ron Idst Ileak}}

-extraction\_tech\_file ***/QrcTechFile

-spice\_models ***

-spice\_corners **

-spice\_subckts ***

-current\_distribution propagation

5. 功耗分析

\# 在进行功耗分析之前,设计工程师首先需要定义功耗分析数据的输出路径和文件夹,然后设定相应的功耗分析模式。

- write\_static\_currents需要被设置成true用来产生 绕线的电流数据。

- create\_binary\_db设置成true,定义binary\_db\_name ,用来保存二进制DB。

- 设定分析方式为静态用来执行静态的功耗分析。

- ignore\_control\_signals 设置成true。

- honor\_nehative\_energy设置成 true用来保存.lib中内部功耗表格中的negative internal energy numbers.

set\_power\_output\_dir staticPowerResults

set\_power\_analysis\_mode -method static

-write\_static\_currents true

-binary\_db\_name dynPower.db

-create\_binary\_db true

-ignore\_control\_signals true

-honor\_negative\_energy true

-analysis\_view ***

\# 设计工程师需要定义电路的switching activity ,如果有时钟门控,还需设置门控比例。 如果设计工程师有信号网络的翻转信息(TCF,toggle count format ) 文件\, 可以直接读入TCF。

set\_default\_switching\_activity -input\_activity 0.2

-seq\_activity 0.1

-clock\_gates\_output\_ratio 0.5

read\_activity\_file -format tcf ***.tcf

定义功耗文件的格式.

report\_power -rail\_analysis\_format VS

-outfile static.rpts

在功耗分析之后,工具将会产生很多.ptiavg文件,例如dybPower.db static\_VDD.ptiavg 。这些 static\_***\_.ptiavg文件将会被用来进行电压降的分析。

6. Rail分析

6.1 设置rail分析的模式

\# 设计工程师需要定义rail 分析的模式

- 定义rail分析的方式。该手册使用静态分析。

- 定义分析的准确度模式 (xd或者hd)。

- 导入PGV信息文件 ***.cl。

- 设置enable\_rlrp\_analysis为false加快电压降分析,减少内存使用。

- 定义分析的view和温度。

set\_rail\_analysis\_mode -method static

-accuracy xd

-power\_grid\_library {***.cl}

-enable\_rlrp\_analysis false

-verbosity true

-analysis\_view ***

-temperature *

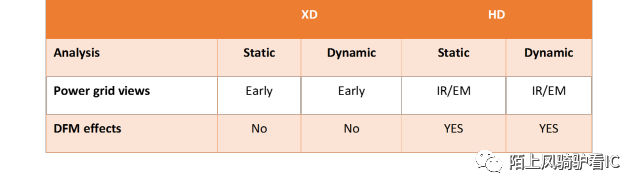

注意: 对于分析模式的精确度来说,工具有两种精确度模式:XD 和HD。 XD (accelerated definition) 被用来进行芯片设计流程中早期的电压降和电迁移分析。 HD (high definition) 用来进行设计流程最后电压降和电迁移的分析和验证。 XD 和HD 分别用在不同时期的电压降和电迁移的分析和验证,具体如下表所示。

6.2 创建和设置电源凸点(power pad)

\# 在进行rail分析之前,设计工程师需要创建和设置电源凸点。命令-auto\_fetch将会选取设计中所有的电源点。设计工程师使用电源凸点的**.pp文件来进行rail分析,该文件包含了电源凸点的物理信息。

create\_power\_pads -net VDD -auto\_fetch -vsrc\_file vdd.pp

create\_power\_pads -net VSS -auto\_fetch -vsrc\_file vss.pp

\# 在设置电源凸点之前,工程师被推荐重置设计中原始的电源凸点。重置好电源凸点之后,需要指定电源凸点的形式和电压源信息的文件。工具包含五种格式的电源凸点形式 (defpin\, pdcell\, xy\, boundary and xyiv) 。以xy为例,它表示电压源的位置是由x和y的坐标点进行标记。推荐客户使用XY坐标点的电源凸点文件。

set\_power\_pads -reset

set\_power\_pads -net VDD -format xy -file vdd.pp

set\_power\_pads -net VSS -format xy -file vss.pp

6.3 设定功耗数据

\# 设计工程师需要定义功耗数据的格式,然后将功耗数据导入Tempus。例如,使用-format current定义**.ptiavg文件是功耗分析产生的电流文件。同样,在设置功耗数据文件之前,推荐设计工程师将设计中原始的功耗数据重置。

set\_power\_data -reset

set\_power\_data –format current

{ staticPowerResults/static\_VDD.ptiavg

StaticPowerResults/static\_VSS.ptiavg }

6.4 设定pg信息

\# 在rail分析之前,需要对pg线进行设定。设计工程师需设定pg线的名称,供电电压值和pg线上承载的电压阈值。电压阈值用于后期生成电压降违例。定义force用来跳过对电源线有效性的检测。设计工程师同样被推荐先重置设计中原始的pg线信息,然后再去根据设计需求定义pg线的信息。

set\_pg\_nets -reset

set\_pg\_nets -net VDD -voltage 1.0 -threshold 0.9 -force

set\_pg\_net -net VSS -voltage 0.0 -threshold 0.05 -force

6.5 设定rail分析域

\# rail分析之前,设计工程师需要设定用以进行rail分析的电源域。对于可以开启关断的电源域,工程师只需要设定一直处于开启状态的电源线。如果工程师只需要对某条电源线进行rail分析,那么则不需要定义分析的域。

Set\_rail\_analysis\_domain -name ALL -pwrnets { VDD } -gndnets VSS

6.6 Rail分析

\# Rail分析是基于电源域或者电源线进行分析的,因此设计工程师需要定义rail分析的模式是基于电源域还是电源线。

analyze\_rail -name ALL -results\_directory ./staciRailResults -type domain all

6.7 Rail 分析结果

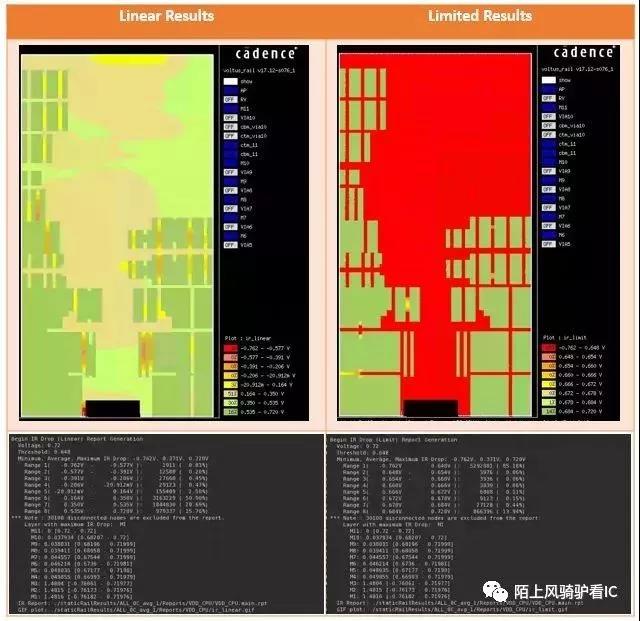

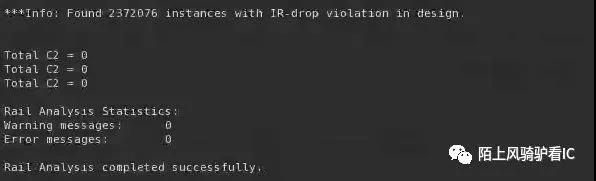

工具将会在用户定义的路径下面产生对应的分析结果,例如,ALL\_0c\_avg\_1。Rail分析的结果将会被用来进行电压降debug。设计工程师可以在Reports的路径下面检查相应的报告,并且在以电源线命名的路径下面检查对应电源线的rail分析结果。在本手册中,以 VDD\_CPU为例。设计工程师可以检查电压降分析的分布图,或者可以检查log文件来查看压降分析的范围和比例。下图所示的为电压降的分布图和log文件中显示的压降分布区间和比例。

注意:IR压降结果的显示有两种类型,线性结果和有限结果。就线性结果而言,工具会将从0到设定的电压值行平均分配,然后显示出每个电压范围内的实例占比。至于有限结果,该结果的显示和设计工程师的设定有关。在设定PG线信息时,工程师会定义每条电源线上的阈值,当线上的实际电压值高于或者定于设定的阈值时,工具便会将对应的实例标记为电压降违例。同时,工具会将高于或者低于阈值和设定的标准电压之间的范围进行平均分配,并且显示对应区间范围内的实例占比。

7. 电压降debug

在rail分析之后,需要进行电压降debug,用以识别芯片上不同区域的电压降违例,并且提供相应的违例信息供工具进行电压降违例的修复。

\# 电压降debug需要指定rail分析产生的结果目录,例如该手册中的ALL\_0c\_avg\_1。如果用户需要基于电源域来进行电压降debug,需要设定相应电源域的名称。推荐设计工程师定义eco\_report,用来产生包含电压降信息的的文件,该文件可以用来在Tempus中进行ECO修复电压降违例。设计工程师使用Nregion定义设计应当分为几个区域来进行分析,通过nworst\_instance定义多少个违例应该被报告出来。

debug\_irdrop -state\_directory./staticResults/ALL\_0c\_avg\_1

-domain ALL

-output\_directory pre-eco\_latest

-nworst\_instances ***

-eco\_report

-nregion *

设计工程师可以在pre-eco\_latest的目录下面检查debug报告,或者直接在log文件中查看相应的违例实例的具体数目。Log文件的结果显示具体如下图所示。

8. 电压降违例ECO

电压降debug会识别出设计中的IR压降违例,设计工程师需要进行ECO对电压降违例进行修复。本手册的流程推荐工程师在Tempus中进行修复。

\# 设定ECO的优化模式retime为 path\_slew\_propagation,工具会根据路径实际slew值,基于 PBA? 重新计算路径的时序延时。

set\_eco\_opt\_mode -retime path\_slew\_propagation

\# 设计工程师通过设定 max\_slack\, max\_paths和nworst分别来定义来定义ECO过程中允许的最大slack值,每个终点对应的最差路径的数目和 每个终点可以列举的路径数目。

set\_eco\_opt\_mode -max\_slack * -max\_paths * -nworst *

\# 设定allow\_multiple\_incremental 为true,允许工具可以进行多次的优化来进行电压降违例的修复。

set\_eco\_opt\_mode -allow\_multiple\_incremental true

\# 设定load \_irdrop \_db去加载电压降debug的结果。

set\_eco\_opt\_mode -load\_irdrop\_db ***

设定verbose为 true用来打印详细的电压降违例ECO的信息进入log文件。

set\_eco\_opt\_mode -verbose true

\# 设定 fix\_max\_tran and fix\_max\_cap 为false来阻碍工具修复DRV。这里,重要的是要设定fix\_ir\_drop为true,该命令将会开启Tempus的电压降违例ECO功能。

set\_eco\_opt\_mode -fix\_max\_tran false

-fix\_max\_cap false

-fix\_ir\_drop true

\# 设定setup\_recovery 为true用来修复因为电压降违例修复引起的时序违例。

set\_eco\_opt\_mode -setup\_recovery true

使用eco\_opt\_design开始进行ECO修复电压降的违例,设计工程师需要定义-drv用来触发ECO的功能。

eco\_opt\_design -drv

9. 在Innovus进行ECO

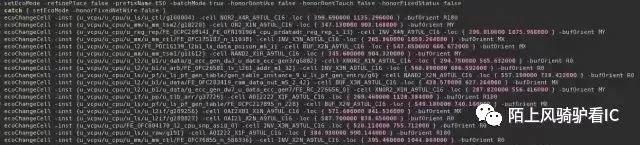

在Tempus中通过eco\_opt\_design修复电压降违例之后,工具将会产生以eco\_innovus.tcl命名的脚本文件,该脚本具体的内容由下图所示。

该eco\_innovus.tcl脚本包含需要被ECO替换的实例信息,例如实例的位置,实例的单元名称,和单元的方位。

下面的步骤介绍了在Innovus中进行ECO 的流程。需要注意的是,在完成ECO替换单元之后,设计工程师需要进行ECO绕线用以修复因为换单元而被触及的绕线。

- 开启Innovus,导入postroute的DB。

- 执行eco\_innovus.tcl

- ecoRoute

10. 验证电压降ECO之后的时序结果

在Innovus中完成ECO之后,需要验证ECO之后的时序结果。设计工程师可以直接在Innovus中调用timeDesign的引擎去报时序结果,或者抽取SPEF文件,在Tempus中验证时序和电压降结果。

总结

该手册用来帮助设计工程师在postroute的阶段进行电压降违例ECO修复。工具将会通过对标准单元进行放大或者缩小,替换不同阈值电压的标准单元进行电压降违例的修复。该手册推荐的流程将会最小限度的扰乱设计原始的时序信息,并且修复电压降违例。

通过应用该手册,设计工程师可以最小限度的触及设计时序去修复电压降违例。

参考文献

Innovus User Guide Product Version 17.10

Innovus Text Command Reference Product Version 17.10

Tempus User Guide Product Version 17.10

Tempus Text Command Reference Product Version 17.10

Voltus User Guide Product Version 17.10

Voltus Text Command Reference Product Version 17.10

来源:https://mp.weixin.qq.com/s/1tyowYNtvhOxEqCiydyLzA

作者微信公众号

相关文章推荐

更多IC设计技术干货请关注IC设计技术专栏。