如何在设计中有效考虑Dummy Metal Fill对于芯片的影响

文章作者:

张倩忆, Cadence公司数字设计事业部产品工程总监

沈龙, Cadence公司数字设计事业部产品工程师

舒越中, Cadence公司数字设计事业部产品工程师

Zhanzhong Yao, Cadence公司数字设计事业部产品工程师

1 Dummy Metal fill对于先进工艺的影响

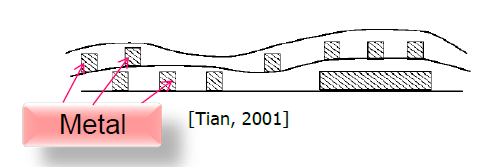

化学机械抛光 (Chemical-mechanical polishing, 简称CMP) 是半导体工艺的一个步骤。 但是其也有自身的缺陷,例如某些没有任何互联金属线的区域会产生大片的凹陷区域(如下图所示),经过了CMP这道工序之后也依然存在,其危害则是会导致信号延迟。这种情况在电路设计中非常普遍,例如在memory设计或者模拟电路设计中经常会有大片没有信号走线的区域存在。

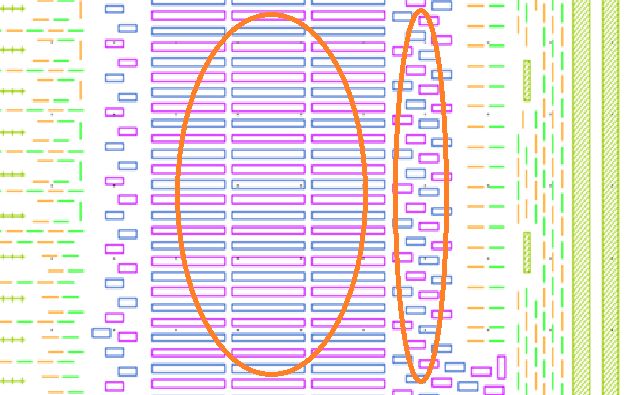

那么如何去规避这种危害呢?一种有效的方法就是去填充Dummy Metal Fill。目前的EDA公司中,Cadence公司的工具PVS 和Pegasus已经提供了成熟的插入Dummy Metal Fill的功能。以下截图为从Virtuoso Layout中,有无插入Metal Fill的对比。

未加入Metal Fill

加入Metal Fill之后

一般来说,填充Dummy Metal Fill工工作实在整个设计周期的最后,所有的DRC/LVS 时序分析签收后完成的。这些增加的金属层次所产生的额外的寄生电容于是就被忽略了,即使它们对芯片的整体有很大影响,使得芯片的速度变慢。

在以往的40nm工艺中,这些额外的寄生电容对于时序的影响大致在0.12%左右。这个影响有时甚至比静态时需分析(STA)和SPICE仿真之间的误差还要小,我们完全有理由之间忽略它。

然而在28nm工艺中,这些寄生电容的影响就提升到了2.5%。在16nm工艺中,其平均误差会达到4%。在更先进10nm、7nm及以下工艺中,其影响会更大,达到甚至超过5% 。这样的误差就无法再忽略了。

28nm工艺中有无加入MF的平均偏差在2.5%

16nm 工艺中有无加入MF的平均偏差在4%

如果去计算这些dummy金属带来的影响也会带来问题。整个芯片需要在增加了这些新增的金属图形的基础上去重新分析。包括了再重新做一次完整的寄生参数的抽取,再带入这些新增的寄生参数做完整的物理验证,时序验证,功能验证。如果最后时刻发现了问题,这样就必然会影响整个设计周期。

所以,如果能在设计周期的初始阶段就有效预估这些dummy metal fill会产生的影响的话,就能在设计时直接加以考量,避免不必要的设计周期延期。

由此,Cadence公司在Quantus工具中推出了Integrated Virtual Metal Fill (IVMF)功能。区别于以往的直接插入dummy metal fill来进行各种分析,IVMF功能可以直接在参数提取过程中根据实时的模型文件 (rule table) 去模拟dummy metal fill的影响,直接预估它们会带来的寄生参数的影响,由此直接进行各种物理信息及时序信息的仿真。

2 Quantus Integrated Virtual Metal Fill (IVMF) 解决方案

对于其他静态时序分析工具来说,IVMF只是一个提取寄生参数的工具。但当它和Innovus相结合使用的时候,能更紧密地与布局布线工作结合起来,这样才能最大发挥其优势。

在Cadence的数字布局绕线工具Innovus的RC寄生抽取中提供了不同的模式(effort-level Medium、High 和Signoff)。一般在placement和CTS时采用Medium mode抽取;Post route 和ECO 优化时使用High mode抽取,Signoff mode一般在最终时序签收时采用。

IQuantus (high effort-mode in Innovus) 和Quantus都支持IVMF功能。IVMF可以采用和真实metal fill相同的插入规则来进行模拟并抽取。同时,对于先进工艺节点中有color和非color的设计都可以支持。此外,还可以支持track-based或者non-track-based的方式进行模拟插入。

借助这样的结合,IVMF就可以在保持需要的精度的情况下大幅提升速度, 整体的提升在3-4倍左右。这是IVMF的最重要的优势。 另一个优势就是极其简单的使用方法。本文会在下面的几个子章节里详细介绍。

2.1 精度与速度的赛跑

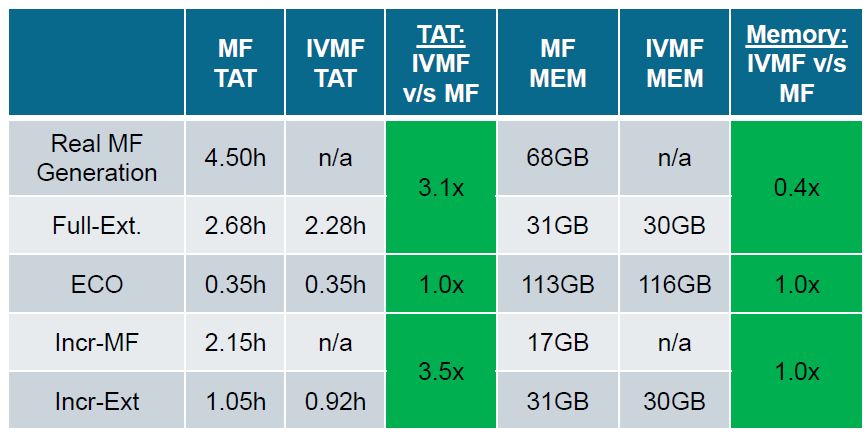

用IVMF的模式抽取,会比在实际版图中插入metal fill之后进行抽取,提升15%-20%的速度。如果算上传统的插入metal fill这一步骤所耗费的时间,并进行寄生参数抽取的整个过程,采用IVMF的方法进行寄生参数抽取可以提升3-4倍速度。如下表所示,我们可以看到IVMF在整体运行时间和消耗资源方面,在设计的每一步骤都比插入真实MF有很大的提升。

IVMF与其它MF方法耗时比较

通过对于IVMF和实际Metal Fill的结果进行分析对照之后,业界对于其精度也颇为认可。有了精确的模拟,设计者才可以有效减少时序分析和ECO和最终signoff周期。

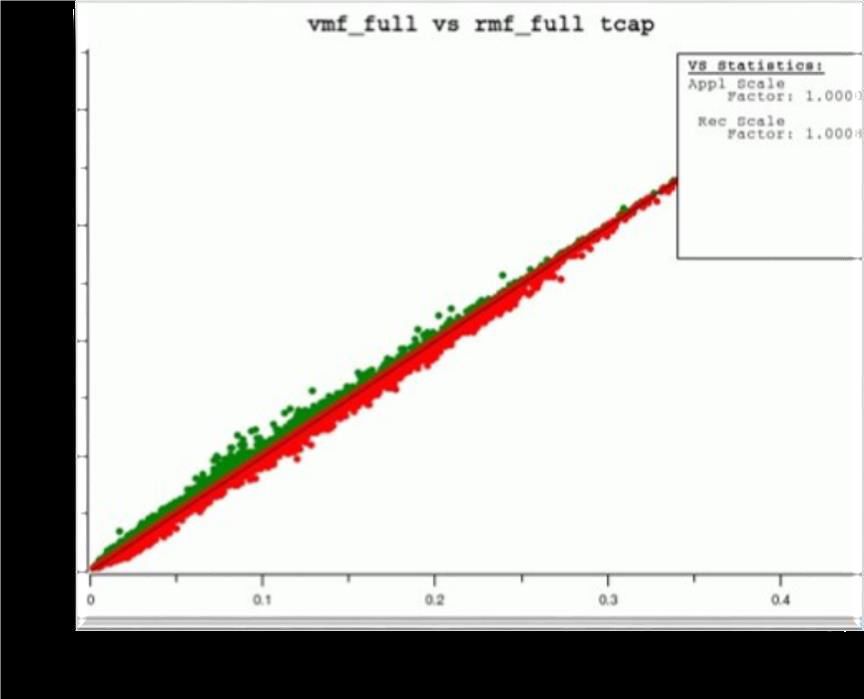

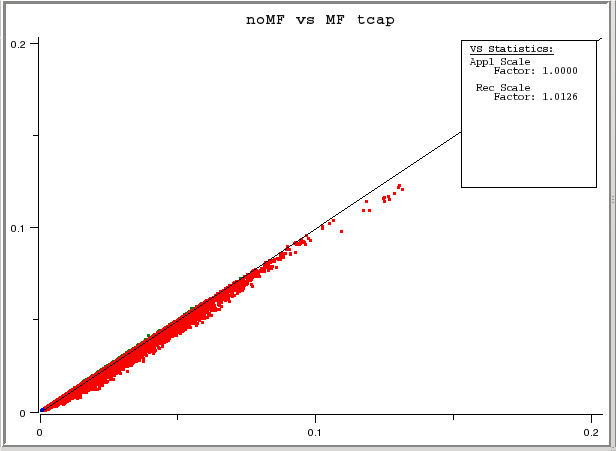

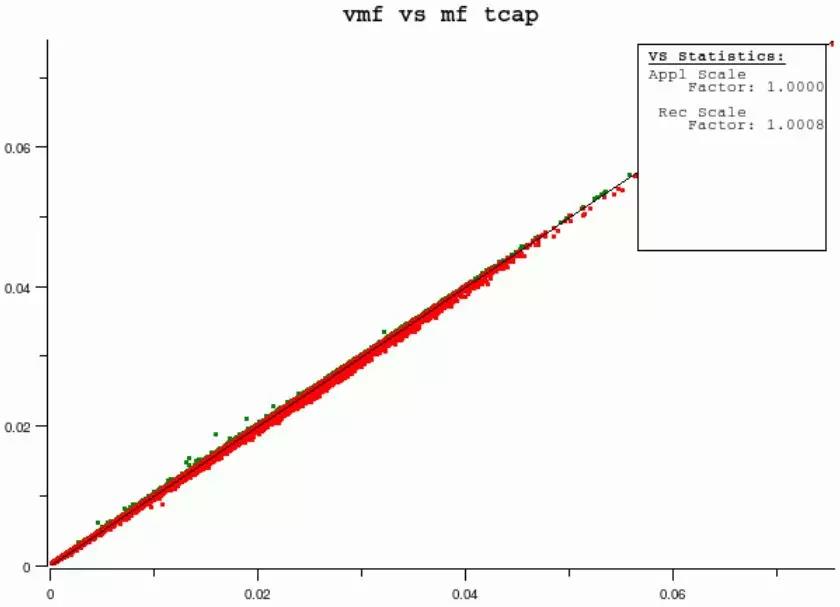

下图显示的是IVMF在某代工厂的质量检测样本中和实际Metal Fill进行的对比,其误差也是非常微小,完全可以达到研发设计的要求。以下将对其精度进行分析。

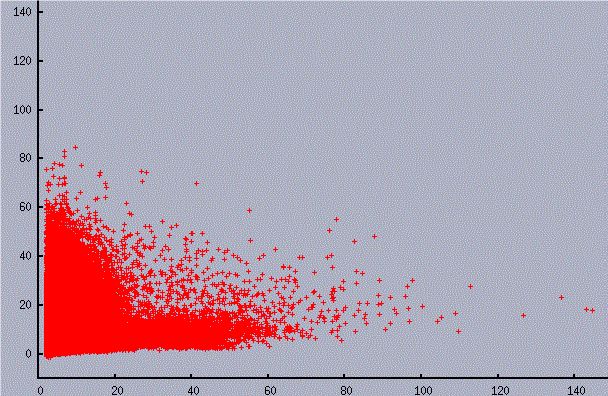

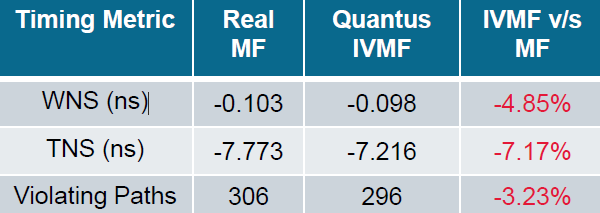

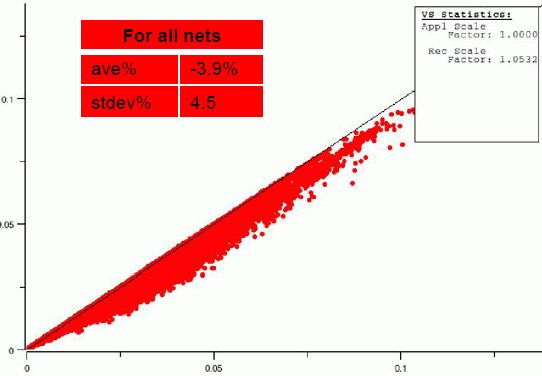

以下图表中对基于非track基准(non-track based)的IVMF和实际MF进行了对比,其误差也非常细微。对于总电容,平均偏差在0.06%以内,标准偏差在1.61%以内。对于电阻,平均偏差在0.27%以内,标准偏差在0.8%以内。

IVMF与Real MF对于总电容、电阻差异对比图

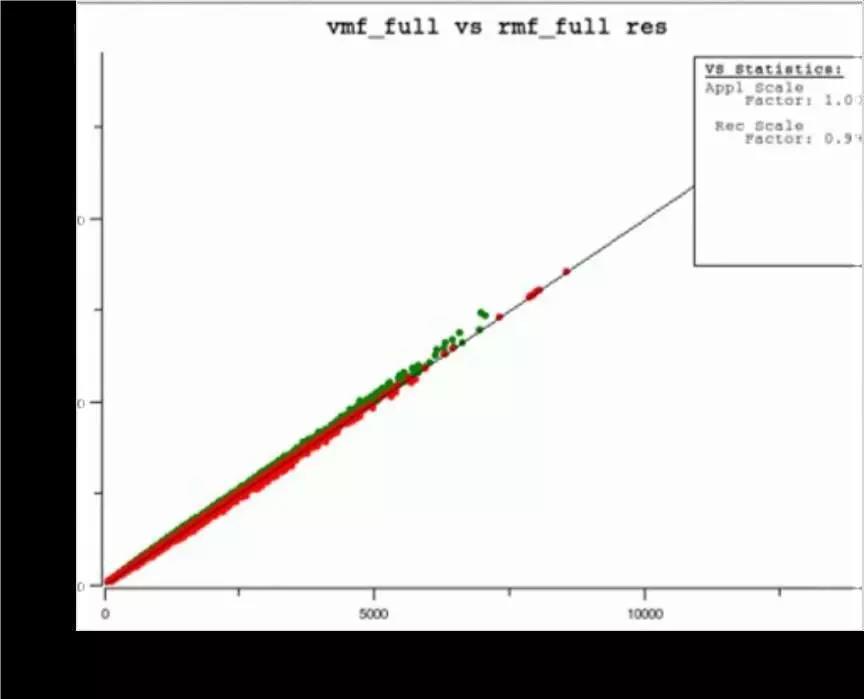

如下表所示,采用IVMF和实际Metal Fill在时序分析中对比,最差slack路径的误差在4.85%以内,总slack误差在7.17%以内,时序不满足的路径总误差为3.23%

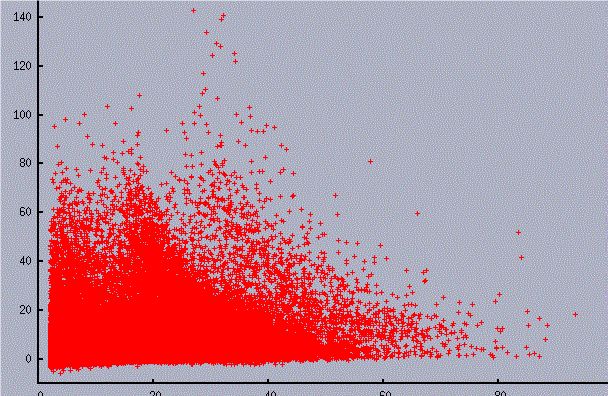

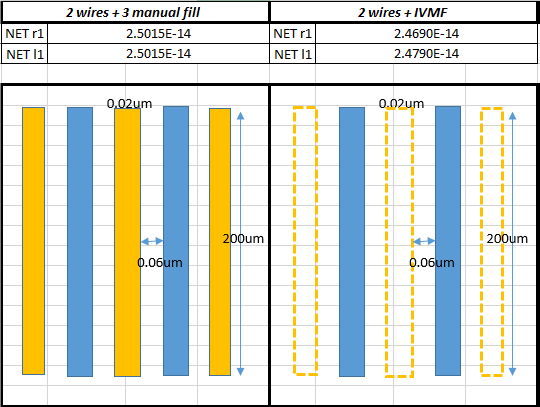

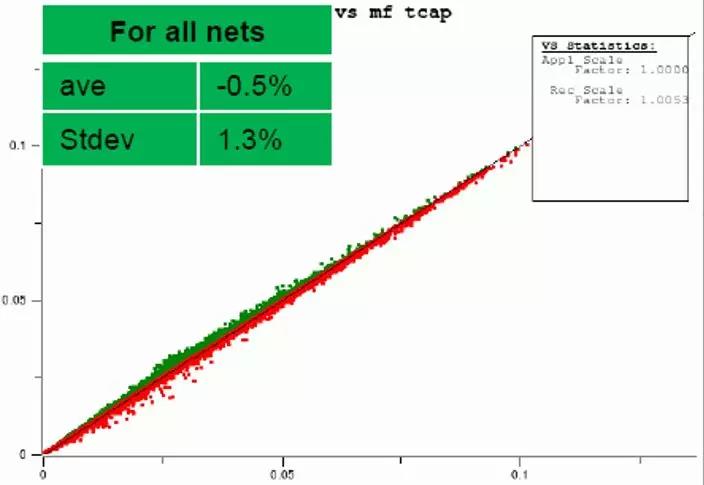

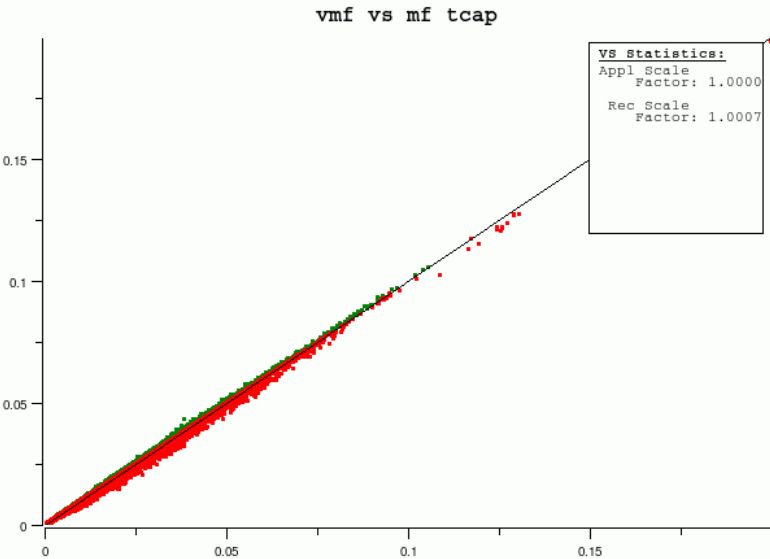

以下是以track为基准(Track Based Metal Fill, TBF)在16nm设计上对IVMF中电容精确性的对比。TBF插入规则中,fill的宽度以及其之间的间隔是固定的,只有长度可以有区别。如下图(左)所示,实际的GDS MF插入后,对于整个设计的总体寄生电容的增加在4%左右。其中某些net的电容增加甚至会达到20%-50%,对于这样幅度的增加,在芯片设计中是无法接受的。

下图(右)所示中,我们对IVMF的寄生抽取和GDS MF的抽取结果进行对比,其最大误差在1%左右。由此通过采取IVMF的方法,在此芯片设计中,有效的提高了工程师的工作效率,也节省了整个设计周期。

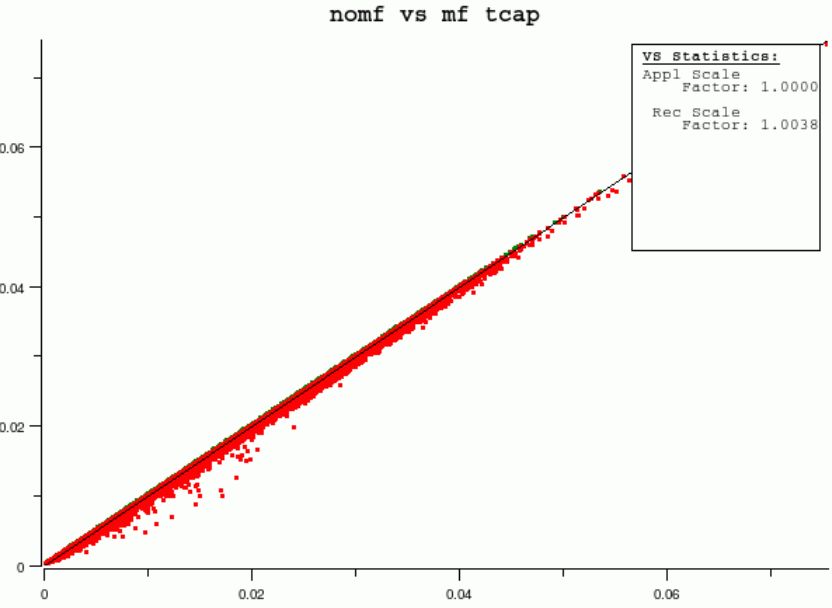

之前的段落中提到过IVMF与实际MF之间稍有误差,那么这些误差为什么会产生呢?从实际插入MF的部分来看,MF生成工具对每一层需要填充金属层都会提供多个不同的插入规则(rule),针对大小、间隔不同的区域,所插入的实际MF其大小,间距都会有所不同,如下图所示。

IVMF对同一金属层,出于对计算时间的考虑,目前只支持按照同一种规则去模拟MF。针对大小不一的这些MF,推荐使用较小的MF规则去进行模拟。这样IVMF模拟出来的寄生参数更接近实际情况,对于整体的时序分析的影响最小。

2.2 清晰简单的用法

使用IVMF的时候,只需要添加两个额外的规则文件,scheme 文件和rule文件。Scheme文件用来定义每一层金属线的名字和其对应的层次分类的名字,以及其在绕线时的走向。Rule文件则是用于定义Dummy Metal的插入规则。

Metal Scheme 文件:

金属层名 金属层类名 布线方向

。。。。。。

IVMF 规则文件:

金属层类名 长 宽 布线-MF 间隔 等等

。。。。。。

以上规则文本可以根据设计手册中的MF规则来生成,或者根据实际的MF在版图中的测量来生成。需要的话,可以参照从实际MF提取的结果调节IVMF规则表的精度。一旦确认了精度,规则表可适用于相同工艺的设计版图。

Quantus会在进行寄生参数提取时根据版图的环境和上述规则表,在几乎不需要额外运行时间的情况下实时模拟精准的MF的效果。

3先进工艺(7nm)研发中实例分析

有无MF最大误差在17%左右

IVMF与Real MF最大误差在1-2%左右

另一个N7的设计中表明,某些metal fill在较小net (<20fF) 上对寄生电容的影响可以多达40%。Quantus IVMF功能不仅显著改进了这些小net上的寄生信息的抽取,而且对于整体net的分析也达到了有效提升。

有无MF最大误差在40%左右

IVMF与Real MF最大误差在2%左右

4 总结

Quantus中提供的IVMF功能在各个工艺节点都具有很高的精度,其对于Metal Fill的模拟可以帮助工程师在布局绕线的同时考虑到Metal Fill对于芯片整体的影响,从而有效提高整体的设计效率,保证整体设计周期。

来源:https://mp.weixin.qq.com/s/9\_kdB3Muhv8Ju9SbHgxHKA

作者微信公众号

相关文章推荐

更多IC设计技术干货请关注IC设计技术专栏。