TONIC

原版见NSDI2020。

这个专题主要对基于FPGA的智能网卡技术进行介绍,上篇介绍了NanoPU、PANIC等,这次介绍“Enabling Programmable Transport Protocols in High-Speed NICs”。高山留存阅读点滴。

传输协议,连同网络堆栈的其余部分,传统上是在软件中运行的。尽管努力提高性能和效率,软件网络堆栈往往消耗30-40%的CPU时间,跟上当今数据中心的应用程序需求。随着数据中心转向100 Gbps以太网,软件网络堆栈的CPU利用率变得越来越高。因此,多家供应商开发了完全在网络接口卡(NIC)上运行的硬件网络堆栈。但是,这些NIC上只实现了两种主要传输协议,它们都是硬连接的,并且只能由供应商修改:

RoCE。RoCE用于远程直接内存访问(RDMA),使用DCQCN进行拥塞控制,使用简单的返回N方法进行可靠的数据传输。

TCP协议。一些供应商将自己选择的TCP变体卸载到NIC上,以便直接通过socket API使用(TCP卸载引擎)或启用RDMA(iWARP)。

然而,这些协议只使用了过去几十年中提出的用于可靠传输和拥塞控制的无数可能算法中的一小部分。例如,最近的研究表明,低延迟数据中心网络可以显著受益于接收端驱动的传输协议,这在当前的硬件堆栈中不是一个可选项。为了在Microsoft数据中心部署RoCE NIC,运营商需要修改数据传输算法以避免网络中的活锁,但必须依赖NIC供应商来进行更改。已经提出了其他算法来改进RoCE的简单可靠传输算法。TCP在各种网络中多年来的优化列表证明了传输协议对可编程性的需求。

TONIC主要研究如何使硬件传输协议可编程。即使NIC供应商开放了硬件编程接口,在高速硬件中实现传输协议也需要大量的专业知识、时间和精力。为了满足100Gbps的处理速度,传输协议应该每隔几纳秒生成并传输一个数据包。它应该能够处理超过1000个活动流,这在今天的数据中心服务器中是很普遍的。然而,NIC在片上内存和计算资源的数量方面受到极大的限制。

高速网卡上的传输协议可以进行编程,而不会让用户暴露于高速硬件编程的全部复杂性。主要基于两个主要因素:

首先,可编程传输逻辑是实现灵活的硬件传输协议的关键。传输协议的实现执行若干功能,例如连接管理、数据缓冲区管理和数据传输。然而,它的中心责任,关键创新点,是决定要传输的数据段(数据传递)和时刻(拥塞控制),称为传输逻辑。因此,高速网卡上可编程传输协议的关键是允许用户修改传输逻辑。

其次,可以利用传输逻辑中的常见模式来创建可重用的高速硬件模块。尽管它们在应用程序级API(例如,TCP的套接字和字节流抽象与RDMA的基于消息的谓词API)以及连接和数据缓冲区管理方面存在差异,但传输协议有几个共同的模式。例如,不同的传输协议使用不同的算法来检测丢失的数据包。然而,一旦一个数据包被丢弃,可靠的传输协议将其重传优先于发送一个新的数据段。在拥塞控制中,给定由控制环路确定的参数(例如,拥塞窗口和速率),只有几种常见的方法可以计算流在任何时候可以传输多少字节。这使能够为硬件中的传输逻辑设计一个有效的“模板”可以用一个简单的API编程。

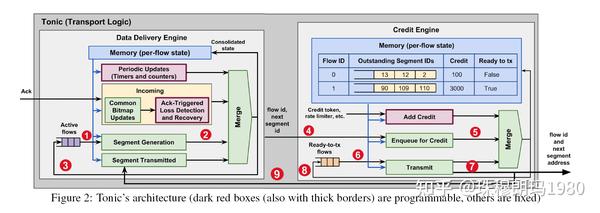

基于这些观点,设计并开发了Tonic,这是一种可编程的硬件体系结构,可以使用简单的API实现各种传输协议的传输逻辑,同时支持100Gbps的数据速率。每个时钟周期,Tonic都会生成下一段的地址以供传输。数据段由下游DMA管道从内存中提取,并由硬件网络堆栈的其余部分转换为完整的数据包。

Tonic将驻留在NIC上,取代传输协议硬件实现中的硬编码传输逻辑(例如,未来的RDMA NIC和TCP卸载引擎)。Tonic为传输逻辑提供了一个统一的可编程体系结构,与不同传输协议的具体实现如何执行连接和数据缓冲区管理以及它们的应用程序级api无关。然而,将描述Tonic如何与传输层的其余部分进行通用接口(x2),以及如何将其集成到Linux内核中,以使用socketapi与应用程序进行交互(x5)。

智能网卡专题:

FPGA-inline加速器SmartNIC(2):PANIC

FPGA-inline加速器SmartNIC(1):NanoPU

作者:珠穆朗玛2048

来源:https://zhuanlan.zhihu.com/p/359426149

更多FPGA智能网卡相关技术干货请关注FPGA加速器技术专栏。