参考资料资料原文链接: [链接]作者:到处找资料的文章来源:TrustZone推荐阅读如何做一颗SOC——工具篇做IP设计是一个非常幸福的岗位做SOC设计就是连连看除了PCIE,DDR,你还知道哪些IP?Verilog代码设计之时分复用更多IC设计干货请关注IC设计专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。

对于前端设计人员,经常会需要一个MUX来对工作模式,数据路径进行明确(explicit)的声明,这个对于中后端工程师下约束也很重要。这里介绍一种巧用的RTL原语,实现MUX的方法。闲言少叙,ICerGo!

相较于仅基于逻辑连接的MBFF封装,如果考虑到布局的实际情况,那么就有physical aware的in-place的MBFF封装实现,这种思路可以应用在常见的DCT/DCG/genus\_PLE 等综合流程。 和in-compilre相比,这种in-place的MBFF封装,最大的优势,就是physical aware。譬如如下示意图:

在两年前的一篇文章简单介绍了Multi-bit的一些基本知识,详情请戳:芯片设计里的Multi-Bit FF探究 在此篇旧文的基础上,其实MBFF (Multi-bit FF)还有不少技术细节值得再次学习和理解。据此,这里再次把MBFF相关的技术和流程相关的细节梳理的更为清晰一些。闲言少叙,ICer GO!

有人认为我验证做得很牛,也有人认为我的验证早就丢下了;有人认为我发现了各个项目的不少问题,也有人认为我在CMM库的几百个问题单大部分纯属灌水。

2024年3月初,在美国硅谷举办的DVCon2024上,IEEE-SA和Accellera联合宣布通过IEEE Get Program可以免费获取IEEE 1800-2023 SystemVerilog语言参考手册。

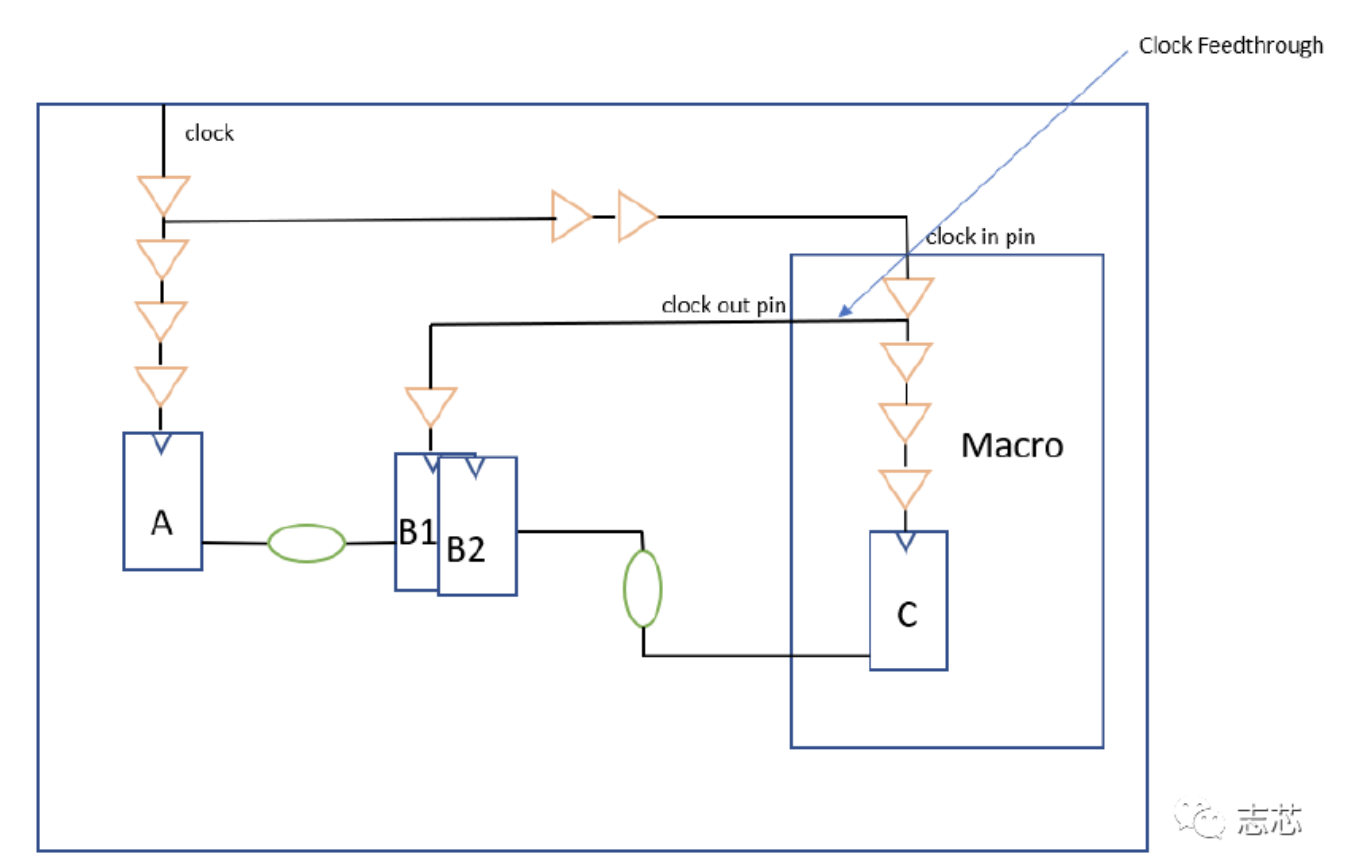

为什么需要分段去做时钟树呢?因为在某些情况下,按照传统的方法让每一个clock group单独去balance,如果不做额外干预,时钟树天然是做不平的。

现代嵌入式处理器,例如NXP的i.MX 8M Plus系列处理器,配备了图像信号处理器(ISP)。它们通常被称为图像处理器或图像处理单元(IPU),专为快速高效地处理摄像头数据而设计。

区别于其他用途的芯片,车规级芯片有一套独立的适用于汽车电子元件的规格标准,比如它的工作温度范围在-40°~125°、元器件的寿命要达到20年、抗冲击的能力要比较强,还有很多专业的电气特性测试、环境应力测试、可靠性测试等等。而消费电子的要求则要低很多,它的工作温度通常在0~70°之间,芯片寿命在3~5年左右。

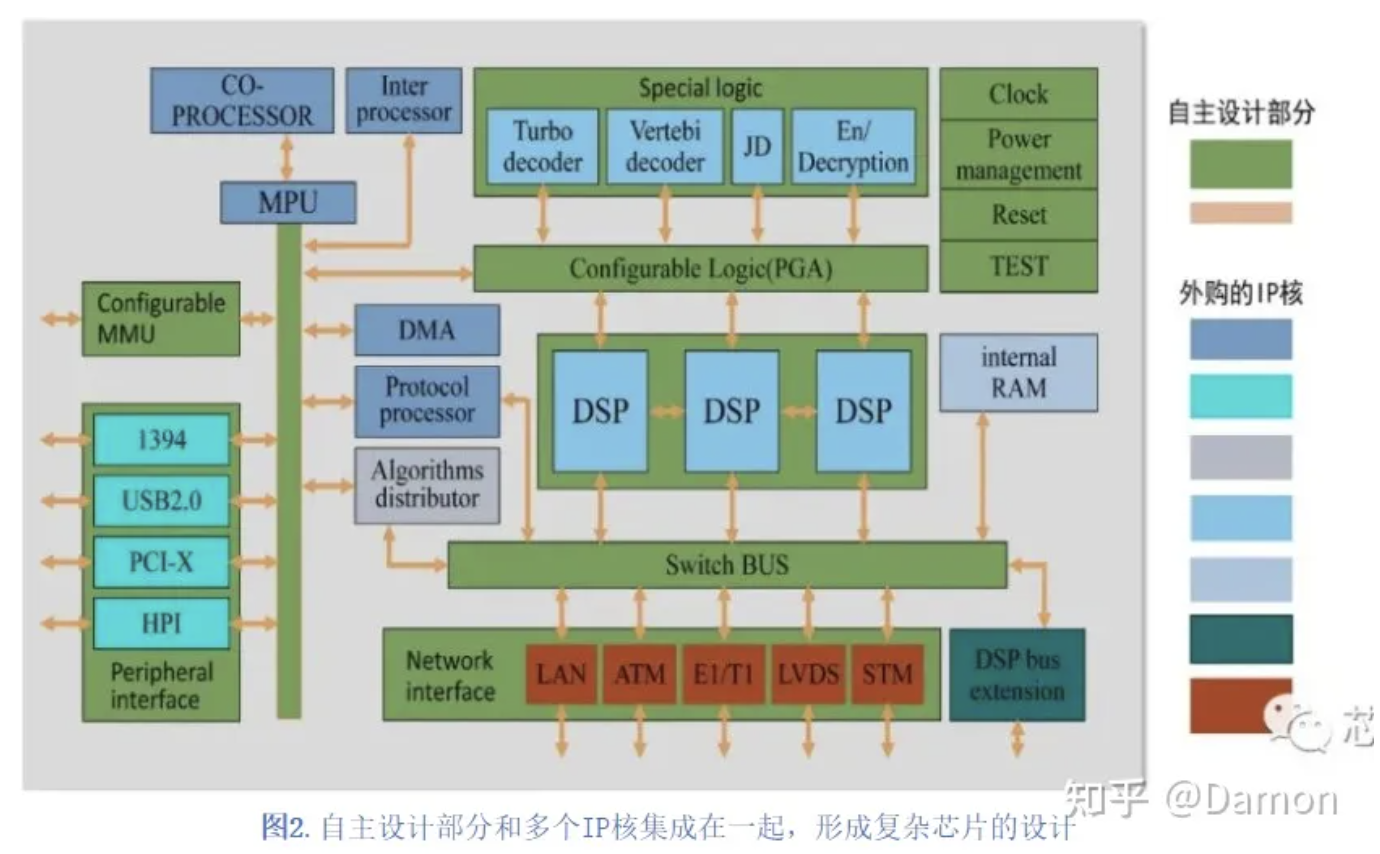

IP一般指IP核,是芯片中具有独立功能的电路模块的成熟设计。该电路模块设计可以应用在包含该电路模块的其他芯片设计项目中,从而减少设计工作量,缩短设计周期,提高芯片设计的成功率。该电路模块的成熟设计凝聚着设计者的智慧,体现了设计者的知识产权,因此,芯片行业就用IP核(Intellectual Property Core)来表示这种...

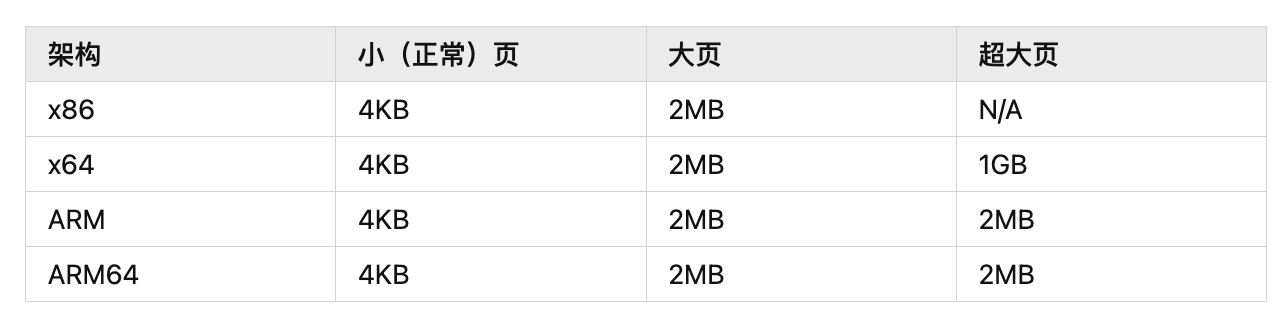

内存管理包含的内容有:逻辑和物理地址映射、内存分配、内部和外部碎片和压缩、分页,以及虚拟内存:请求分页、页面替换策略。本章将详细阐述内存相关的概念、技术、原理和机制。

本章涉及线程和进程间的通信、竞争条件、关键部分、互斥、硬件解决方案、严格交替、彼得森解决方案、生产者-消费者问题、信号量、事件计数器、监视器、消息传递和经典IPC问题,以及死锁的定义、特征、预防、避免等。

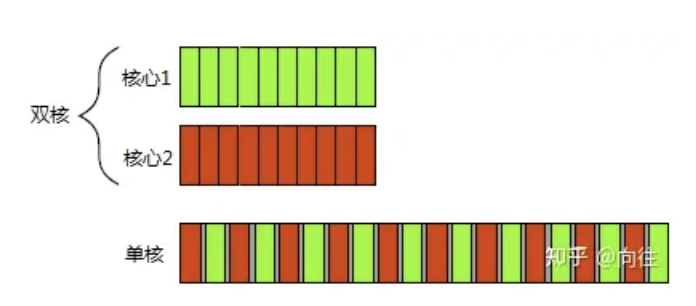

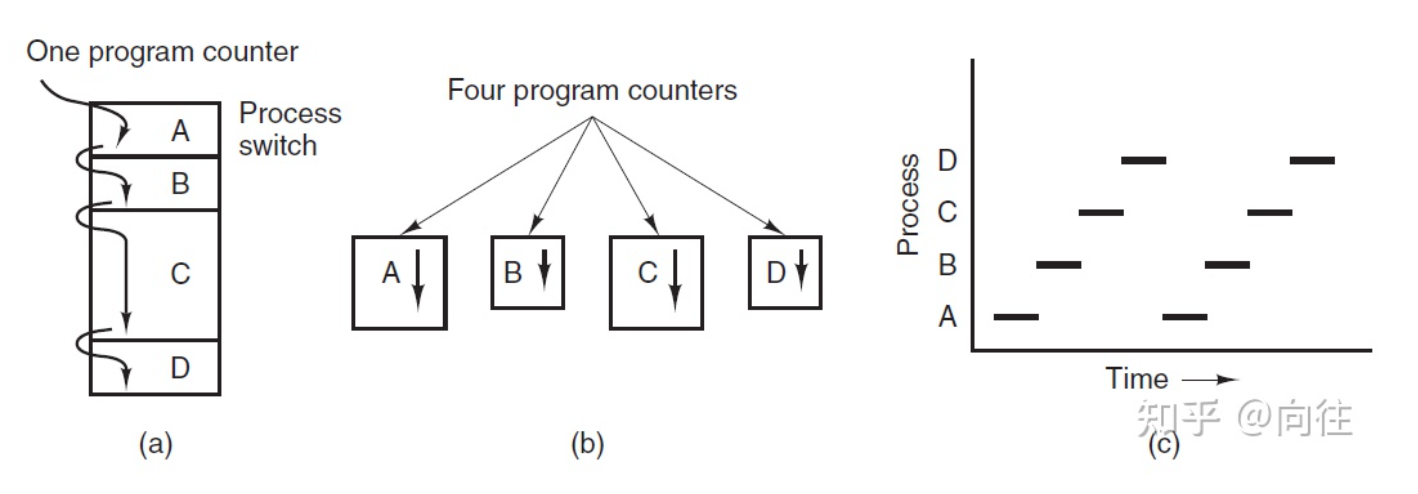

在这种模型中,计算机上所有可运行的软件,有时包括操作系统,都被组织成若干顺序进程,或者简称为进程。进程只是执行程序的一个实例,包括程序计数器、寄存器和变量的当前值。从概念上讲,每个进程都有自己的虚拟CPU。当然,在现实中,真正的CPU在进程之间来回切换,但为了理解系统,考虑以(伪)并行方式运行的进程集...

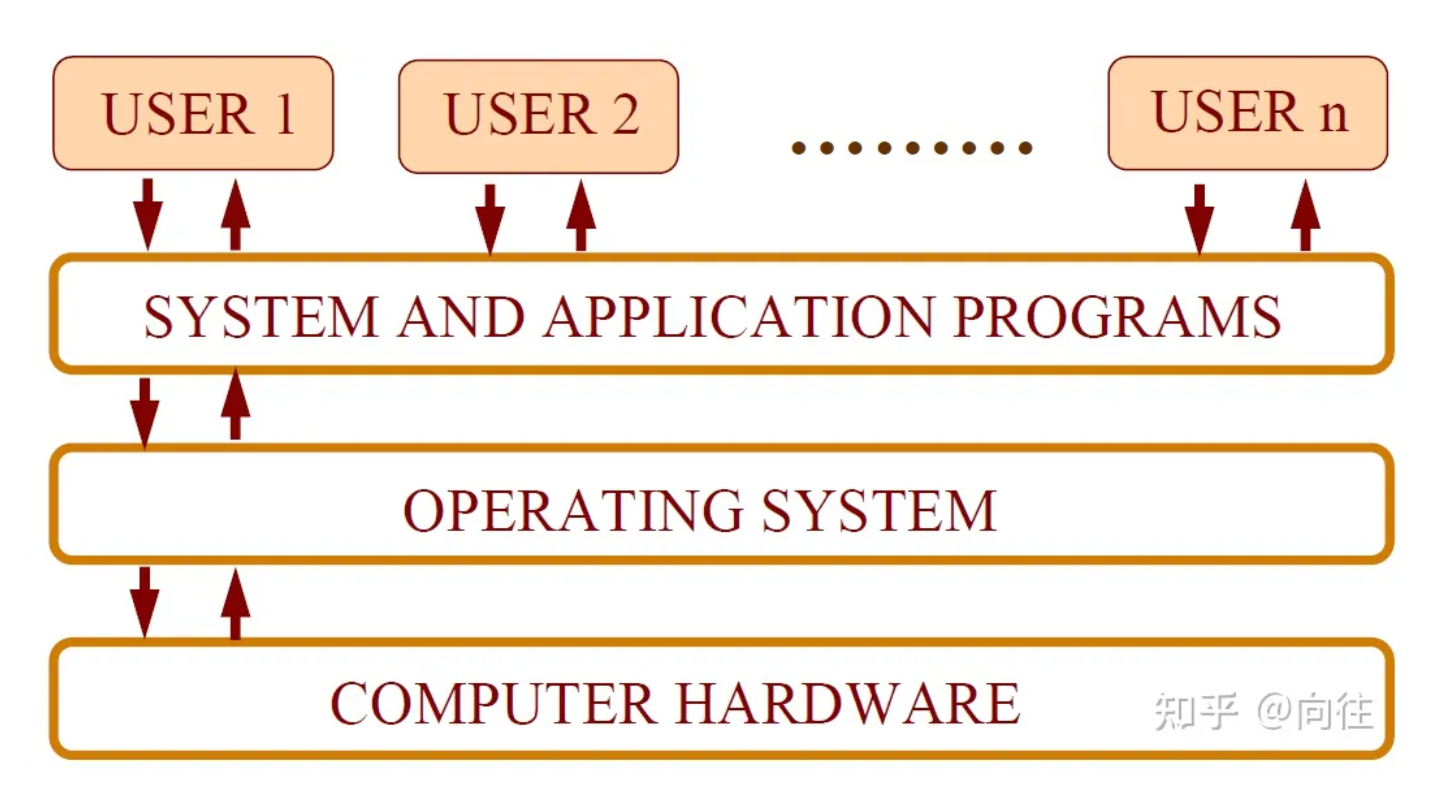

迄今为止,博主在博客中阐述的内容包含渲染技术、性能优化、图形API、Shader、GPU、游戏引擎架构、图形驱动等等技术范畴的内容,这些内容都仅仅局限于单个应用程序之中,常常让人有”只缘身在此山中“的感叹。现在是时候更进一步了——进入操作系统(Operating System,OS)的范畴,以更高的层次去看待渲染体系,以便我们能...

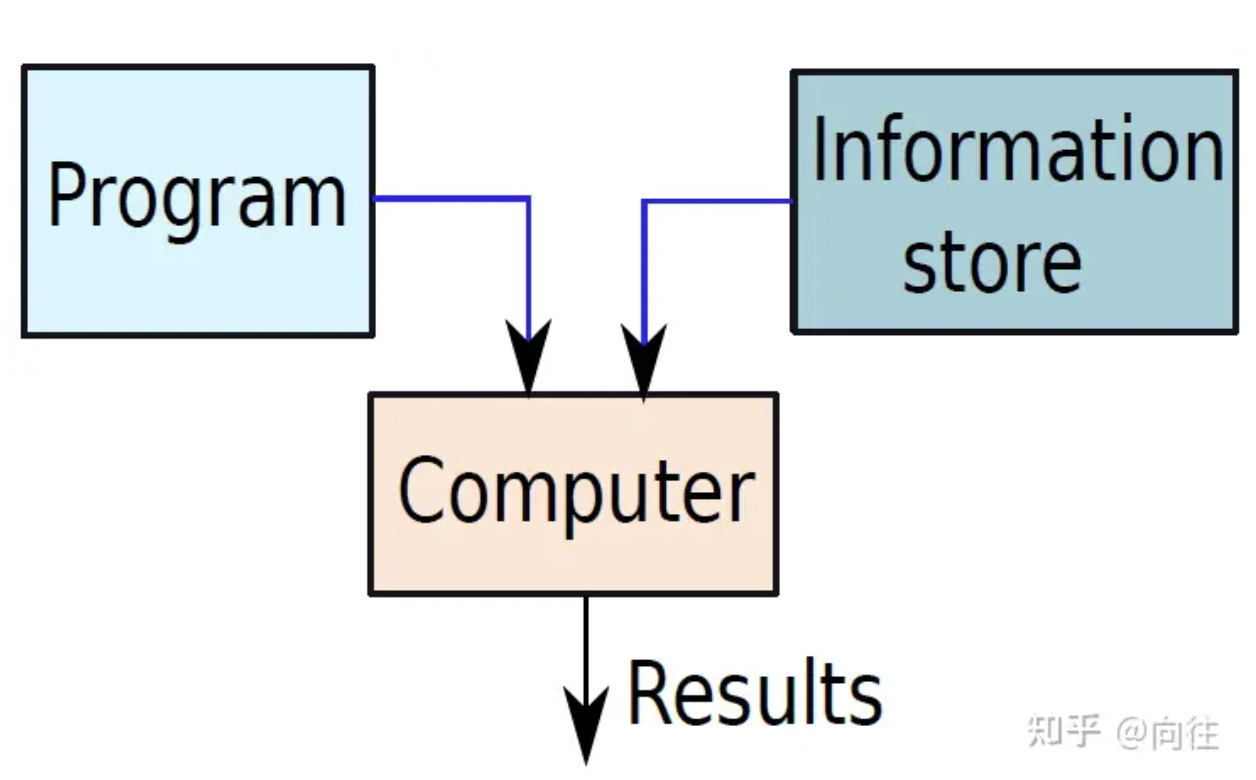

之前的很多篇文章已经大量涉及了各种各样的硬件和技术,本篇将更加全面、系统、深入地阐述计算机的硬件组成和体系架构,从而形成自上而下的计算机体知识体系。本篇主要阐述以下内容:

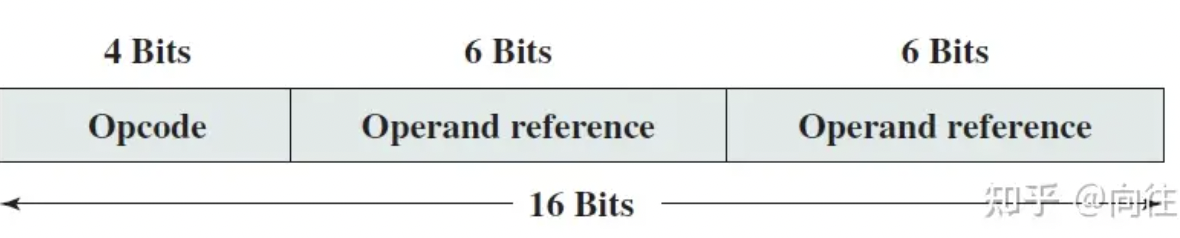

就像任何语言都有有限的单词一样,处理器可以支持的基本指令/基本命令的数量也必须是有限的,这组指令通常称为指令集(instruction set),基本指令的一些示例是加法、减法、乘法、逻辑或和逻辑非。请注意,每条指令需要处理一组变量和常量,最后将结果保存在变量中,这些变量不是程序员定义的变量,是计算机内的内部位...

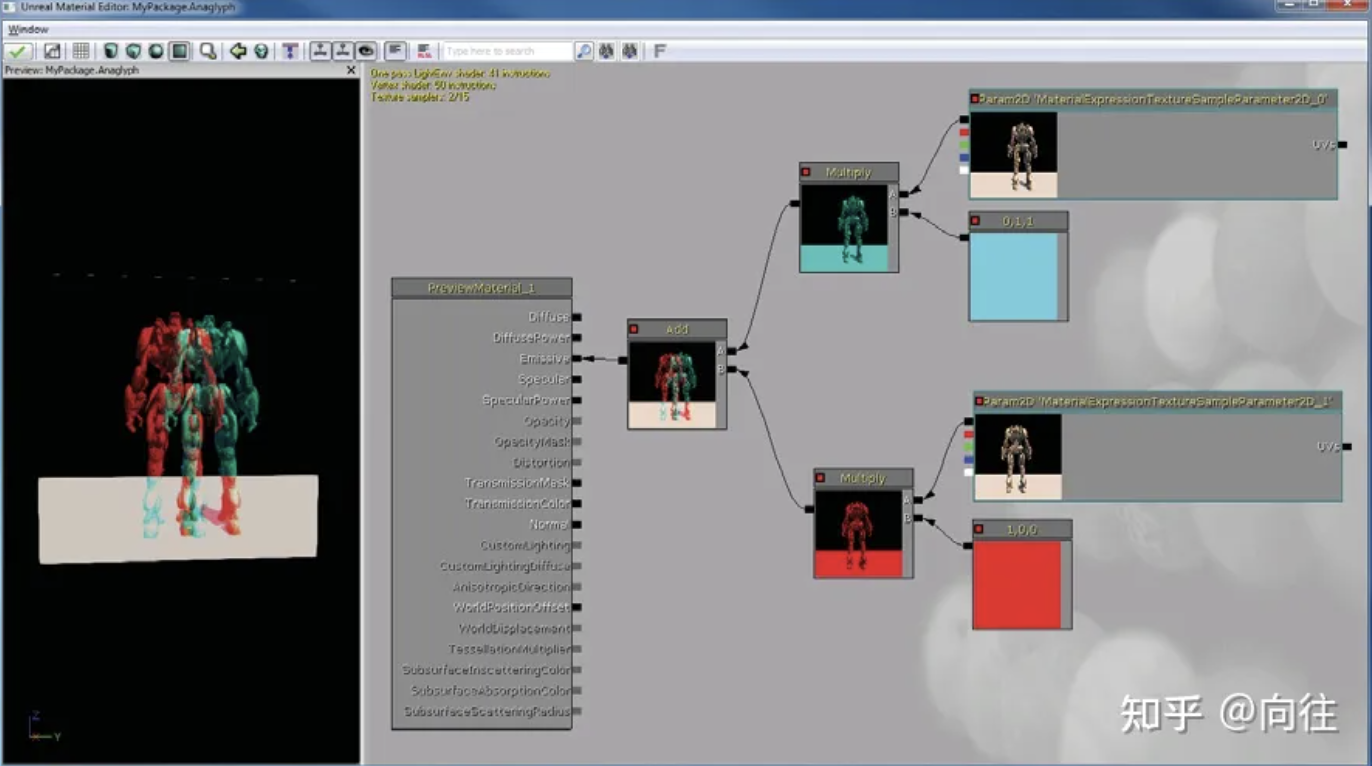

早在UE3时代,就已经通过节点图支持了VR的渲染,其中渲染管线的不同组件可以在多个配置中重新排列、修改和重新连接。根据所支持的节点类型,有时可以以产生特定VR技术效果的方式配置节点。下图显示了一个示例,它描述了虚幻引擎的材质编辑界面,该界面被配置为渲染红色青色立体图像作为后处理效果。

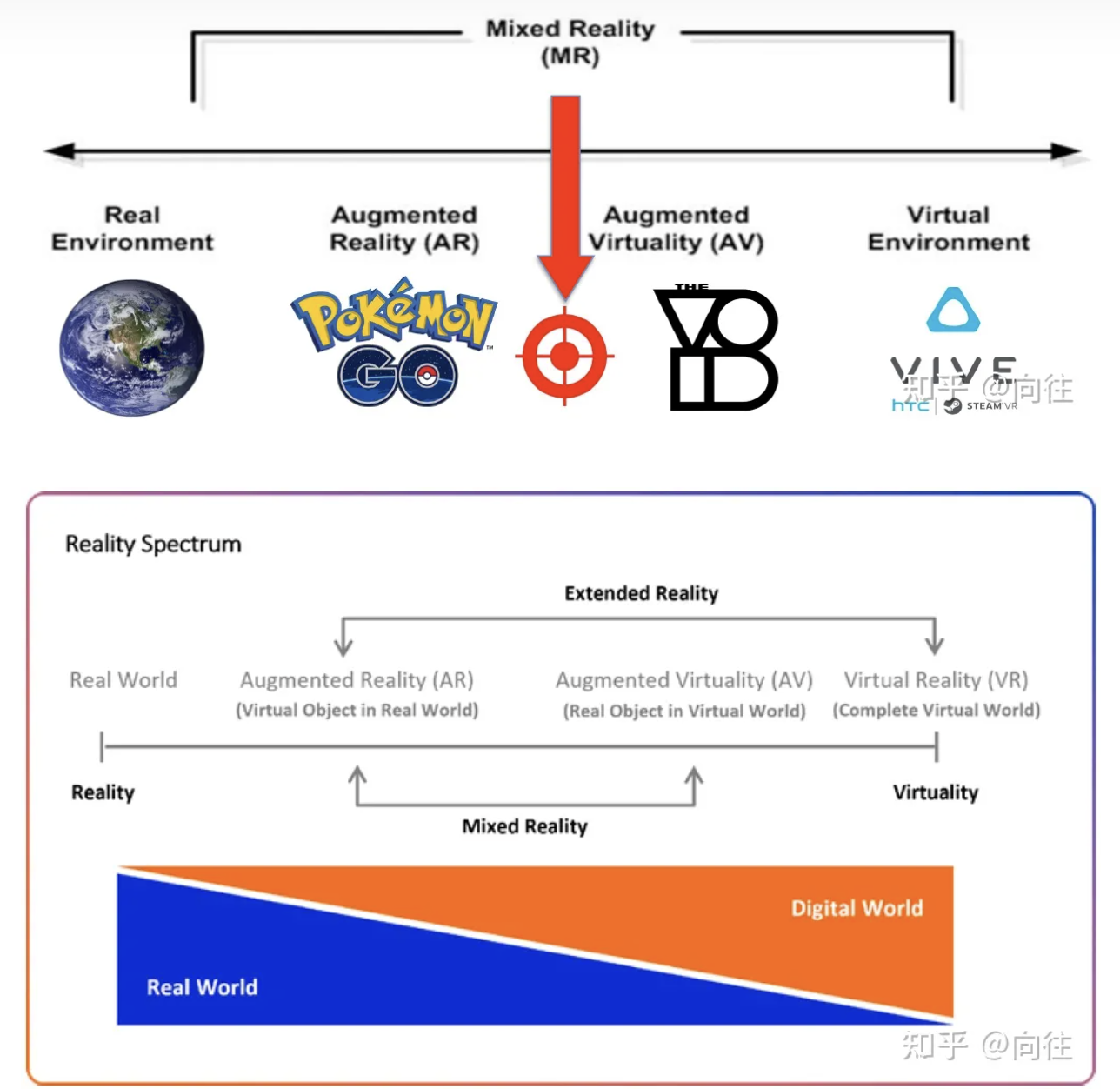

虚拟现实(VR)因伊万·萨瑟兰(Ivan Sutherland)在20世纪60年代的工作而广受赞誉。在过去的50年里,虚拟现实技术的普及程度上下波动。特别是,近年来,虚拟现实在虚拟现实及其对应产品增强现实(AR)方面的投资吸引了许多科技巨头的注意。例如,2014年,Facebook以20亿美元收购了虚拟现实技术公司Oculus,并开始推动虚...

说起虚拟机,相信作为技术人员的小伙伴们不会感到陌生。虚拟机的使用场景非常多,如搭建测试环境、在 Windows 系统中安装 Linux 或在 Mac 机器上运行 Windows 系统、甚至还可以用来进行安全实验。

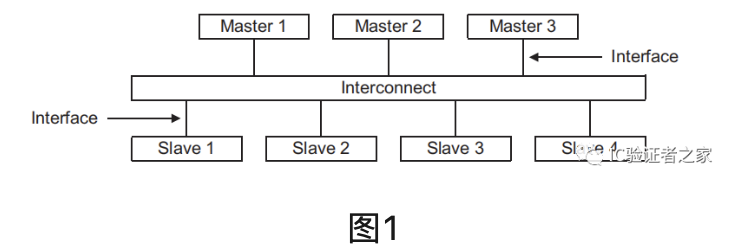

提纲:1. AXI基本概念AMBA总线中APB,AHB,AXI的关系读操作写操作2. AXI OrderingOutstanding。Aw-W-B的valid/ready依赖关系AR-R的valid/ready依赖关系相同ID数据保序,不同ID支持out of ordervalid与ready的依赖关系通道内的Ordering通道之间的Ordering3. AXI Burst数据量的约束不能跨4K4. 总线异常Error Response的处理...