Corundum

原版见FCCM2020

代码见: https://github.com/ucsdsysnet/corundum

这个专题主要对基于FPGA的智能网卡技术进行介绍,上篇介绍了NanoPU、PANIC、Tonic等,这次介绍“Corundum: An Open-Source 100-Gbps NIC ”,完全开源的100Gbps网卡,主要设计实现了一种可配置的DMA。高山留存阅读点滴。

网络接口控制器(NIC)是计算机与网络进行交互的关口。网卡在软件栈和网络之间形成一个桥梁,即定义了网络接口。网络接口的功能以及这些功能的实现都在迅速发展变化。这些变化是由不断增长的带宽/速率和支持高性能分布式计算和虚拟化的NIC功能的双重需求推动的,不断增长的带宽导致许多NIC功能必须用硬件而不是软件来实现。另一方面,为了实现高级的协议和网络体系结构,需要新的网络功能,例如对多个队列的精确传输控制。

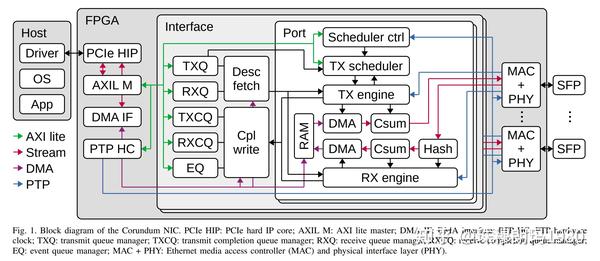

为了满足新的网络协议和架构的开放式开发平台的需求,设计开发一个基于FPGA的高性能开放源码NIC原型平台Corundum,能够运行至少94Gbps,是完全开源的,连同它的驱动程序,可以使用在一个完整的网络协议栈。这种设计既具有好的移植型又紧凑,支持许多不同的设备,同时也为进一步定制(即使在较小的设备上)留下了充足的硬件资源。Corundum模块化设计和可扩展性允许协同优化的硬件/软件解决方案在系统中开发和测试高级网络应用程序。

动机和相关工作

现有NIC的网络接口功能设计关键在于硬件和软件之间进行功能划分。硬件NIC功能分为两大类。第一类由简单的卸载功能组成,这些功能可以从CPU中移除一些逐包的处理,例如校验和/哈希计算和分段卸载,这些功能使网络协议栈能够批量处理数据包。第二类包括必须在NIC上硬件中实现的功能,以实现高性能和公平性,这些特性包括流控制、速率限制、负载均衡和时间戳。

(1)ASIC NIC

传统的NIC的硬件功能实现于专有的专用集成电路(ASIC)中。再加上规模经济,这使得ASIC网卡具有高性能低成本特点。然而,这些ASIC可扩展性是有限的,添加新硬件功能的开发成本高周期长。为了克服这些限制,开发了各种智能NIC和软件NIC。智能网卡通常通过提供大量可编程处理核心和硬件原语,在网卡上提供强大的可编程性。这些资源可用于从主机上卸载各种应用程序、网络和虚拟化操作。然而,智能NIC不一定能很好地扩展到高性能,并且硬件功能可能受到限制。

(2)软件NIC

软件NIC通过在软件中实现网络功能,提供了最大的灵活性,绕过了大多数硬件卸载功能。因此,可以快速开发和测试新功能,但需要进行各种权衡,包括占用主机CPU周期和不一定支持线速处理。此外,由于软件固有的随机中断特性,开发需要精确传输控制的网络应用程序是不可行的。尽管如此,许多研究项目通过修改网络协议栈或使用内核旁路框架(如数据平面开发套件(DPDK))在软件中实现了新的NIC功能。

(3)FPGA NIC

基于FPGA的NIC结合了基于ASIC的NIC和软件NIC的优点:能够以线速运行,提供低延迟和精确计时,同时具有相对较短的功能开发周期。高性能、专有、基于FPGA的NIC也已有很多。例如,阿里巴巴开发了完全定制的基于FPGA的RDMA专用NIC,用于运行精确拥塞控制协议(HPCC)。商业产品也存在,包括Exablaze和Netcope等产品。

基于FPGA的数据包处理解决方案包括Catapult,它实现了网络应用程序卸载,FlowBlaze,它在FPGA上实现了可重构的匹配动作引擎。然而,这些平台将标准NIC功能留给了一个单独的基于ASIC的NIC,并且完全作为一个“bump-in-the-wire”模式来运行,不提供对NIC调度器或队列的显式控制。

其他项目使用软件实现或部分硬件实现。Shoal描述了一种网络体系结构,它使用自定义NIC和快速链路层交叉开关执行单元路由。Shoal是在硬件中构建的,但是只使用合成流量进行评估,没有与主机连接。SENIC描述了基于可伸缩NIC的速率限制。调度器的硬件实现是单独评估的,但系统级评估是在带有定制排队规程(qdisc)模块的软件中执行的。PIEO描述了一个灵活的NIC调度器,它是在硬件中单独评估的。NDP是数据中心应用程序的接收端驱动的拉模式传输协议。使用DPDK软件NICs和基于FPGA的交换机对NDP进行评估。Loom描述了一种高效的NIC设计,并用BESS软件对其进行了评估。

与基于ASIC的NIC类似,商用的基于FPGA的NIC往往是专有的,具有不能修改的基本“黑盒”功能。基本NIC功能的不能升级,严重限制了开发新网络应用程序的实用性和灵活性。

商用高性能DMA组件,如Xilinx XDMA核心和QDMA核心,以及Atomic Rules Arkville DPDK 加速核心,没有提供完全可配置的硬件来控制传输数据流。Xilinx DMA内核是为计算卸载应用程序而设计的,因此提供了非常有限的排队功能,并且没有简便方法来控制传输调度。Xilinx QDMA核心和Atomic Rules Arkville DPDK加速核心通过支持少量队列和提供DPDK驱动程序面向网络应用程序。然而,XDMA核心支持的队列数量是的2K队列,Arkville核心的队列达128个队列,这两个核心都没有提供精确控制数据包传输的简单方法。

NetFPGA等开源项目只为基于FPGA的数据包处理提供了一个功能库和平台,并不是专门为NIC开发而设计的。此外,NetFPGA NIC参考设计使用了Xilinx XDMA内核,它不是为网络应用而设计的。将NetFPGA板的参考NIC设计中的Xilinx-XDMA内核替换为Corundum,可以获得更强大、更灵活的原型平台。

Corundum别于所有这些项目,因为它是完全开源的,可以运行在一个标准的主机网络栈,在实际的物理链路。它提供了数千个传输队列和可扩展的传输调度程序,用于流的细粒度控制。这就为开发结合了硬件和软件功能的网络应用程序提供了一个强大而灵活的开源平台。

智能网卡专题:

FPGA-inline加速器SmartNIC(3):Tonic

FPGA-inline加速器SmartNIC(2):PANIC

FPGA-inline加速器SmartNIC(1):NanoPU

作者:珠穆朗玛2048

来源:https://zhuanlan.zhihu.com/p/359754525

更多FPGA智能网卡相关技术干货请关注FPGA加速器技术专栏。