AccelNet

原版见NSDI 2018。

这个专题主要对基于FPGA的智能网卡技术进行介绍,上篇介绍了NanoPU、PANIC、Tonic、Corundum、NICA等,这次介绍“Azure Accelerated Networking: SmartNICs in the Public Cloud”,主要针对SR-IOV对HostSDN的策略实施影响,提出AccelNet,实现GFT。高山留存阅读点滴。

HostSDN引入

公有云是在线软件服务大规模迅速增长的关键技术。仅在微软Azure云中,服务就消耗了数以百万计的处理器内核、E字节的存储空间和数P字节的网络带宽。公有云网络性能,包括带宽和延迟,对于大多数云工作负载,尤其是面向客户的交互式工作负载来说至关重要。

微软Azure作为一家大型公有云提供商,已经在基于主机的软件定义网络HostSDN上构建了自己的云网络AccelNet,使用这些技术实现了几乎所有的虚拟网络功能,例如带有客户提供的地址空间的私有虚拟网络、可扩展的L4负载平衡器、安全组和访问控制列表(ACL),虚拟路由表、带宽计量、QoS等等。这些特性由主机平台负责,这通常意味着在hypervisor中运行的软件。

提供这些服务的成本继续增加。在短短几年时间里,将网络速度提高了40倍甚至更多,从1GbE提高到40GbE+,并添加了许多新功能。尽管构建了越来越完善和高效的HostSDN数据包处理功能,但在主机上运行这个软件协议栈需要额外的CPU周期。为这些服务消耗CPU会占用客户VM可用的处理能力,并增加提供云服务的总体成本。

SR-IOV使HostSDN失效?

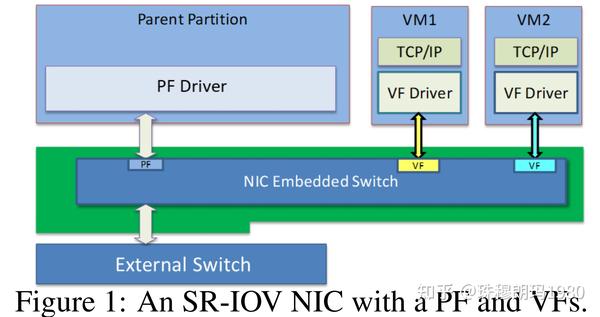

单根I/O虚拟化(SR-IOV)被提出,通过允许从VM直接访问NIC硬件来降低CPU利用率。但是,这种直接访问将绕过HostSDN协议栈,使NIC负责实现所有SDN策略。由于这些策略变化很快(几周到几个月),因此,需要一个解决方案,该解决方案可以提供类似软件的可编程性,同时提供类似硬件的性能。

在HostSDN中Azure加速网络(AccelNet),实现在基于FPGA的Azure SmartNIC上。AccelNet在虚拟化环境中提供近本机网络性能,将数据包处理从主机CPU卸载到Azure SmartNIC。在基于软件的VFP主机SDN平台和Catapult的硬件和软件基础设施上,AccelNet提供了专用硬件的性能,以及在虚拟机监控程序中运行的软件的可编程性。

通用流表卸载GFT

AccelNet的目标是找到一种使VFP的复杂策略与SR-IOV兼容的方法。在VFP中用于在SR-IOV环境中实施策略和过滤的机制称为通用流表(GFT)。GFT是一种匹配操作语言,它为一个特定的网络流定义数据包的转换和控制操作。从概念上讲,GFT由一个大表组成,该表为主机上的每个活动网络流都有一个条目。GFT流是基于VFP统一流(UF)定义来定义的,它匹配一个唯一的源和目标L2/L3/L4元组,可能跨多个封装层,同时还有一个header transposition(HT)操作,指定如何添加/删除/更改头字段。

每当GFT表不包含网络流的条目时(例如当新的网络流启动时),可以将流向量化到主机上运行的VFP软件。然后,VFP处理流的第一个数据包的所有SDN规则,使用实时流操作编译器为每个UF(例如,每个TCP/UDP流)创建有状态的精确匹配规则,并创建包含该流的所有编程策略的复合操作。然后,VFP在GFT表中增加新条目,并传递数据包以进行处理。

一旦在GFT表中增加了新流的操作,每个后续数据包都将由GFT硬件处理,提供SR-IOV的性能优势,但是VFP的软件SDN堆栈具有完整的策略和过滤实施。

FPGA智能网卡专题回顾:

珠穆朗玛1980:软件定义FPGA智能网卡介绍(5):NICA

珠穆朗玛1980:软件定义FPGA智能网卡介绍(4):Corundum

珠穆朗玛1980:软件定义FPGA智能网卡介绍(3):Tonic

珠穆朗玛1980:软件定义FPGA智能网卡介绍(2):Panic

珠穆朗玛1980:软件定义FPGA智能网卡介绍(1):NanoPU

作者:珠穆朗玛2048

来源:https://zhuanlan.zhihu.com/p/360749432更多FPGA智能网卡相关技术干货请关注FPGA加速器技术专栏。