iPIPE

原版见SIGCOMM 2019。

这个专题主要对基于FPGA的智能网卡技术进行介绍,上篇介绍了NanoPU、PANIC、Tonic、Corundum、NICA、AccelNet、FairNIC、Lynx等,这次介绍“Offloading Distributed Applications onto SmartNICs using iPipe”,提出基于Actor的应用开发模型,在Smart NIC上实现应用的卸载。高山留存阅读点滴。

引言

多核SoC(system-on-a-chip)已经出现在数据中心,旨在缓解日益增长的网络带宽和停滞不前的CPU计算能力之间的差距。在过去的两年里,主要的网络硬件供应商发布了不同的SmartNIC产品,如Mellanox的BlueField、Broadcom的Stingray、Marvell(Cavium)的LiquidIO、华为的IN5500和Netronome的Agilio。它们不仅针对协议处理的加速(如Open vSwitch、TCP卸载、流量监控和防火墙),但同时也将一种新的计算基础引入数据中心,以低成本扩展服务器计算能力:SmartNIC通常用简单的微体系结构封装计算核心,使其具有成本效益。

通常,这些智能网卡包括多核处理器(即MIPS/ARM)、板载SRAM/DRAM、数据包处理和域特定加速器以及可编程DMA引擎。不同的组件通过高带宽存储器总线或互连连接。如今,这些SmartNIC大多配备了一个或两个10/25GbE端口,甚至100/200GbE端口。这些计算资源允许主机卸载通用计算(包括复杂的算法和数据结构),而不牺牲性能和程序通用性。

最近有一些研究工作也将网络功能转移到基于FPGA的SmartNIC上(如ClickNP,AzureCloud)。它们采用传统的特定领域加速方法,将大多数应用程序逻辑整合到FPGA可编程逻辑块上。这种方法适用于一类特殊的应用程序,这些应用程序具有足够的并行性、确定性的程序逻辑和规则的数据结构,可以在FPGA上高效地合成。另一方面,针对具有复杂数据结构和算法的分布式应用程序,这些数据结构和算法无法在基于FPGA的SmartNIC上高效实现。

多核SoC SmartNIC

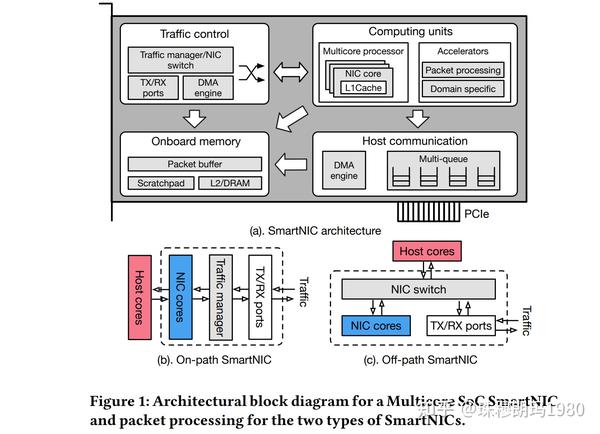

多核SoC SmartNIC由四个主要部分组成:1)计算单元,包括通用ARM/MIPS多核处理器,以及用于数据包处理(如深度数据包检查、数据包缓冲区管理)的加速器和专用功能(如加密/解密、哈希、模式匹配、压缩);2) 板载存储器,包括快速自管理的存储器和较慢的L2/DRAM;3)在TX/RX端口和数据包缓冲区之间传输数据包的流量控制模块,以及将数据包传送到NIC核心的内部流量管理器或NIC交换机;4)用于与主机通信的DMA引擎。

商用多核SoC SmartNIC在性能、可编程性和灵活性方面表现出不同的设计权衡。LiquidIOII智能网卡包含一个OCTEON处理器和一组丰富的加速器,但运行在一个轻量级固件环境中。程序员必须使用本机硬件原语来处理原始数据包、发出DMA命令和触发加速器计算。BlueField和Stingray卡运行ARM Cortex-A72处理器,并拥有一个成熟的操作系统。它们的应用程序开发具有较低的障碍,可以使用传统的Linux/DPDK/RDMA堆栈与本地和外部端点通信。BlueField卡甚至支持NVDIMM容错存储。当前智能网卡通常有10/25GbE的链路速度,100/200GbE的设备开始出现。一般来说,智能网卡比传统网卡贵。例如,一个10/25GbE的SmartNIC通常比相应的标准NIC贵100∼400美元。

根据SmartNIC内核与流量的交互方式,进一步将SmartNIC分为两类:on-path和off-path。on-path SmartNIC的核心位于数据包通信路径上,具有管理每个输入/输出数据包的能力。LiquidIOII CN2350/CN2360都是on-path SmartNIC。off-path SmartNIC根据安装在NIC交换机上的转发规则,将流量传送到主机核心(绕过NIC核心)。Mellanox BlueField和Broadcom Stingray是off-path的。两个NIC供应商都在进一步改进NIC交换机的可编程性(例如,Broadcom TruFlow,Mellanox ASAP2)。

对于这两种类型的SmartNIC,主机处理与标准NIC相同。在传输路径(主机服务器发送通信量的地方)上,主机处理器首先创建DMA控制命令(包括指令头和数据包缓冲区地址),然后将其写入命令环。然后NIC通过DMA引擎从主机内存获取命令和数据,并将其写入数据包缓冲区(位于NIC内存中)。on-path SmartNIC核心接收输入的数据包(通常表示为工作项),执行一些处理,然后通过DMA引擎将它们传送到TX/RX端口。对于off-path,数据包根据交换规则直接转发到NIC核心或TX/RX端口。接收处理(主机服务器从SmartNIC接收流量)类似,但执行顺序相反。

iPIPE编程模型和API

iPipe应用了Actor编程模型进行应用开发。iPipe使用基于Actor的模型有两个原因。首先,Actor模型能够自动支持计算异构性和硬件并行性。可以很容易地将Actor执行实例映射到物理计算单元,例如NIC或主机核心。其次,参与者具有定义良好的关联状态,可以在NIC和主机之间动态迁移。此属性允许对SmartNIC的计算能力进行动态控制,并允许系统适应流量工作负载特性。更重要的是,与设计用于支持数据密集型控制轻负载的数据流或管道模型(如Floem)不同,基于参与者的模型可以支持复杂分布式应用程序中出现的控制密集型、不确定性和不规则的通信模式。

Actor是一个计算代理,它根据输入消息的类型执行两种操作:1)触发执行处理程序并操纵其私有状态;2)通过异步发送消息与其他参与者进行交互。Actor不共享记忆。基于以下考虑,选择消息传递作为通信范例:1)NIC和主机之间的通信延迟为微秒级;2)Actor是没有共享状态的独立实体。

每个Actor都有一个与以下字段相关联的结构:1)init\_handler和exec\_handler,用于状态初始化和消息执行;2)private\_state,它可以使用不同的数据类型;3)mailbox是一个多生产者多消费者并发FIFO队列,它用于存储传入的异步消息;4)exec\_lock,用于决定一个Actor是否可以在多个核上执行;5)一些运行时信息,如端口、actor\_id和对actor\_tbl的引用,其中包含其他Actor的通信地址。一个Actor在一个或多个内核上运行,程序员的责任是为在Actor的私有状态上的操作提供并发控制。

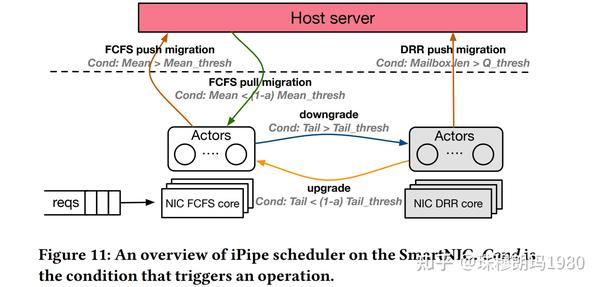

iPipe运行时支持Actor分配/销毁、Actor处理程序的运行时调度以及Actor及其关联状态的透明迁移,从而支持基于Actor的模型。具体来说,iPipe有三个关键的系统组件:1)一个Actor调度器,它跨SmartNIC和主机内核工作,并使用混合FCFS/DRR调度规程来支持具有不同执行成本的Actor处理程序的执行;2) 一种分布式对象抽象,支持灵活的参与者迁移,并支持软件管理的缓存,以降低SmartNIC与主机通信的成本;3)一种安全隔离机制,保护参与者状态免受损坏和拒绝服务攻击。

小结

iPipe为分布式应用程序开发引入了一个Actor编程模型。每个参与者都有自己独立的私有状态,并通过消息与其他参与者进行通信。iPipe提供了一个分布式内存对象抽象,支持actor迁移,响应动态工作负载变化,并确保线速率通信的交付。iPipe的一个核心部分是actor调度器,它结合了FCFS(first come first service)和基于DRR(赤字循环)的处理器共享,允许具有可变执行成本的任务,并最大限度地提高了SmartNIC的资源利用率。iPipe允许来自不同应用程序的多个参与者在SmartNIC上安全共存,防止参与者状态损坏和拒绝服务攻击。总之,iPipe的机制支持对任意应用程序逻辑进行动态和有工作负载意识的卸载,而以前的工作侧重于专门任务的静态卸载(例如Floem和ClickNP)。

FPGA智能网卡专题回顾:

FPGA智能网卡介绍(5):NICA

FPGA智能网卡介绍(4):Corundum

FPGA智能网卡介绍(3):Tonic

FPGA智能网卡介绍(2):Panic

FPGA智能网卡介绍(1):NanoPU

作者:珠穆朗玛2048

来源:https://zhuanlan.zhihu.com/p/363113387更多FPGA智能网卡相关技术干货请关注FPGA加速器技术专栏。