最近各大自媒体都在写ISSCC 2020, 矽说的《后SoC时代或将迎来Chiplet拐点》 尤其好,深入浅出且幽默诙谐。提到Chiplet 许多美满人都不由得感叹,美满前掌门Sehat 多年前就开始关注并投入研究Chiplet, 如今Chiplet 的春天似乎来了,而他老人家却已离开了这一亩田,用一位老兄的话说:起了大早错过了赶集——论成败人生豪迈,有几人可重头再来!

老驴接着《ISSCC 2020: AMD - Chiplets, 把积木玩起来》继续翻译,今天翻译CEA 的积木跟三星和联发科的5G SOC. 在5G 领域我大花厂绝对是走在前列的,可惜今年ISSCC 看不到我花厂了,都说科学技术无国界,别糊弄鬼了,小心上身!

CEA 96 cores Processor

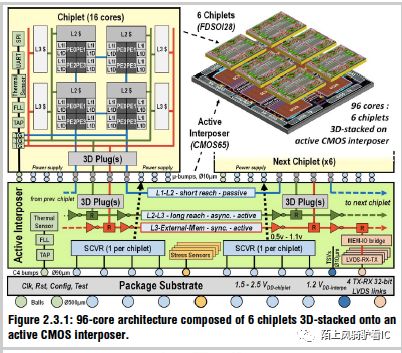

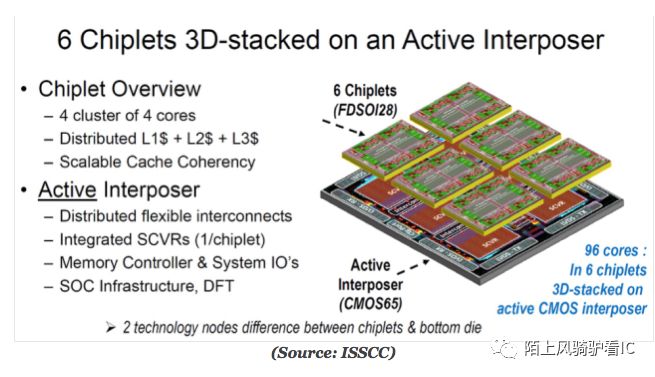

ISSCC 处理器分会场法国研究机构CEA, 同样使用Chiplet 策略搭建了一个96 核处理器,不同于AMD 用专用I/O 芯片来连接多芯片模块,该芯片使用了有源硅中介层,将I/O 逻辑做在中介层中。

Source: ISSCC

该处理器由CEA-Leti 设计,由ST Micro制造,使用6 个Chiplet 构建了96个内核,性能可达220个GOPS ( Giga [billion] Operations Per Second )。 目的是检验用Chiplet 跟有源硅中阶层两种异构芯片搭建处理器这一概念。 尽管此设计使用同构Chiplet, 但将来的设计可以使用异构Chiplet. 与AMD EPYC 设计一样,CEA 的目标是增加处理器的处理能力,而单颗芯片不足以提供所需的处理能力。该处理器的一个应用场景是需要数百个GOPS 的自动驾驶。

使用有源硅中介层,可以把处理器中的一些功能单元用较老的工艺设计实现,如电源管理、内存接口和 I/O. 对于该设计,CEA使用了2D 网格分布式互连。有源硅中介层上的互连有用于短距离的无源通道和用于较长距离的有源通道。 该设计还采用了一种新的异步QDI (Quasi Delay Insensitive) 逻辑与芯片上的异步网络进行通信。

该处理器中,Chiplet 使用具有主体偏置的FDSOI 28nm LPLV 工艺制造,有源硅中阶层使用65nm 工艺制造。虽然该芯片使用较老的工艺,但是展示了如何完成构建和制造。使用传统的known-good-die 技术对Chiplet 进行测试,当所有元件组装好之后再对有源中介层进行测试。 在量产中,如果使用更先进的工艺节点,则制造流程可能会有所不同。

Samsung and MediaTek 7nm 5G SOC

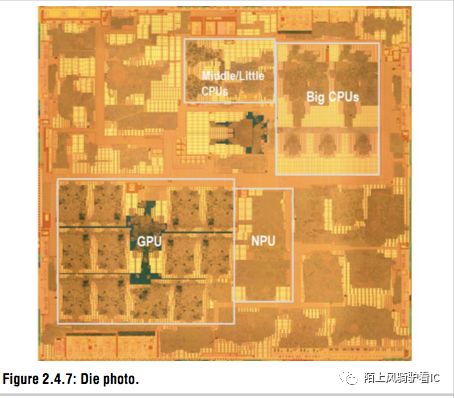

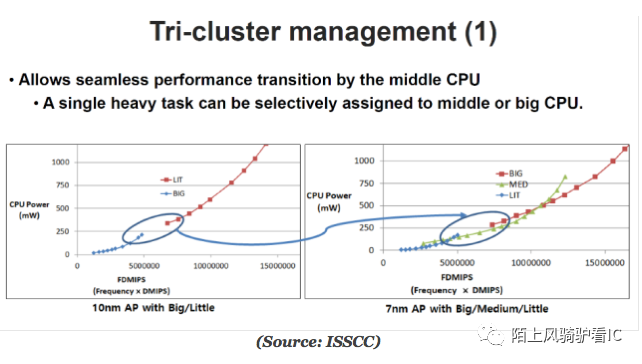

联发科和三星的5G 智能手机SOC, 都聚焦于用不同的Arm 核搭建不同的big.LITTLE 架构及CPU 在重负载下内部IR-Drop 的检测问题。

在三星的5G SOC 中,CPU 核被规划到三个集群中,而不是Arm 传统的双集群 big.LITTLE 架构。三星将Arm 许可的CPU 用于三个集群中的两个,但性能最高的CPU 是由三星根据Arm 的架构许可自己设计的,即两个M4, M4 具有3M 单独的L3 Cache,其性能对标Intel i5.

Source: ISSCC

中核是Arm Cortex-A75, 小核是Cortex-A55, Cortex-A55 与M4 之间的功耗性能差距太大,所以增加了Cortex-A75 以弥合这一差距。该SOC 还集成了一个具有1024 MACs 的神经处理单元。

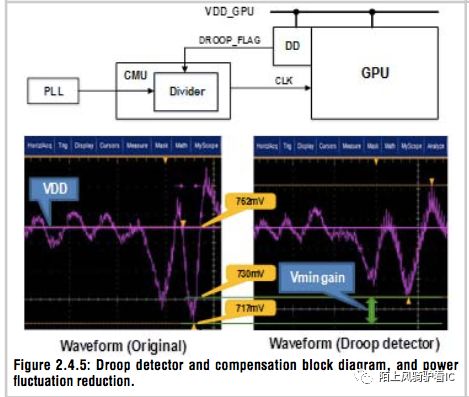

电压降是高性能处理器必须要规避的问题,如果为了保持较高的电源电压添加过多的保护带,则会消耗更多的功耗。在更节能的额定电压下,当某个特别耗电的模块处于重负载状态时(例如运行高分辨率游戏的GPU ),内部压降可能导致内部电压下降到规格以下。 SOC 内通常会有内置专用电路来检测该类压降,并尽量规避该问题。常用的方法是调整时钟频率,通过降低时钟频率来减速电路以减小功耗。三星使用一个环形振荡器电路,该电路会根据电压变化改变速度,振荡器驱动的计数器与阈值进行比较,如果超过阈值,则设置时钟管理单元(CMU)中的标志位,并使时钟频率减半。

Source: ISSCC

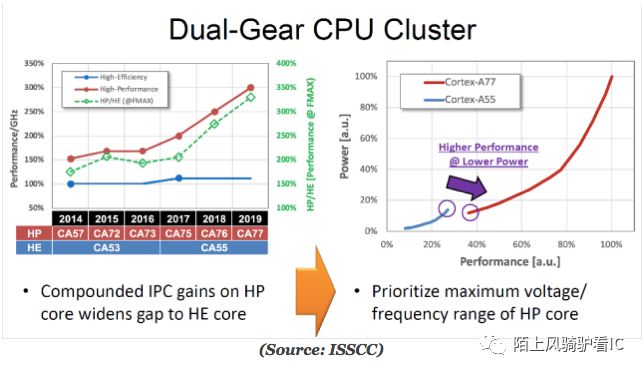

联发科5G SOC 的CPU 架构被称为『双齿轮设计』采用正统的Arm big.LITTLE 方案,大核是Cortex-A77, 小核是Cortex-A55, 为了弥合A55 跟A77 之间的性能差距,联发科并没有添加中核,而是将A77 的工作电压范围进行扩展以支持更低速度。所以三星只有两个高性能M4, 而联发科则有四个A77, 四个A77 和四个A55 内核共享一个2M L3 Cache.

对于电压降联发科最初的设想是在芯片上撒一些存储电荷的电容,做瞬时电流补偿,但这需要额外的面积,所以最后也采用了调整时钟频率的办法。

Source: ISSCC

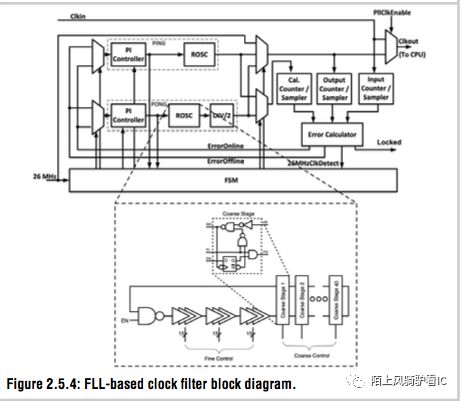

联发科的一大变化是使用了锁频环FLL (frequency locked loop) 而非锁相环PLL (phase locked loop)。 FLL具有双时钟设计,从不丢失时钟周期,但由于其振荡器随电压变化,因此该设计的确定性较低。借助FLL电路,能够将Vmin 提高约35mV, 节省了约10%的功耗。 联发科还用Gateway TAP 为芯片构建了一种新颖的JTAG 解决方案,用于Hierarchical 测试。

Source: ISSCC

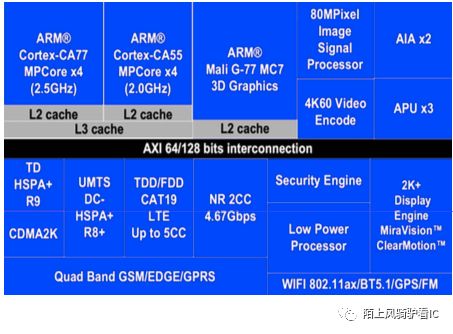

此外,该芯片集成有WiFi-6, 支持5G 独立和非独立模式,CPU 总面积是9.4 平方,A77 频率可达到2.6GHz, GPU是9核Arm Mali G-77。

作者:陌上风骑驴

来源:https://mp.weixin.qq.com/s/8f12jmpe8BfcpqMCyTt9hg

作者微信公众号

相关文章推荐

更多IC设计技术干货请关注IC设计技术专栏。