FPGA开发一种是以verilog等硬件编程语言**设计硬件功能模块状态机,通过编译映射到FPGA资源,另一种是以高级语言描述**业务处理流程,通过高级综合工具HLS等映射到PFGA资源。前者开发复杂,效率高;后者开发简单,效率低。尽管存在多种外围IP核,简化了SoC系统开发,但是用户自己功能开发仍然需要从零开始设计。如FAST硬件开发框架,基于流水线模型提供了UM开发框架,用户功能开发方式并没有改变。针对简化用户逻辑开发,能否进一步抽象FPGA细粒度\_fine-grained\_资源,提供更高级的能够动作重构的功能模块?成为我们关注的重点,粗粒度\_coarse-grained\_重构阵列提供了一种思想。

粗粒度重构阵列CGRA概念

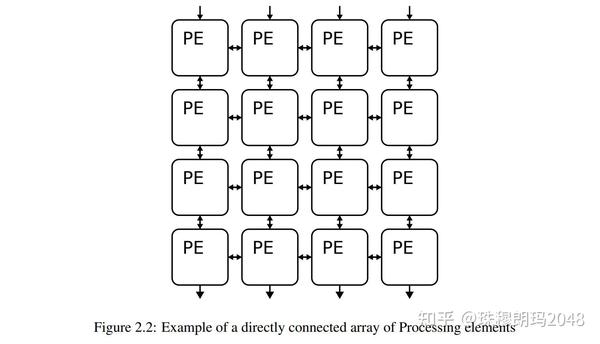

粗粒度可重构阵列CGRA(Coarse Grained Reconfigurable Array)是指由网格方式互连的块矩阵组成的体系结构,可以共同实现各种各样的算法。2D阵列中的每个块执行其操作,并且可以将信息传递给相邻的块,有效地构成可重构的流水线,在每个时钟周期中开始和结束循环的整个迭代。这些模块的复杂程度可以从小型ALU到整个RISC核。具有比这些更简单单元的系统,如门或LUT,被归类为细粒度可重构阵列(FGRA),与FPGA相当。

CGRA体系结构可以根据应用程序采用多种形式。处理单元(PE)的类型和功能在很大程度上依赖于应用程序域。在大多数情况下,PE具有ALU的复杂性,ALU是每个循环执行一个操作的基本模块。每个PE可以有许多附加功能,如内部寄存器、混合操作(如乘法和累加),甚至可以作为一个完整的RISC内核,内部程序独立于其他PE运行。支持内部控制流的CGRA允许更复杂的算法。相比之下,具有更简单的PE但具有更高的质量将具有类似的效果,同时在实现更简单的算法时允许更多的自由度。

关键技术:动态重构

每个PE中配置的加载和存储方式是CGRA架构中的另一个可变性来源。每个PE的配置信息可以存储在每个PE内的寄存器中,并在几个周期内加载,以改变每个PE的操作和PE之间的数据流。一些方法在每个PE中加载了几个配置,使得这些配置可以在没有延迟周期的情况下改变,从而允许在执行期间对整个阵列进行动态重新编程。

动态重构,也称为任务的时分映射,包括映射一个任务,使得一个或多个PE的配置随时间而改变。这允许用户实现条件执行的形式,例如,对每个偶数值执行一个操作,对奇数值执行另一个操作。这种类型的配置基础结构需要比静态配置多得多的资源。这尤其会影响控制器,因为它将负责执行这些更改。另一种方法是在每个PE中添加一个子系统,实际上是一个有限状态机,用于控制要使用的配置。

比如,配置被加载到第一列,并随着新配置的出现而传递到下一列。以这种方式链接配置寄存器可以减少系统加载配置的面积和能源成本。这种实现允许一种特殊情况,即每列实现一个循环的迭代,并将该配置传递给下一列。因此,支持动态配置(对于某些任务),而不需要在每个PE中存储多个配置。

关键技术:互连拓扑

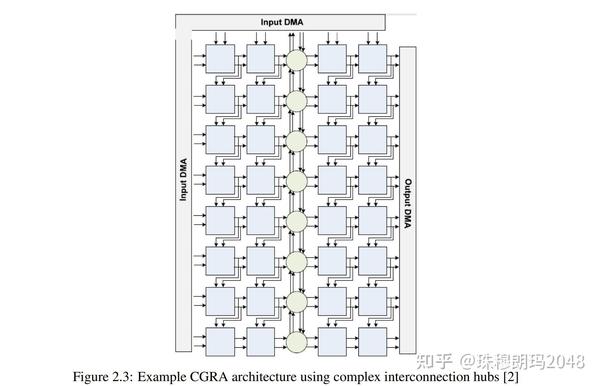

PE之间的互连可以对算法到CGRA的映射施加强大的限制,并且可以表示阵列的功耗和面积的重要部分。更简单的CGRA架构将PE互连在一个网状结构中,每个PE连接到它的近邻。扩展连接性以包括距离为2(2跳)的所有PE可以使应用程序的映射更加简单。有些方法连接每一行或每一列的所有元素,有些方法在每一行或每一列之间使用总线,甚至包括复杂的互连网络,这些互连网络可以跨阵列连接PE。

一般来说,互连密度对到CGRA的映射算法施加了限制,另一方面,对功耗敏感的应用程序必须考虑复杂互连基础设施将消耗的能源量和面积。阵列的拓扑结构不一定是同质的,这取决于应用程序。

关键技术:PE和加速模块

很少使用的操作可能仅限于PE中最有用的部分。诸如浮点单元之类的功能单元消耗大量的面积,并且只能添加到特定的单元中,从而大大减少了面积,同时仍然允许使用需要硬件浮点计算的算法。

诸如浮点单元或除法器之类的模块可以实现为阵列网络之外的附加模块,并允许许多PE访问它。如果模块是流水线的,并且允许每个PE像具有相应的功能单元一样工作,那么这尤其有益。这种方法要求对这些模块的PE访问进行静态调度。其他方法将多个单元组合成更复杂的模块。如可以将每2个PE组合成一个浮点单元。组合单元使用第一个PE计算尾数,另一个PE计算指数,在6或8个周期内执行浮点运算。也可以将2个PE以及一些附加逻辑用于形成超长指令字处理器(VLIW),因此在不处于CGRA模式时不需要主处理器,从而允许整个工作负载在同一硬件上运行。

小结

针对上述关键技术,设计了面向网络分组处理的可重构流水线RMT。

作者:珠穆朗玛2048

来源:https://zhuanlan.zhihu.com/p/365291995更多FPGA智能网卡相关技术干货请关注FPGA加速器技术专栏。