不经一番寒彻骨,怎得梅花扑鼻香。

-- 黄櫱禅师

按照惯例,先讲基础原理,再说ARM的相关部分。

今天要说的这个是存储一致性(memory consistency),不要跟前面讲过缓存一致性(cache coherence)混淆了。缓存一致性协议解决的是对单个存储器地址的访问之间如何排序的问题,而对于不同地址的访问并不是缓存一致性协议所要考虑的问题。存储一致性问题在任何具有或不具有高速缓存的系统中都存在,虽然高速缓存的存在有可能进一步加剧存储一致性问题。

存储器模型(memory model)又称为存储一致性模型。用于定义系统中对存储器访问需要遵守的原则,只要软件和硬件都遵循该原则,就能保证多核程序能运行得到确切的结果。

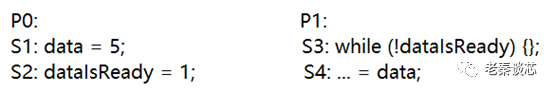

对于程序员来说,通常直觉上会隐式地假定存储器操作是按一定次序的。来看下面的例子,假定有两个线程P0和P1。

在线程P0中,执行S1,赋值data为5;执行S2,赋值dataIsReady为1。在线程P1中,等待dataIsReady这个变量变为1,然后把data赋值给其它变量。在我们直观看来,S1先于S2执行,通过dataIsReady来阻塞P1的S3执行,那么执行S4的时候,拿到的data一定是5。实际上,未必是这样,可能S2的结果早于S1传播到P1,S4拿到的data就有可能是旧值,而不是5!

在我们的直观感觉里,对于变量的写操作会即时传播,或者说是原子性的,即P0的写操作必须以不能分割的步骤传播到P1。我们把关于存储器访问次序的隐式期望表示为:来自一个处理器的存储器访问应该以程序的次序执行,并且每个访问的执行必须是原子性的。这样一种期望被正式定义为顺序一致性(SC)模型。顺序一致性模型虽然能严格的解决存储访问次序问题,但是由于过于严厉,会产生巨大的性能开销。因为当某一个写入操作未执行完,其它的操作可能会全部暂停下来。所以现在大部分处理器都不会实现顺序一致性,而是实现一些较为松弛的一致性模型。

下面将根据从强到弱的限制程度排序,列举几种典型的存储器模型:

1. 顺序一致性模型(sequential consistency,SC)

也称为强定序模型,从施加的限制来看,该模型下load/store是顺序的访问存储器。每个处理器都按照程序顺序来执行程序,即便访问的是不同存储器地址,也不能改变访问顺序。从全局看,每个存储器写操作都需要能被系统中所有的处理器同时观测到,同一时刻只有一个处理器和存储系统相连,因此对memory的访问时原子化的,串行化的。顺序一致性模型简单直观,但限制了CPU硬件和编译器的优化,影响了整个系统的性能。

2. 完全存储定序模型(Total Store Order,TSO)

由于处理器主频和存储器频率相差较大,系统设计人员通常会在CPU中增加存储缓冲区(store buffer),它的作用是为store指令提供缓冲,使得处理器不用等待存储器的响应。但是由于存储缓冲的存在,一些在store之后的load指令可能会越过该指令提前执行,那一个core的store-load操作通常会被其他core看成乱序执行了,变成load-store了。因此在在该模型下,访存操作的四种组合store-store,store-load,load-store,load-load中,只有store-load存在乱序。store操作在store\_buffer中顺序执行。load同样按顺序执行,但可穿插到多个store执行过程中

3. 部分存储定序模型(Part Store Order,PSO)

系统设计人员并不满足TSO模型带来的性能提升,于是继续在TSO的基础上放松访问内存访问限制,允许处理器以非FIFO来处理store buffer缓冲区的指令,处理器只保证地址相关指令在store buffer中以FIFO的形式进行处理,而其它的则可以乱序处理。

4. 处理器一致性模型(Processor Consistency,PC)

该模型比顺序一致性弱。在SC中,要维持每一条load/store指令与后续load/store指令的次序。在处理器一致性模型中,则放松了较早的store指令和较晚的load指令之间的次序。当一条store指令还未被执行时,允许一条较晚的load指令像高速缓存发出请求甚至结束。这一点的重要性在于,store指令可以在写缓冲区排队并在稍晚执行,同时,load指令不需要等待较早的store指令结束就可以访问高速缓存,所以降低了load指令的时延。

5. 弱序一致性模型(Weak Order Consistency,WO)

该模型的主要思想是把同步操作和普通访存操作区分开来,两个同步操作之间的访存操作的顺序不受影响,依然遵循指令程序顺序。WO模型利用了两个假设:程序是适当同步的;程序员正确的向硬件表示哪些load和store是起到同步访问作用的。程序员必须用硬件可识别的同步操作把对可写共享单元的访问保护起来,以保证多个处理器对该共享单元的访问是互斥的。该模型增加了程序员的负担,但能有效提高性能。目前,很多的商业化处理器实现的就是WO,比如ARM。

6. 释放一致性模型(Release Consistency,RC)

该模型是对弱一致性模型的改进,它把同步操作进一步分成获取操作(acquire)和释放操作(release)。acquire用于获取对某些共享存储单元的独占性访问权;release用于释放该访问权。执行的顺序为:acquire-> load/store ->release。与WO类似,RC允许编译器自由改变load指令和store指令的次序,但是不允许它们越过一个获取同步向前移动,也不允许它们越过一个释放同步向后移动。与WO不同的是,单靠指令的操作码不容易表示同步访问。

通常来说,存储一致性模型对访存事件次序施加的限制越弱,越有利于提高性能,但增加了编程难度。且限制越强的存储器模型程序可以在限制较弱的存储器模型上运行,很少会导致错误。

关于存储器一致性模型,有很多的学术文章和书籍,我所了解的也就是一点皮毛。其实,今天讲的这些,都是基础知识。我们下周重点看一下WO,以及ARM的有关内容。

作者:老秦谈芯

来源:https://mp.weixin.qq.com/s/cJ0sbjlMaDX7JXxBzWGD4g

作者微信公众号

相关文章推荐

欢迎大家点赞留言,更多Arm技术文章动态请关注极术社区Arm技术专栏。