耐心是一切聪明才智的基础。

-- 柏拉图

书接上回。ARMv8-A采用的是weakly ordered model。也就是说内存的真实访问顺序和程序的load/strore操作顺序并不完全一致。WO比SC松弛的多,编译器可以自由的改变load和store指令的次序,只要它们不跨越同步边界。在执行过程中,只要同步访问之间的次序得到保证,load和store指令的执行就可以改变次序或相互叠加,无需原子性的执行这些指令。WO比SC能提供更好的性能,但是,其代价必须是向硬件适当地标识和表示同步访问。

我们来看一下ARM为此做了什么。对于存储属性,ARM有如下定义:

- Cacheability:对于cacheable的存储位置,其数据可以放入cache内缓存;而对于non-cacheable,就不可以放入高速缓存了。

- Shareability:对于shareable的区域,意味着这块区域可以被多个处理器共享,也就是说需要有硬件保证访问这块区域的处理器之间保持一致性。

Armv8提供以下两种互斥的存储类型:

1. Normal memory

这种类型通常用于大容量内存操作,包括读/写和只读操作,一般指的是RAM,ROM这些。Normal memory可以通过weakly ordered来提高性能,并且编译器也能做更深层次的优化工作。为了提高性能,应用程序和数据总是被标记为Normal类型。但如果需要严格的存储器访问顺序,那需要用barrier操作来保障。

Normal memory类型具有以下属性:

- 对具有Normal属性的内存位置的写入在有限时间内完成。

- 对于Inner和Outer可缓存而言,对normal类型(non-cacheable或write-through cacheable)的内存位置的写入必须在有限时间内到达内存系统中该位置的端点。两次写入同一位置,其中至少有一次使用normal类型,那么两次写操作可以到达终结点之前被合并,除非两次写入之间存在排序关系。

- 如果系统配置为生成未对齐的内存访问,则未对齐的内存访问可以访问正常内存。

- 处理器以外的内存系统不需要能够识别多寄存器加载/存储指令访问的元素。

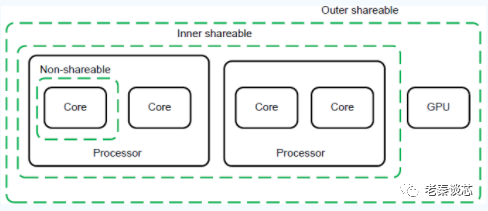

一般对于处理器来说,要指明缓存一致性实现在哪一层次的cache。在ARM中,可以通过innerdomain和outer domain属性。对于具有shareable属性的normal memory区域来说,会是下面几种情况之一:

- Inner shareable,意味着它适用于整个内部可共享域。这表示该domain内的处理器之间可以相互share数据。一个系统可以有多个inner shareable domains,并且当某个操作影响到其中一个innershareable domain时,它并不会影响到其它的inner shareable domain。

- Outer shareable,意味着它适用于内部可共享和外部可共享域。一个outer shareable domain可以由一个或多个innershareable domain组成,并且当一个操作影响到outer shareable domain时,也会影响到其下所有的inner shareable domain。

- Non-shareable,表示相关区域只能给指定的处理器访问。

- Full System,包含全部处理器。

图1 inner和outer shareable domain

上图的Full system可以理解为全局,即一个操作的影响会带给整个系统。

2. Device memory

ARM架构中禁止对Device memory进行任何推测性读取(speculative read)。Device memory一般就是外设的存储区域,对这些区域的读/写操作本应该更加严格。Device memory适用于读取敏感的位置(location)。在标记为Device memory区域运行代码的后果是不可预测的,可能导致取指令失败,也可能是权限错误。

Device memory又分为以下四种

- Device-nGnRnE

- Device-nGnRE

- Device-nGRE

- Device-GRE

其中的G代表的是gathering,nG就是non-Gathering。如果具有gathering属性,那么:

- 同一类型的多个存储访问(读或写)到同一个位置,可以合并到一个事务中。

- 同一类型的多个存储器访问(读或写),访问不同的位置,可以合并到互连网络上的单个内存事务中。

R代表的是Reordering,nR就是non-Reordering。如果具有reordering属性,那么对该区域的访问顺序可以重新排列,规则同访问Normal non-cacheable的重排规则一样。有一点需要注意,nR区域的大小是根据处理器的实现来决定的。

E代表的是Early Write Acknowledgement。在ARM的体系结构中,对于处理器的写操作,需要存储器的端点(endpoint)发出一个确认(acknowledgement)才能认为写操作完成。如果存储区域具有E属性,那么处理器写的内容缓存在某些地方时就可以得到一个确认,然后进行后续操作,不必等到真的写入外设,但是要保证两点:

- 只有写访问的端点返回访问的写确认。

- 存储系统中的任何较早点都不会返回写确认。

可以看出,对于上面的四种device memory来说,从上到下越来越严格。

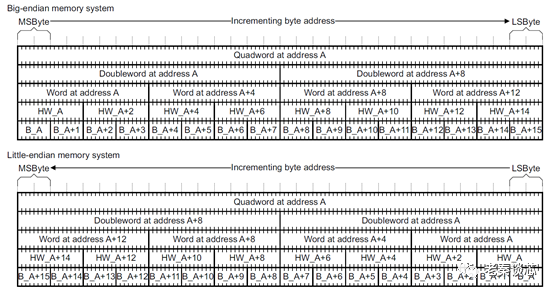

最后再提一点。对于数据在内存中的存储顺序,有大小端之分。大端模式(Big-endian),是指数据的高字节,保存在内存的低地址中,而数据的低字节,保存在内存的高地址中,这样的存储模式有点儿类似于把数据当作字符串顺序处理,地址由小向大增加,而数据从高位往低位放。小端模式(Little-endian),是指数据的高字节保存在内存的高地址中,而数据的低字节保存在内存的低地址中,这种存储模式将地址的高低和数据位权有效地结合起来,高地址部分权值高,低地址部分权值低,和我们的逻辑方法一致。

图2 大端和小端

作者:老秦谈芯

来源:https://mp.weixin.qq.com/s/3LWyQddaolMlPhwnYkiSjA

作者微信公众号

相关文章推荐

欢迎大家点赞留言,更多Arm技术文章动态请关注极术社区Arm技术专栏。