永远要记得,成功的决心远胜于任何东西

-- 亚伯拉罕·林肯

上期讲的多电压域设计主要还是解决的动态功耗问题,今天来看一种降低静态功耗的方法—电源门控(power gating)。当芯片内部的模块/IP不工作时,即使我们把时钟关掉,输入端全部隔离,模块/IP的漏电还是会一直存在的。对于一些手持或功耗非常敏感的设备,这些不必要的静态功耗还是能省就省。最好的做法就是把不工作的模块/IP的电源关掉,等需要工作时再加电。

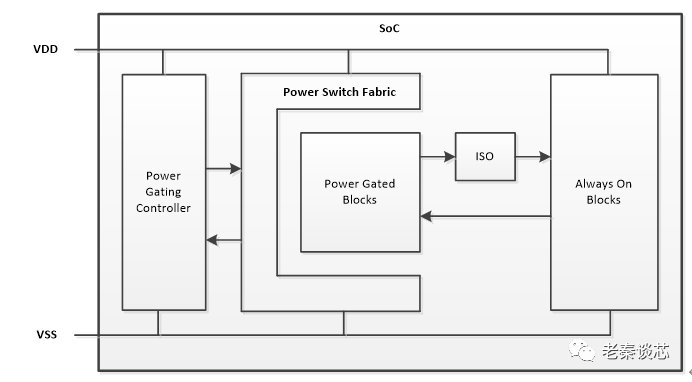

图1 SoC电源门控开关设计示意图

电源门控设计要面对的几个挑战如下,后面进行概念性介绍:

- 电源门控的逻辑设计

- 门控开关的组织结构

- Isolation和retention

- 时钟和复位信号

- 不同power state下的功能验证

- 减少电源门控对时序和面积的影响

- DFT设计,要保证门控开关,isolation和retention的控制逻辑可测

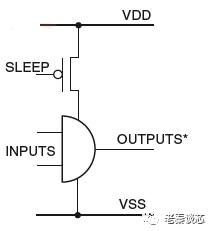

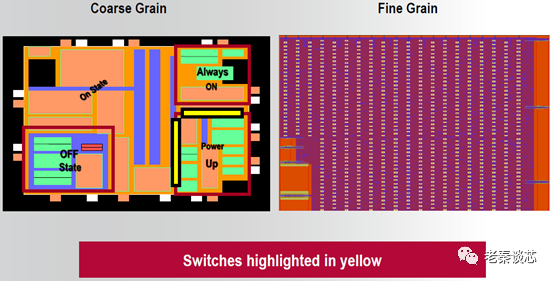

如何去控制功耗开关,分为两种:细粒度(fine grain)和粗粒度(coarse grain)。简单说,细粒度就是每个标准单元内部带电源开关(单元尺寸比正常情况大不少);粗粒度就是所有标准单元被一组开关所控制。能想象出,细粒度这种方法对面积的影响会非常大。

图2 fine grain单元

图3 Fine grain和Coarse grain设计对比

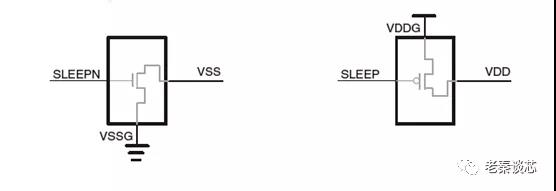

对于电源控制,通常有两种办法,一种是控制VDD,另一种是控制VSS。只要关闭其一即可。所以电源开关的类型就分为两种,header和footer,如下图所示:

图4 footer和header开关示意图

一般通常采用高阈值的管子做开关管,来降低泄露功耗。为了降低模块/IP上电时产生的电源噪声(IR drop),必须要控制上电时的电流(rush current)不能太大。合理的做法就是让模块/IP内部的所有标准单元依次加电,而不是同时加电,所以一般采用daisy chain的方式连接电源开关,也就是前一个电源开关打开后会有一个输出,连到后一个电源开关的控制输入端,以此类推,把所有的开关串成一条链。细心的同学可能要问了,那么最原始的输入控制信号从哪里来呢?这就是前端工程师要做的工作了,还记得图一中的power gating controller吗?前端工程师要根据实际需求来决定在某种工作场景下,哪些模块可以关电,哪些模块必须工作。

前端工程师还要做的一个工作就是确保功能上的正确性,包括以下几个方面。首先是,如何处理下电模块/IP的输出信号,使其不会影响电源常开模块/IP的工作。这里面要用的一种特殊的标准单元,isolation cell。顾名思义,就是把下电模块的信号隔离。当模块/IP下电了,把其输出信号按照功能需要固定(clamp)在高电平或者低电平。至于说具体信号是应该高还是低,后端工程师并不关心,必须是前端工程师来定。而且isolation不同于上篇提到的level shifter(虽然可能合并成一个cell了),必须通过仿真来验证clamp的值是否正确。而且在处理这个逻辑的时候,前端工程师还要保证不会产生glitch。再有一点,一定要注意不要在可关电的模块内产生时钟给其它模块用,否则会对整个时钟树和时序带来巨大的麻烦。

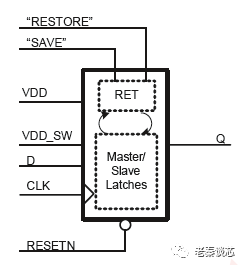

还有一个有关逻辑设计的地方是,模块/IP内部的某些寄存器值在下电以后是不是要保留,以待下次上电时使用。如果每次上电都可以当作一次冷启动,那么就不需要保留上次的状态,否则就需要。另一种特殊标准单元闪亮登场,retention寄存器,如下图所示。这个寄存器需要有两个电源,一个是常开的VDD,给shadow寄存器用,另一个是可以关断的VDD\_SW,给主寄存器用。在需要保留状态时,使能SAVE信号,主寄存器的值就被保留到shadow寄存器中,然后即使VDD\_SW关闭了,shadow寄存器的值也会保留。当模块/IP再次上电,通过使能RESTORE信号,就可以把shadow寄存器的值写回主寄存器中。Retention寄存器除了下图的形式,还有其它形式,但是原理是一样的。至于哪些寄存器需要保留状态,是全模块的寄存器全部保留还是只保留部分即可,这是与功能相关的,需要前端工程师来定。

图5 Retention寄存器

以上提到的isolation和retention并不需要前端工程师在RTL中实现,但是要把功耗设计意图(power intent)告诉给EDA工具,这样工具才能帮助我们完成这个工作。传递功耗设计意图的工作,是通过撰写UPF(Unified Power Format)文件来完成的。

总结一下,当一个模块/IP需要下电,建议功耗控制器按下面的步骤完成相关逻辑操作:

- 结束模块的所有功能事务或操作

- 关闭模块的时钟信号

- 使能isolation控制,固定模块的输出值

- 使能retention的SAVE,把需要保留的寄存器放入shadow中

- 使能reset,初始化模块内部逻辑

- 使能power switch的控制端,关闭模块的电源

对于上电过程,基本就是下电过程反过来。

对于后端工程师,要考虑的问题也很多,比如电源网络的设计,电源开关和isolation的选型和摆放,时序检查,DFT设计等等。电源网络设计好理解,常开和可关断的电源必须是不同的网络。也正是因为分开,布线的资源占用的就多了。

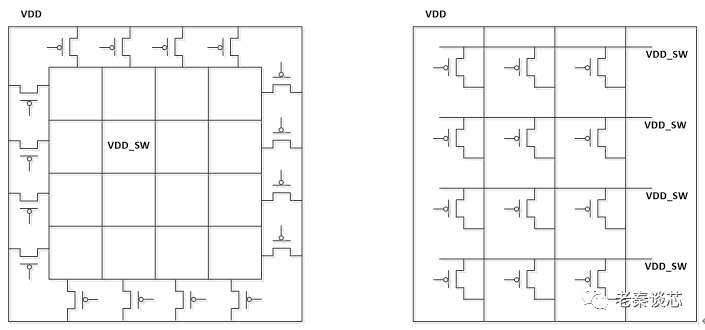

现在大多数设计都是用的coarse gain方式,如何组织这些电源开关也是一个难题,既要考虑面积影响,也要考虑电流影响。如果是自己做物理实现,设计自由度相对大一些。如果是硬核的模块/IP,只能围绕模块周边加电源开关,对于控制面积和IR drop都有一定挑战。

图6 电源开关的ring stayle(左)和grid style(右)

再拿isolation来说,放在source端还是destination端。如果可关电模块的信号要输出给很多其它模块用,isolation摆放在source端可能更合理一点,因为如果放在destination端就要在每个用到这个信号的模块内都实现isolation;isolation放在source端带来的一个潜在问题是,可关电的模块内部要给isolation提供常开电源。所以具体情况还是要结合具体设计需求做trade-off,不能一概而论。

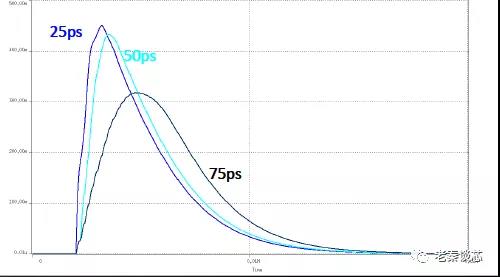

在做IR drop检查时,要考虑模块上电场景,必须保证上电过程时的电流变化不会过大过快,以免造成比较大的电源噪声,影响常开电源域的工作。控制上电过快的方法有很多,一种常见的做法是在电源开关的chain中加buffer。

图7 不同的rush current情况

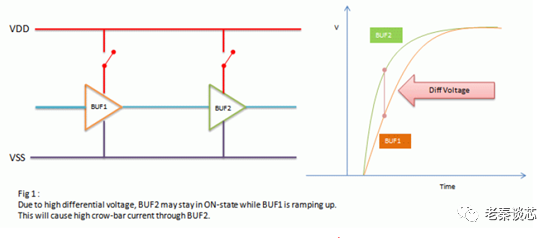

考虑到电源开关往往是串成daisy chain,还要做一个额外的differential voltage检查,如下图所示。如果BUF2先于BUF1完成了上电,BUF1在上电时BUF2会造成瞬态开路电流,严重时会影响后面电路正常工作。

图8 differential voltage检查

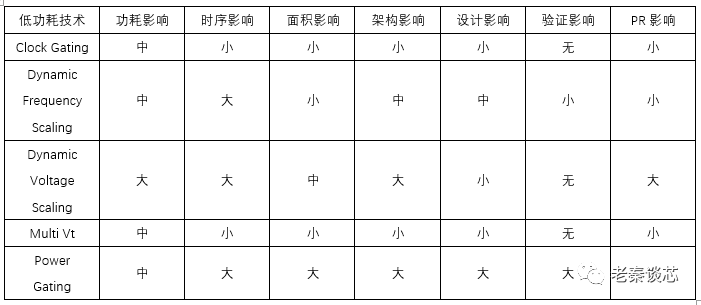

实际项目中,要考虑的地方肯定不止上面提到的这些,还有DFT,STA等许多方面。最后还是总结一下各种低功耗技术的收益和影响,作为一个简单的参考。

SoC功耗系列就先写这么多吧,后面还是想写一些自己更感兴趣的话题。其实,SoC功耗系列至少还缺一个UPF介绍和低功耗验证介绍,先留着这几个坑吧。

表1 低功耗技术总结

作者:老秦谈芯

来源:https://mp.weixin.qq.com/s/9zBpEKI7VfqubpOiphtrsw

作者微信公众号

相关文章推荐

更多IC设计技术干货请关注IC设计技术专栏。