不管什么问题,都必然存在着答案。

-- 东野圭吾

有朋友后台留言,觉得ACE有点跳跃,希望讲一下AXI。

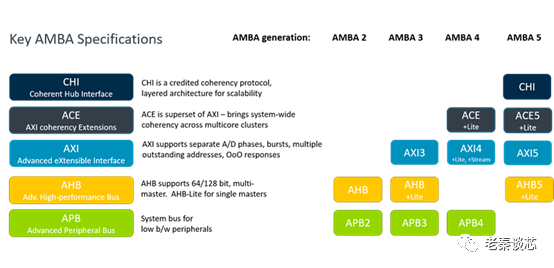

开始之前,先上图,看看AMBA的演进过程。目前最新版本是AXI5,5和4的差别不大,所以下文以3和4为主。

AXI的全称是Advanced eXtensible Interface。在spec里面是这么自夸的:

- 用于高带宽和低延迟设计。

- 提供高频操作,无需使用复杂电桥。

- 协议满足各种组件的接口要求。

- 适用于具有高初始访问延迟的内存控制器。

- 提供了实现互连架构的灵活性。

- 与AHB和APB接口向后兼容

AXI有五个独立的事务通道,分别是:

- 读地址(Read Address,简称AR)

- 读数据(Read Data,简称R)

- 写地址(Write Address,简称AW)

- 写数据(Write Data,简称W)

- 写响应(Write response,简称B)

AXI的五个通道是单方向的,这样做的好处是可以对每个通道单独优化,而且当经过复杂的片上网络时,能够优化时序减少延迟。AXI支持突发(burst)传输,乱序(out of order)传输,极大地提高了数据吞吐能力,在满足高性能要求的同时,又减少了功耗。

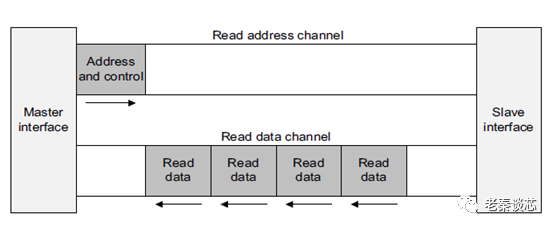

对于读操作,主机(master)通过AR通道发送读事务地址,从设备(slave)通过R通道返回给主机所需要的数据,如下图:

图1 AXI的读操作

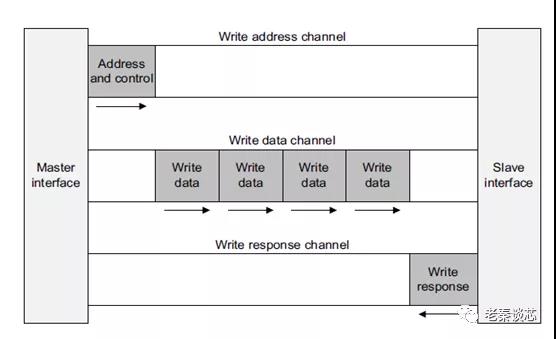

对于写操作,主机通过AW通道发送写事务地址,并通过W通道把数据发送给从设备,而从设备接收到数据后,需要通过B通道返回一个响应给主机,整个过程结束。

图2 AXI的写操作

读和写的不同之处,一是数据方向不一样,还有就是读事务不需要从设备再发响应了,想想为啥涅。

读和写的数据宽度可以是8, 16, 32, 64, 128, 256, 512, 1024 bits中的一种。

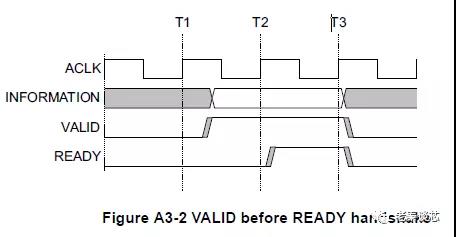

这里不得不提一下AMBA中广泛采用的VALID/READY握手机制。正是因为有了这个机制,发送方(Source)和接收方(Destination)才都有能力控制传输。

发送方通过职位VALID信号,来告诉接收方,自己已经将数据等信息准备好;而接收方通过置位READY信号,来告诉发送方,自己准备好了接收数据。只要有任何一方没准备好,传输就不能进行。

这里不要混淆了,发送方不总是主机,比如读数据通道上,发送方就是从设备,主机是接收方。

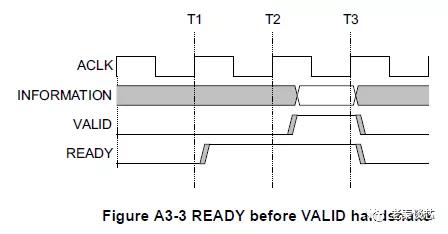

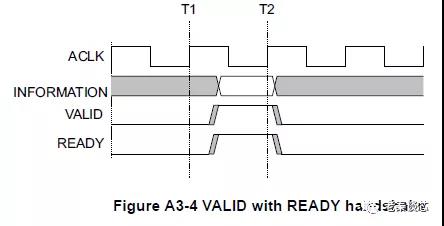

发送方的VALID信号和接收方的READY信号并不需要同时置位,可以发送方先准备好,也可以接收方先准备好。也就是说VALID可以早于READY,也可以晚于READY,也可以同时置位。对应的就是下面三种情况。

但是,为了避免死锁等问题,对于VALID/READY信号还是有一定要求的。协议规定,发送方的VALID信号一旦置位就不能拉低,直到完成一次握手;而且,发送方不能根据接收方的READY信号来置位自己的VALID信号。简单说,就是发送方可以根据自己的需求随时发起传输,不能也不需要判断接收方是否空闲,同时发送方一旦发起传输,就不能随意中止。对于接收方,如果没有准备好接收就可以不置位READY,这样就可以反压发送方的传输了,而且接收方置位READY后,只要发送方没置位VALID,可以拉低READY。

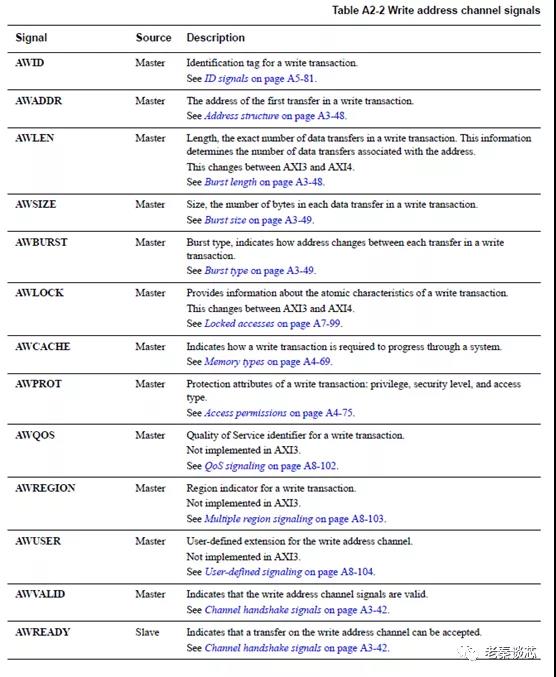

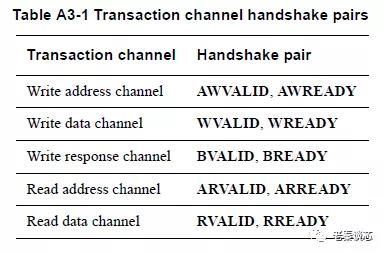

时钟信号和复位信号作为全局信号,没啥好说的。AXI的五个通道的信号如下,先是写地址通道:

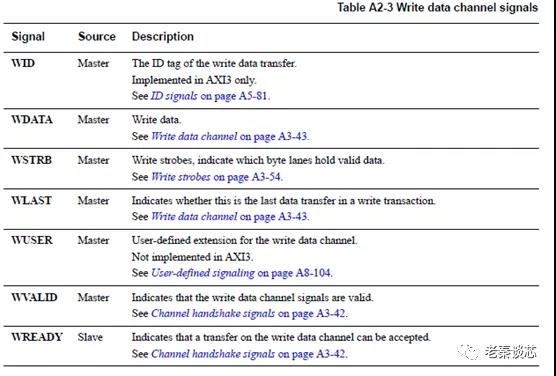

写数据通道:

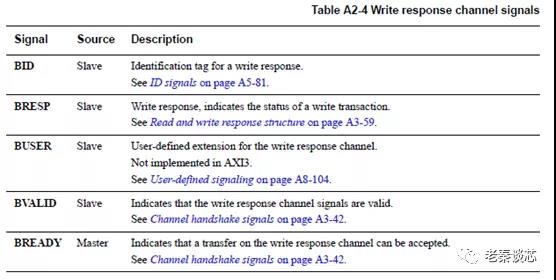

写响应通道:

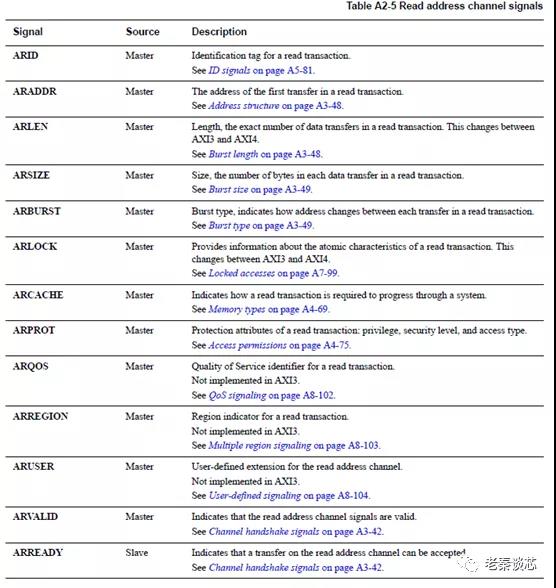

读地址通道:

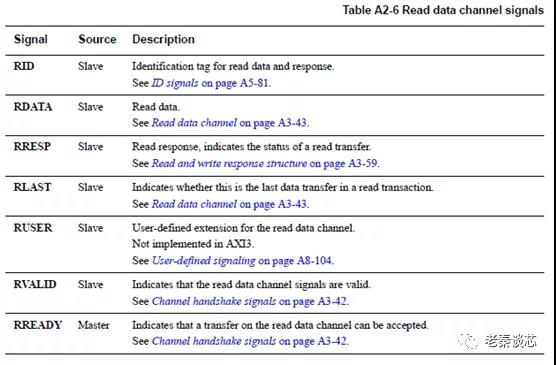

读数据通道:

从上述的信号列表我们可以看出来,每个通道都有自己的VALID/READY信号。这种VALID/READY握手机制在整个AMBA体系里面广泛采用,不管是做设计还是做验证的同学,一点要熟记。

今天内容不多,都是基础,下周来看看具体的信号都是什么含义吧。

【未完,待续】

作者:老秦谈芯

来源:https://mp.weixin.qq.com/s/k8iY4gh4OjMpozR4wMQiyA

相关文章推荐

更多IC设计技术干货请关注IC设计技术专栏。